一套數字音頻采集、播放和傳輸系統的實現

TLV320AIC23簡介

TLV320AIC23(以下簡稱AIC23)是TI推出的一款高性能的立體聲音頻Codec芯片,內置耳機輸出放大器,支持MIC和LINE IN兩種輸入方式(二選一),且對輸入和輸出都具有可編程增益調節。AIC23的模數轉換(ADCs)和數模轉換(DACs)部件高度集成在芯片內部,采用了先進的Sigma-delta過采樣技術,可以在8K到96K的頻率范圍內提供16bit、20bit、24bit和32bit的采樣,ADC和DAC的輸出信噪比分別可以達到90dB和100dB。與此同時,AIC23還具有很低的能耗,回放模式下功率僅為23mW,省電模式下更是小于15uW。由于具有上述優點,使得AIC23是一款非常理想的音頻模擬I/O器件,可以很好的應用在隨聲聽(如CD,MP3……)、錄音機等數字音頻領域。

AIC23的管腳和內部結構框圖如下:

從上圖可以看出,AIC23主要的外圍接口分為以下幾個部分:

一. 數字音頻接口:主要管腳為

BCLK-數字音頻接口時鐘信號(bit時鐘),當AIC23為從模式時(通常情況),該時鐘由DSP產生;AIC23為主模式時,該時鐘由AIC23產生;

LRCIN-數字音頻接口DAC方向的幀信號(I2S模式下word時鐘)

LRCOUT-數字音頻接口ADC方向的幀信號

DIN-數字音頻接口DAC方向的數據輸入

DOUT-數字音頻接口ADC方向的數據輸出

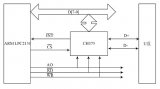

這部分可以和DSP的McBSP(Multi-channel buffered serial port,多通道緩存串口)無縫連接,唯一要注意的地方是McBSP的接收時鐘和AIC23的BCLK都由McBSP的發送時鐘提供,連接示意圖如下:

二. 麥克風輸入接口:主要管腳為

MICBIAS-提供麥克風偏壓,通常是3/4 AVDD

MICIN-麥克風輸入,由AIC結構框圖可以看出放大器默認是5倍增益

連接示意圖如下:

三. LINE IN輸入接口:主要管腳為

LLINEIN-左聲道LINE IN輸入

RLINEIN-右聲道LINE IN輸入

連接示意圖如下:

四. 耳機輸出接口:主要管腳為

LHPOUT-左聲道耳機放大輸出

RHPOUT-右聲道耳機放大輸出

LOUT-左聲道輸出

ROUT-右聲道輸出

從框圖可以看出,LOUT和ROUT沒有經過內部放大器,所以設計中常用LHPOUT和RHPOUT,連接示意圖如下:

五. 配置接口:主要管腳為

SDIN-配置數據輸入

SCLK-配置時鐘

DSP通過該部分配置AIC23的內部寄存器,每個word的前7bit為寄存器地址,后9bit為寄存器內容。具體方法和寄存器具體內容見后。

六. 其他:主要管腳為

MCLK-芯片時鐘輸入(12.288M、11.2896M、18.432M、16.9344M)

VMID-半壓輸入,通常由一個10U和一個0.1U電容并聯接地

MODE-芯片工作模式選擇,Master或者Slave

CS-片選信號(配置時有效)

CLKOUT-時鐘輸出,可以為MCLK或者MCLK/2(詳見寄存器配置)

DSP與AIC23的連接

設計中DSP采用了TI的C5409,這是一款性價比高,外設資源豐富,耗電量低,處理能力強的16位DSP,在實際應用中較為流行。

C5409有三組可通過寄存器靈活配置的McBSP同步串口,與AIC23的連接主要使用這些串口。

一. 與AIC23數字音頻接口的連接

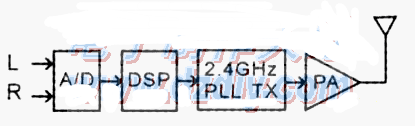

AIC23的數字音頻接口支持I2S模式(一種通用的音頻格式),也支持DSP Mode模式(專為與TI的DSP連接模式)。兩種模式的時序如下圖:

I2S模式

DSP Mode模式

DSP與AIC23的連接可以采用I2S模式也可以采用DSP模式,區別僅在于DSP的McBSP幀信號的寬度。前者的幀信號寬度必須為一個字(16bit)長,而后者的幀寬度可以為一個bit長,比如在字長16bit(即左右聲道的采樣各為16bit),幀長為32bit的情況下,如果采用I2S,幀信號寬度應為16bit;而采用DSP Mode幀信號寬度1bit即可。

為了與AIC23通信,DSP的串口時鐘也應該正確的設置。DSP的McBSP時鐘為了減少外圍電路通常都選擇由內部CPU時鐘分頻得到,比如在AIC23采樣速率為8K的情況下,McBSP串口時鐘應為8×32=256K,這時,DSP工作時鐘/256K=需要設置的分頻因子。

需要注意的是,DSP的串口分頻因子最大為0xff(256),所以如果采用內部時鐘分頻的辦法,DSP工作時鐘不能超過64M。

二.與AIC23配置接口的連接

AIC23的配置接口支持I2C模式,也支持SPI模式。通常比較簡單的辦法是利用DSP的一個McBSP用SPI模式跟AIC23連接。但是有些時候,如果DSP的McBSP串口資源比較緊張(比如需要跟近端RS-232和遠端RS-485連接),也可以通過DSP模擬I2C總線與AIC23連接。下面簡單介紹這兩種方法:

SPI時序圖如下:

這種模式的特點是只在片選信號有效時鎖存進數據。由于也是同步串口,所以通過配置McBSP為Clock Stop Mode(時鐘在幀信號有效時產生,其他時間沒有時鐘信號)可以無縫與之連接。這時,McBSP的幀信號連接SPI的CS信號,時鐘和數據信號與SPI一一對應。這種連接只需設置McBSP的寄存器,使用比較簡單可靠。

I2C時序圖如下:

C5409沒有I2C接口(TI的C5509有),但是可以利用DSP的GPIO(General Purpose Input/Output)來實現I2C時序。C5409有8個HPI(Host Port Interface)管腳可以選擇作為GPIO使用(上電時HPIENA管腳或者HPI16管腳為低),這樣我們可以利用其中的兩個管腳來作為I2C中的SCL和SDA。在I2C中SDA是雙向管腳,而DSP的GPIO的方向要通過寄存器來配置為輸入或者輸出,所以在實現I2C總線時,要經常在需要的時候變換GPIO(作為SDA的那個)的方向。對GPIO的操作是通過寄存器來完成:當設為輸出時,向寄存器寫入要輸出的值;設為輸入時,從該寄存器讀入管腳上的值。

在實現I2C總線時,還需注意下面幾點:作為SDA的那個GPIO應該接上拉電阻;AIC23只可寫不可讀;AIC23的設備地址當CS為低時是0011010b,CS為高時是0011011b。

DSP的軟件設計

DSP需要處理來自和發向AIC23的數據,從而達到采集和播放聲音。

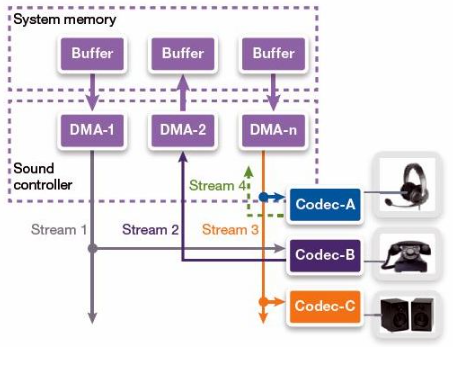

從上面的分析我們知道,這些數據都是通過DSP的McBSP交換的。McBSP可以有三種方式跟CPU通信:每收到或發送一個單元,置標志位,CPU輪詢此標志位;每收到或發送一個單元,給CPU發送中斷;通過DMA收到或發送完一組單元,再給CPU中斷。通常,為了減輕CPU負擔,都采用第三種方法。

采用DMA的方式,即串口每發送或接受到一個單元,都會自動觸發DMA將其搬送到一個內部的Buffer,等Buffer滿了再通過中斷方式告訴CPU處理。這時DMA最好采用ABU(Auto Buffering)模式,在這種模式下,DMA會在兩個Buffer(其實是一個大Buffer的前一半和后一半)之間自動切換,每個Buffer滿了(接收)或空了(發送)都會給CPU發出中斷,在CPU處理這個Buffer的時候,DMA會自動去操作另一個Buffer。采用這種方式可以有效防止Buffer中的數據在串口速率較高時被新數據沖掉的問題。

在DMA的中斷服務程序中為了可靠可以把這個Buffer的數據再拷貝到另一個待處理的空間,即兩級Buffer,然后置標志位,CPU在主程序中查詢標志位然后作出相應的處理。DMA操作的Buffer可以通過寄存器配置,Buffer的大小和起始位置應設置正確。在指定Buffer的起始位置時應該注意,起始位置應該為大于Buffer大小的下一個2的整數冪的倍數。例如,在8K、16bit采樣的情況下,以20ms數據為Buffer大小,那么一次處理的數據是8000×32×0.02=5120bit=320word。所以,DMA的Buffer應為640word(兩個320word Buffer)大小,而Buffer的起始地址應該為1024=2^10>640的整數倍,如0x7000,0x7400……

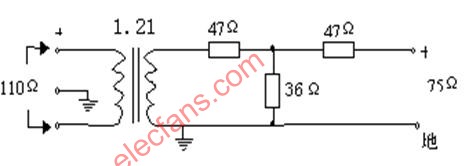

DSP與異步串口間的通信

DSP與PC機交換聲音數據可以通過異步串口實現(近端RS-232或者遠端RS-485再到RS-232)。下面簡單介紹如何利用DSP的McBSP實現RS-232協議從而跟PC機的串口通信。

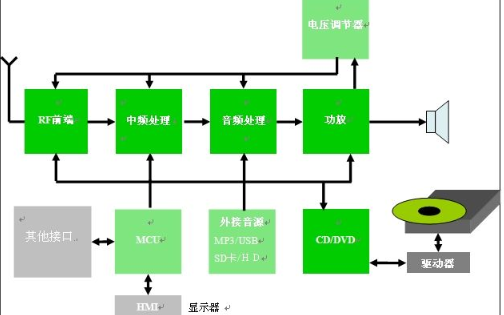

首先,因為McBSP和RS-232電平不同,之間需要加一個MAX232這樣的電壓轉換芯片。同時,DSP的McBSP是一個三線同步串口,而RS-232只需一根數據線(單向)即可通信,所以在實現異步串口時,首先硬件連接應該如下:

從上圖可以看出, McBSP串口的接收幀信號和接收數據線連在一起,這樣做的目的是為了利用異步幀的開始位(低有效)來給McBSP一個幀信號。顯然,這時DSP的幀信號應設置為低有效且接收延時應設置為'1'。

同步-異步轉換的基本原理就是對異步信號過采樣得到同步信號,例如一般是對異步信號的每個bit用同步信號的一個字來表示(即16個'1'-0xffff或16個'0'-0x0000)。可參看下圖(上邊為異步信號,下邊為同步信號):

串口的發送和接收都采用DMA方式,Buffer的大小為:1+8+1(無校驗位,結束位長度為1)=10word。同步-異步具體轉換在軟件上實現:

對于發送來說,較為簡單,就是對每一個Byte的每個bit用一個word(16bit)進行代替,加上開始位、結束位。然后判斷是否可以發送(通過發送完畢標志),如果可以則把這10個word放入Buffer,啟動DMA即可。在發送中斷服務程序中需要作的是停止發送DMA,并置發送完畢標志有效。

接收相對發送麻煩一些,需要對接收到的每一個字進行判斷從而恢復每一個bit,例如可以認為收到0000 1111 1111 0000b為'1',其余為'0'。過濾掉開始位('0')和結束位('1'),恢復的8個bit就合成一個Byte。這些應該在接收中斷服務程序里面做。

還有就是同步串口時鐘的選擇,一定要稍大于設計速度,比如,在跟57.6K的RS-232通信時,時鐘應該為57.6×16=921.6K,實際配置串口分頻寄存器時應該稍大于這個速度,否則就可能由于沒有正確檢測到停止位而出現錯誤。

更詳細的同步-異步轉換設計流程跟我們的主題無關,有很多文章有具體的描述,這里就不主要討論了。

至此,一個較為完整的系統就建立了。此系統可以完成對語音或者音頻信號的采集和播放,同時通過DSP內部的壓縮算法,如g.729或者MP3傳給PC機進行儲存和傳輸。

附錄:

AIC23的內部寄存器中的一些主要設置bit:

1. LINE IN左聲道音量控制寄存器:

LIM:靜音

LIV【4:0】:音量控制

2. LINE IN右聲道音量控制寄存器:

RIM:靜音

RIV【4:0】:音量控制

3. 耳機左聲道音量控制寄存器:

LHV【6:0】:音量控制

4. 耳機右聲道音量控制寄存器:

RHV【6:0】:音量控制

5. 模擬通道控制寄存器

BYP:Bypass模式

INSEL:ADC輸入選擇,0-LINE IN、1-麥克風

MICM:麥克風靜音

6. 數字通道控制寄存器

DACM:DAC靜音

ADCHP:ADC高通濾波器開關選擇

7. 省電控制寄存器

OFF:Device Power off

CLK:Clock Power off

OSC:Oscillator Power off

OUT:Outputs Power off

DAC:DAC Power off

ADC:ADC Power off

MIC:MIC Power off

LINE:LINE IN Power off

8. 數字接口格式寄存器:

MS:工作模式Master or Slave

LRSWAP:DAC左右聲道交換

LRP:I2S模式下,LRCIN低左聲道或右聲道

?????DSP模式下,MSB在LRCIN有效后1st或者2nd BCLK沿出現

IWL【1:0】:采樣Bit長度

FOR【1:0】:DSP格式,即幀信號后跟左右聲道兩個字

I2S格式,幀信號占空比50%,高低各是左右聲道

9. 采樣率寄存器:

CLKIN:時鐘輸入選擇,0-MCLK,1-MCLK/2

CLKOUT:時鐘輸出選擇,0-MCLK,1-MCLK/2

10. 數字接口激活寄存器:

ACT:激活開關

11. Reset寄存器

RES:寫入0重啟

電子發燒友App

電子發燒友App

評論