利用集成式接收器簡化數字預失真電路模擬部分

數字處理電源領域的巨大進步引發了對高性能模擬產品的更大需求。除傳統語音外,如今的蜂窩網絡還能夠以前所未有的高速率傳輸重要的數據和視頻信息,這催生了新的調制方法和依賴于復雜數字技術的新型空中接口標準。盡管數字技術使系統能夠在采用更小封裝尺寸且具有更高可靠性的情況下運行更快速、消耗功率更少,但是它們也對整個系統的RF和模擬信號采集部分提出了新的要求。

調制的復雜度以及基站發送器的寬帶寬,導致功率放大器(PA)有更高的峰均比。為了滿足較高峰均比存在下更嚴格的要求,PA一般尺寸很大,能夠在線性區工作。如果沒有數字校正,PA的效率可能在 10% 左右,這意味著要運行一個20W的PA需要200W功率。在基站中,PA消耗的電功率最大,因此就蜂窩服務供應商而言,PA對運營成本的影響也很大。為了提高PA效率,需要采用數字技術實現振幅因數降低(CFR)和數字預失真(DPD) 。

盡管驅動放大器進入飽和狀態時放大器的效率最高,但是在飽和狀態,放大器是高度非線性的。復雜的數字調制需要PA提供極高的線性度,這意味著必須驅動PA遠離飽和狀態。如果有辦法補償放大器固有的非線性,那么讓PA恰好在即將進入飽和狀態時工作,可以提供高效率。目前,DPD已經成為PA線性化的首選方法。

DPD是一種反饋方法,可以對PA的輸出進行采樣并將其轉換為數字數據。將一個存儲在FIFO中的無失真發送信號與反饋信號進行比較,并產生一個反傳遞函數。在CFR之后,將其與發送數據相加,以降低PA輸出中的非線性。可以使用自適應算法或查找表來產生補償數字信號,或結合使用這兩種方法,但是這超出了本文討論的范圍。下面,我們將集中討論對PA輸出采樣的接收器的模擬要求。

對數字預失真接收器的要求

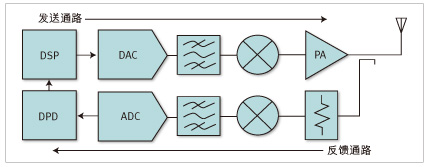

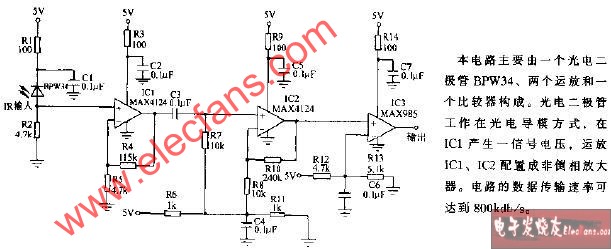

該接收器是從 RF向數字化(參見圖1)轉換的信號鏈路。關鍵的設計要求是輸入頻率范圍和功率級、中頻以及將被數字化的帶寬。這些要求中,有些直接來自PA規格,有些則是在設計時優化得到的。

圖 1:數字預失真信號鏈路

基帶發送信號上變頻至載波頻率,該信號頻率由WCDMA、TD-SCDMA、CDMA2000、LTE等新空中接口標準定義。因此,被采樣的輸出頻譜存在于定義好的頻率范圍(及期望信道)內。既然DPD環路的目的是測量PA的傳遞函數,那么就不必在多載波系統中分離載波,或調制數字數據。唯一必要的,是捕獲有關整個期望信道的信息。

PA非線性會產生奇數階互調分量,在相鄰和相間信道中形成頻譜再生。按照定義,三階分量出現在2fa + fb、2fb + fa、2fa – fb和2fb – fa,其中的fa和fb是位于期望信道之內的兩個信號頻率(在信道外會引起互調失真)。對于一個已調制信道,三階分量出現在期望信道三倍帶寬的范圍(見圖2)。同樣,五階分量出現在五倍帶寬的范圍內,而七階分量則出現在七倍帶寬的范圍內。因此,DPD接收器必須獲得發送帶寬的倍數,該倍數與正在進行線性化處理的互調分量的階次相等。

圖 2:互調分量

目前的發展趨勢是,將期望信道與中頻 (IF) 混合,并獲得所有互調分量的完整帶寬。選擇恰當的IF以減少濾波負擔,避開已經根據規格要求固定了的其它頻率。類似地,選擇整倍于數字調制芯片速率的值為采樣速率,例如,在 WCDMA 中為 3.84MHz。最后,奈奎斯特定理決定,采樣速率必須至少是被采樣帶寬的兩倍。很多配置可以被接受的,其中滿足上述限制的一種配置是:184.32MHz 中頻、245.76MHz ADC 采樣率和122.88MHz 帶寬。

在 20W PA情況下,平均輸出功率是43dBm。峰值/均值(PAR)約為15dBm。為了將進入接收鏈路混頻器的平均輸入功率設置為 -15dBm,耦合器和衰減器合起來的插入損耗必須是 58dB(參考圖 1) 。WCDMA 標準中規定的PA帶內噪聲最大,為 -13dBm/MHz(-73dBm/Hz) 。因此,耦合器、衰減(-58dB)以及PA噪聲限制(-13dBm/MHz)的結合,產生必須低于 -71dBm/MHz (-131dBm/Hz) 的接收器靈敏度等級。為了提供充足的裕度,應該在所期望的數字上再加上 6dB至10dB的裕值。這為DPD接收器設定了頻率計劃、功率級和靈敏度要求。

集成式數字預失真接收器

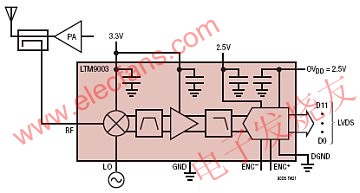

一旦定義了系統要求,接下來的任務就變成了用一個混頻器、IF放大器、ADC、無源濾波、匹配網絡和電源旁路來實現電路。盡管計算和仿真有所幫助,但是其無法取代對真實硬件的評估,硬件評估通常會一次一次反復產生多個PCB。然而,一類新型基于系統級封裝(SiP)的集成式接收器極大簡化了這一任務。例如凌力爾特的LTM9003數字預失真uModule接收器,該產品是一款全集成化DPD接收器,實質上是“射頻到比特流”架構。

由凌力爾特公司倡導的uModule技術利用了一種由雙馬來酰亞胺三嗪(BT)材料制成的薄型多層壓合基底。該多層基底允許采用RF組件、標準引線鍵合IC裸片和傳統的無源元件進行復雜電路設計。電路采用標準IC封裝模塑料進行封裝,而且,LGA焊盤布局也與當前的表面貼裝方法相符。這樣就造就了一個外形與直觀感覺酷似傳統IC的子系統,其經過全面測試,確保了IC的高可靠性,并把采用不同半導體工藝的元件與無源元件結合,與傳統實現方案相比,占位面積更小。

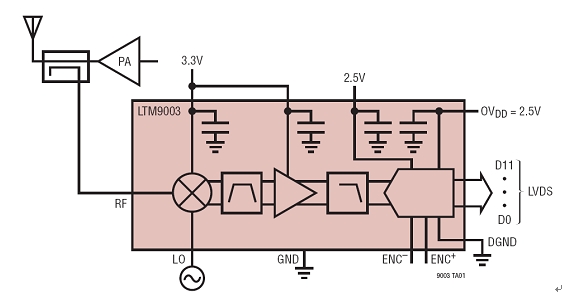

LTM9003由一個高線性度 RF 下變頻混頻器、一個IF 放大器、一個L-C 帶通濾波器和一個高速ADC組成 (參見圖 3) 。導線連接的裸片組裝確保總的外形尺寸高度緊湊,而且還允許基準和電源旁路電容與傳統封裝方法相比更加靠近裸片。這樣做降低了噪聲使ADC精度下降的可能性。該理念擴展到了高頻布局方法中,并在LTM9003接收器鏈路中得到了貫穿使用。

圖 3:LTM9003 集成式數字預失真接收器

集成消除了驅動高速ADC面臨的很多挑戰。線性電路分析無法解決ADC采樣和保持切換動作導致的電流脈沖。傳統電路布局需要多次重復,來定義一個輸入網絡吸收這些脈沖,該網絡在帶外也有吸收性,但是要與前述放大器一起無縫工作。IF放大器還必須在不增加失真的情況下驅動這個網絡。克服這些挑戰也許是LTM9003 μModule接收器潛在的最突出的屬性。

無源帶通濾波器是一個通帶非常平坦的3階濾波器。在中心頻率為25MHz的頻帶內,它呈現了不到 0.1dB的紋波,而且在整個122MHz內,通帶紋波僅為0.5dB。三階配置可確保頻率響應曲線的肩峰部具有單調特性,這一點對于許多DPD算法來說非常重要。

LTM9003的總體性能遠遠超過了上述系統要求。當使用一個-2.5dBm單音信號(相當于在ADC上的-1dBFS),信噪比的典型值為-145dBm/Hz。這個數字低于WCDMA標準定義的-131dBm/Hz目標值。最壞情況下諧波是60dBc。25.7dBm的IIP3數字意味著,如果PA具有足夠的線性,那么LTM9003能夠支持一個 87dBc 的 ACPR。相對于系統要求和可用最佳PA的功能而言,LTM9003遠遠超過了要求。整個鏈路供電電壓為3.3V或2.5V,功耗1.5W,而且電路板面積僅為11.25mmx15mm。

圖4:LTM9003 采用節省空間的 11.25mm x 15mm LGA 封裝,運用多層基片屏蔽敏感模擬線路免受數字走線影響。

無需折中的靈活性

μModule技術還提供了意想不到的靈活性。傳統的高集成電路,可能會在可編程模式或可選功能方面提供靈活度,但會增加復雜性,并常常導致某些性能缺失。通過改變無源元件的參數值或替代IC(作為一個組進行優化),LTM9003提供特殊版本,而且不會帶來性能缺失或復雜性的增加。

例如:LTM9003-AA使用了一個3.3V電壓供電的低功率、SiGe有源混頻器。2xRF-2xLO分量產生了一個60dBc的二次諧波,這是頻譜中的最差寄生干擾。這種情況可以通過使用相似的5V器件替換該混頻器得到改善,但代價是功耗有所增加。于是,在LTM9003-AB中,二次諧波改善為6dB。同樣,在LTM9003的另一版本中,可通過換用一個210Msps ADC(其功耗較小)來降低采樣速率,并改變L-C濾波器的元件參數值實現100MHz帶寬濾波器。該濾波器將針對通帶平坦度和最佳信號鏈路性能進行優化,而且無需使用有損開關。更喜歡不同的IF嗎? 只需變更少量無源元件參數值就可以如愿以償。

綠色、小型化且易于使用

用LTM9003實現PA線性化的好處體現在幾個不同的層面。在較高層面上,DPD使您能夠以較少的補償(back-off)運行PA。PA效率越高,就同樣輸出功率級別而言,消耗的功率就越少。正如之前討論的那樣,PA是基站中最重要的電消耗因素。如果你的公司有“綠色計劃”,那么DPD能夠為做些貢獻。不管怎樣,用更少的電可以降低服務供應商的運營費用,從而使其產品更具競爭力。

在電路板層,μModule封裝將所有關鍵組件集成到非常小的面積上,其中包括用于濾波和去耦的無源組件。這節省了電路板空間、簡化了布局并為能夠進一步提高產品價值的其他功能留出了空間。

在工程層面上,LTM9003能夠節省時間。濾波器設計和元件匹配處理可以在仿真過程中完成,但是在大多數場合中,需要進行重復以保證正確。設計一個不受 ADC采樣和保持電路開關動作干擾的濾波器尤其具有挑戰性。甚至如放置電容器來實現電源去耦這樣常規的事情也可能影響整體性能,并可能導致電路板布局的修改。這些任務可能很容易耗掉幾個月的工程設計時間,以對每一次修改進行調試,并評估這些改變。用LTM9003可以直接節省時間和資源。

電子發燒友App

電子發燒友App

評論