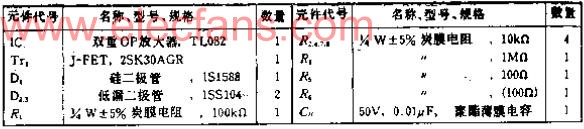

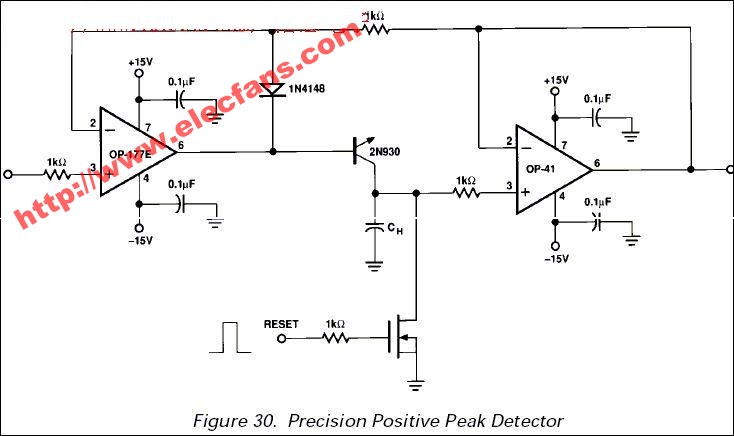

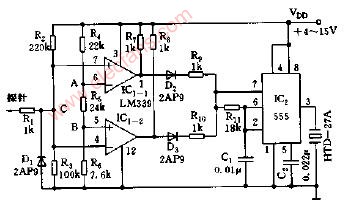

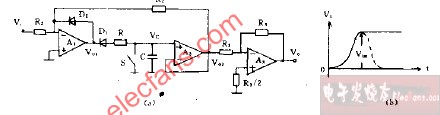

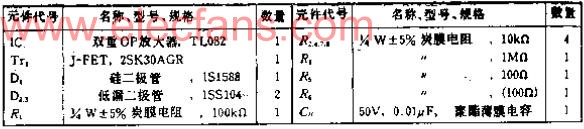

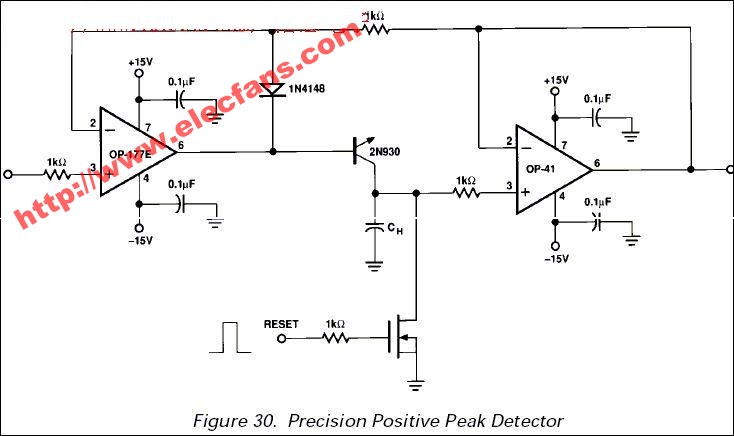

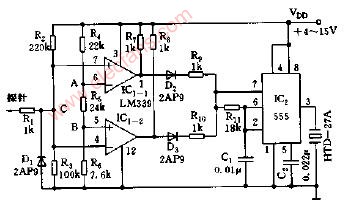

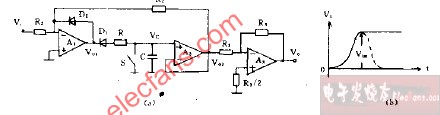

單脈沖電壓正向峰值保持電路

電路的功能

這是一種保持模擬信號(hào)電

2010-05-05 12:02:12 3617

3617

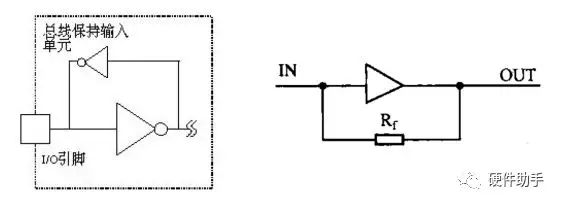

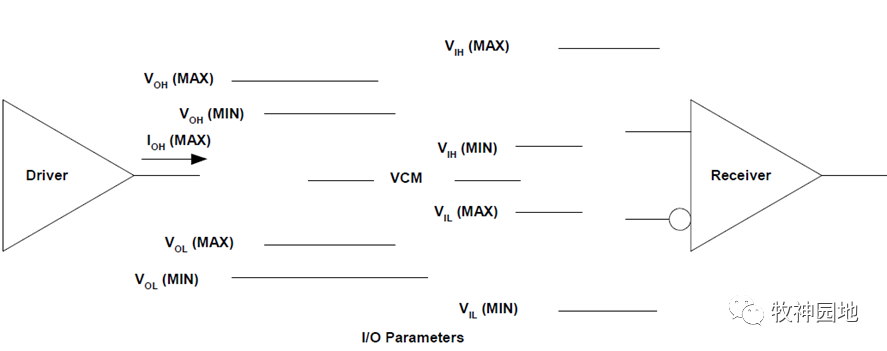

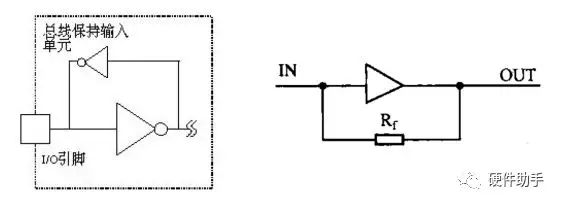

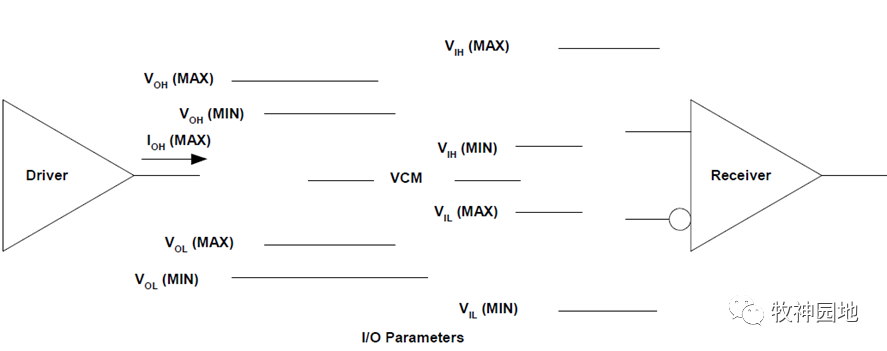

本篇主要介紹邏輯互連中的一些具有特殊功能的互連。這些特殊功能包括總線保持、串聯(lián)阻尼電阻、熱插拔等。 1、總線保持(Bus Hold) 假設(shè)初始狀態(tài)為輸入端和輸出端均為高電平,反饋電路沒(méi)有電流

2020-12-20 12:02:06 5933

5933

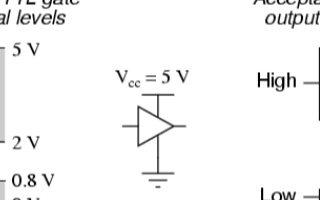

二進(jìn)制中的兩個(gè)數(shù)字0和1稱為位(bit, 是二進(jìn)制數(shù)字binary digit的縮寫)。在數(shù)字電路中,使用兩個(gè)不同的電平表示這兩個(gè)位。一般情況下,1 用高電平表示,0用低電平表示,這種邏輯體制稱為正邏輯。

2024-02-04 16:54:09 462

462

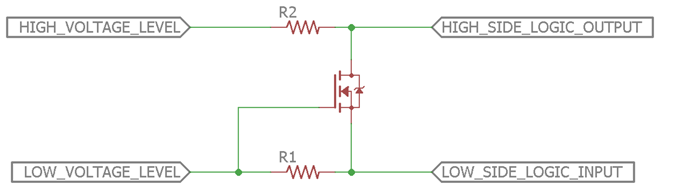

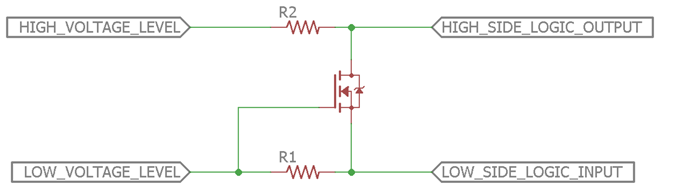

雙向邏輯電平轉(zhuǎn)換器是一種電子器件,用于在不同電壓邏輯電平之間進(jìn)行轉(zhuǎn)換。它可以將一個(gè)邏輯電平轉(zhuǎn)換為另一個(gè)邏輯電平,從而確保在不同電壓環(huán)境下的設(shè)備之間能夠正常通信和協(xié)作。

2024-02-19 16:54:00 465

465

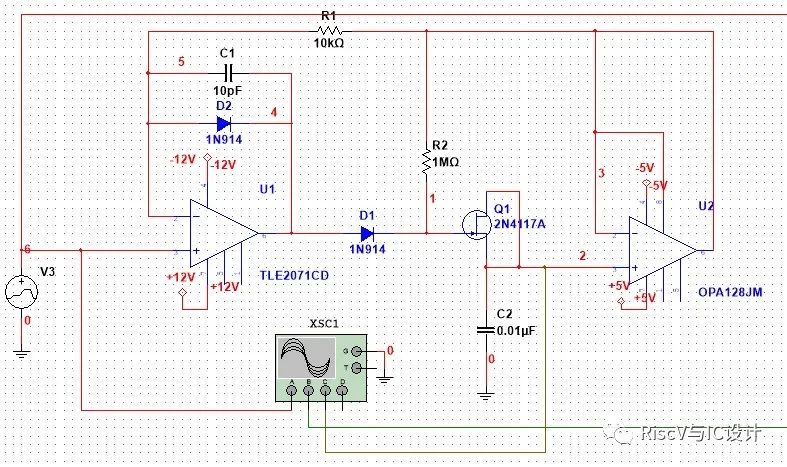

各位大俠,現(xiàn)在需要檢測(cè)保持一個(gè)幾十ns的脈沖峰值,峰值大概在10mV左右(如果太小可以增大到幾百mV),如下圖所示。目前看了使用比較器的高速峰值保持電路,請(qǐng)問(wèn)使用該電路能達(dá)到10ns的峰值檢測(cè)保持嗎?器件該怎么選擇?或者有沒(méi)有使用峰值檢波IC或者其他的方案可以選擇?希望各位指教。

2016-11-01 19:47:06

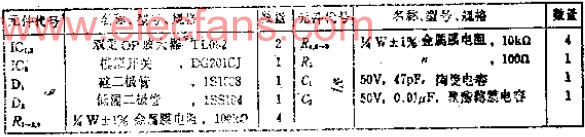

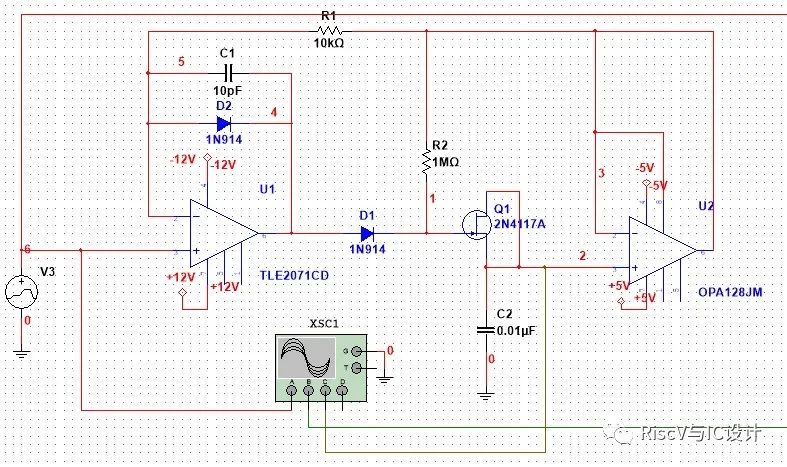

小弟最近正在搞一個(gè)高速窄脈沖峰值保持的電路,信號(hào)的上升沿>2ns,峰值在1V到2V之間,根據(jù)資料搭出了一個(gè)電路,但是峰值保持的電壓不對(duì),不知道問(wèn)題出在哪里。現(xiàn)在問(wèn)題是上升沿為5ns時(shí),峰值1V

2015-12-15 20:32:20

想要保持探測(cè)器輸入的窄脈沖信號(hào)的峰值,輸入脈沖寬度大概10ns,重頻幾十Hz,要實(shí)現(xiàn)峰值保持時(shí)間為幾毫秒,該使用哪種峰值保持電路設(shè)計(jì),電壓型峰值保持電路能達(dá)到要求嗎?

2016-07-28 16:48:45

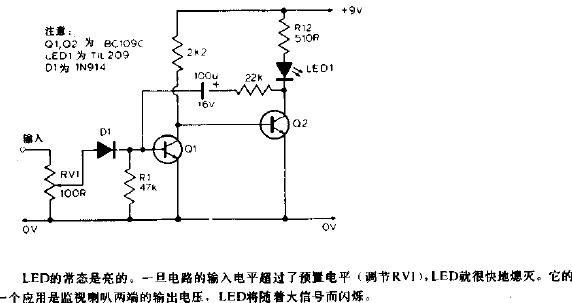

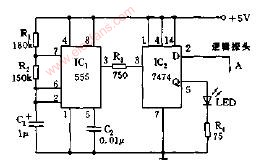

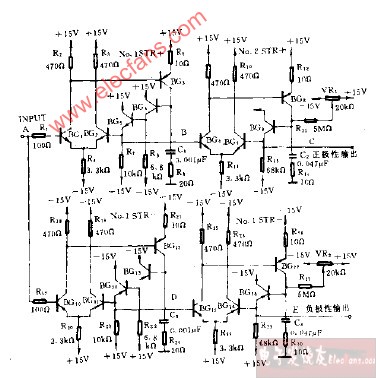

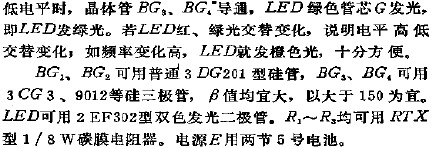

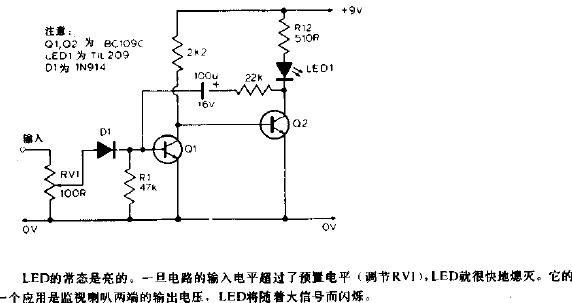

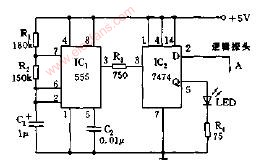

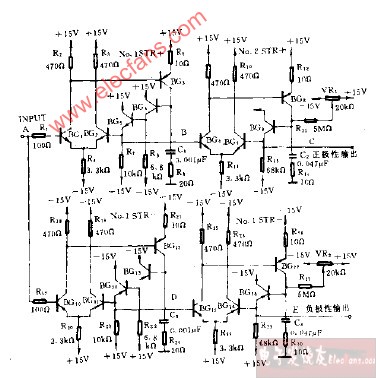

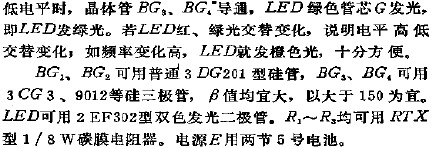

在網(wǎng)上找到了一個(gè)峰值保持LED電平表的圖紙,但用萬(wàn)能板做了個(gè)就是沒(méi)能正常工作,如下圖,希望哪個(gè)高手能指點(diǎn)下圖紙有沒(méi)有錯(cuò)誤

2018-02-25 17:26:58

正峰值檢波AGC電路

2009-09-11 00:48:43

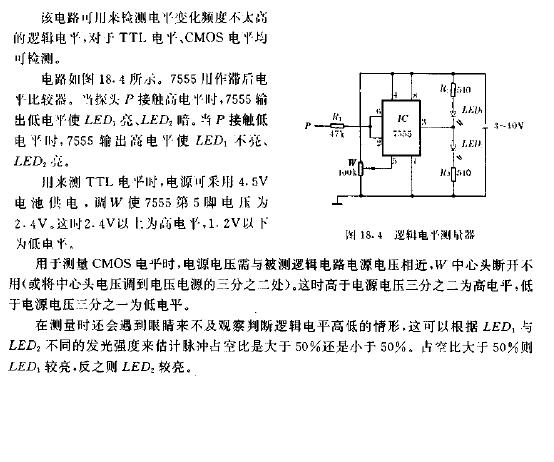

,下面以邏輯器件的功能、工藝特點(diǎn)和邏輯電平等方法來(lái)進(jìn)行簡(jiǎn)單描述。 :TTL和CMOS器件的功能分類按功能進(jìn)行劃分,邏輯器件可以大概分為以下幾類: 門電路和反相器、選擇器、譯碼器、計(jì)數(shù)器、寄存器、觸發(fā)器、鎖

2009-04-12 12:03:33

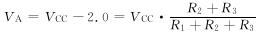

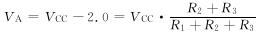

必須要求輸入高電平> Vih,輸入低電平<Vil,而如果輸入電平在閾值上下,也就是Vil~Vih這個(gè)區(qū)域,電路的輸出會(huì)處于不穩(wěn)定狀態(tài)。對(duì)于一般的邏輯電平,以上參數(shù)的關(guān)系如下

2008-06-24 09:38:52

邏輯電平轉(zhuǎn)換說(shuō)明自從TTL和5V的COMS成為邏輯電路的主導(dǎo)標(biāo)準(zhǔn)以來(lái),電子設(shè)計(jì)已發(fā)生了相當(dāng)大的改變。現(xiàn)代電子系統(tǒng)日益增加的復(fù)雜性導(dǎo)致了低電壓邏輯的產(chǎn)生,但同時(shí)又引起在一個(gè)系統(tǒng)內(nèi)部輸入輸出邏輯電平不

2009-10-24 13:43:45

`LCD單色液晶屏通常有正顯、負(fù)顯2種顯示類型,我們下面以段碼屏為例,為大家介紹下這2種顯示類型的區(qū)別:1、正顯所謂正顯就是顯示內(nèi)容的顏色要深于背景顏色,如黃綠底黑字(黃綠屏)灰白底黑字(FSTN

2019-03-02 14:19:34

PIN模塊:如果選擇正或負(fù),IOC總是設(shè)置為兩者。注意:如果使用PLL,系統(tǒng)時(shí)鐘給出大于推薦值(20MHz)的警告。

2020-05-04 18:19:59

最近做峰值保持電電路,用了一個(gè)峰值保持芯片PKD01發(fā)現(xiàn)峰值保不住,輸出到Vmax后會(huì)慢慢下降,我并沒(méi)有發(fā)復(fù)位信號(hào)。

2014-09-04 08:44:10

在屏幕上的位置移動(dòng)問(wèn)題。在電視系統(tǒng)中,采用鉗位電路將全電視信號(hào)的同步脈沖頂部保持在固定電壓,以克服直流分量損耗或干擾引起的電平波動(dòng),從而實(shí)現(xiàn)同步信號(hào)的分離。一個(gè)簡(jiǎn)單的鉗位電路由電容器、二極管、電阻器等組成

2023-02-07 16:02:32

最近看了不少關(guān)了這種電路的圖,其中好幾個(gè)都選擇的是有極電解電容但我很奇怪的是,如果選擇有極電容時(shí)候,就比如右半邊來(lái)說(shuō),到底選擇左正右負(fù)?還是左負(fù)右正呢?因?yàn)閯傞_(kāi)始時(shí)候電流走向是1的線路,也說(shuō)是需要左

2020-01-23 18:50:38

本帖最后由 gk320830 于 2015-3-9 15:55 編輯

本例中的電路可將負(fù)脈沖轉(zhuǎn)換為正脈沖。盡管這個(gè)任務(wù)看似簡(jiǎn)單,但負(fù)脈沖的幅度為-5V~-2V。按照不同應(yīng)用要求,正脈沖也需要

2011-10-14 17:19:21

如何將開(kāi)關(guān)的開(kāi)/斷狀態(tài)轉(zhuǎn)變成Arduino能夠讀取的高/低電平。解決的辦法是通過(guò)上 /下拉電阻,按照電路的不同通常又可以分為正邏輯(Positive Logic)和負(fù)邏輯(Inverted Logic)兩種...

2022-01-17 08:35:42

性,系統(tǒng)電源為負(fù)極性。兩個(gè)電路都利用NPN晶體管將比較器的輸出電平偏移VBE (R5 + R4)/R5 ≈ 4.5V (對(duì)于單相輸出,可以選擇單輸出比較器)。圖3. 該電路把負(fù)脈沖輸出轉(zhuǎn)換成正脈沖輸出

2020-11-23 09:36:51

負(fù)極性。兩個(gè)電路都利用NPN晶體管將比較器的輸出電平偏移VBE (R5 + R4)/R5 ≈ 4.5V (對(duì)于單相輸出,可以選擇單輸出比較器)。圖3. 該電路把負(fù)脈沖輸出轉(zhuǎn)換成正脈沖輸出,能夠配合負(fù)電

2022-05-02 11:03:47

性,系統(tǒng)電源為負(fù)極性。兩個(gè)電路都利用NPN晶體管將比較器的輸出電平偏移VBE (R5 + R4)/R5 ≈ 4.5V (對(duì)于單相輸出,可以選擇單輸出比較器)。圖3. 該電路把負(fù)脈沖輸出轉(zhuǎn)換成正脈沖輸出

2022-07-05 10:37:16

有人做過(guò)2ms低電平觸發(fā),之后低電平保持80ms的電路嗎?

2020-04-15 11:27:52

180°反相,但這個(gè)反相并不影響器件的功能。 這是一款簡(jiǎn)單而快速的電平轉(zhuǎn)換電路,可以將輸入時(shí)鐘調(diào)節(jié)為適應(yīng)正、負(fù)電壓電平。 電平轉(zhuǎn)換電路包括快速切換的晶體管Q1和Q2.用戶選擇電平轉(zhuǎn)換為高和轉(zhuǎn)換為低

2018-11-29 17:01:56

如圖,在multsim上仿真峰值保持電路,用模擬開(kāi)關(guān)控制放電。仿真出來(lái)在模擬開(kāi)關(guān)放電結(jié)束的時(shí)刻,C4上出現(xiàn)負(fù)電平,不知道是什么引起的。由于C點(diǎn)出現(xiàn)負(fù)電平,反饋到運(yùn)放1的反向端后會(huì)使得B點(diǎn)輸出高電平,繼而使二極管D1導(dǎo)通,C4又被充電了。搜了很多相關(guān)帖子都沒(méi)看到有人講過(guò)這里的問(wèn)題。

2019-11-25 19:44:09

我找了一些電路圖,仿真結(jié)果都不理想。大神們,有做過(guò)的嗎100M及以下的頻率都可以進(jìn)行峰值保持。

2021-05-25 17:47:46

因?yàn)樾枰胱鲆粋€(gè)峰值保持電路。輸入為一個(gè)寬度20ns,幅值0~5V的激光脈沖,一秒鐘接收50個(gè)左右。先需要將脈沖寬度拉寬來(lái)進(jìn)行采集。原理圖和效果圖如下。希望大神指點(diǎn)。

2015-09-25 09:41:09

需要選擇一款帶寬在2MHz以上、采樣率在20MSPS、位數(shù)最好是16位的高速ADC,對(duì)于有正有負(fù)的正弦脈沖信號(hào)應(yīng)選擇怎樣的ADC進(jìn)行采樣?

2023-12-21 07:40:09

你好,我需要一個(gè)峰值電壓采集保持器,來(lái)采集一系列脈沖的峰值,脈沖的電平為0-3.3v,求推薦。順便,還需要一個(gè)施密特特性的器件,把脈沖信號(hào)整形成一個(gè)方波,電平大于1v就判別為高,謝謝!

2018-08-24 11:28:34

現(xiàn)在用到一些模擬芯片,像運(yùn)放,AD等都需要正負(fù)電源供電,需要由正負(fù)5伏電源,這個(gè)負(fù)5伏電源一直困擾著我,始終沒(méi)有解決,對(duì)這款電源芯片的要求是:輸入正5伏,輸出負(fù)5伏,輸出電流200mA以上,芯片體積

2019-07-05 04:36:05

輸入端將被鉗位在0.7V,若另一個(gè)輸入為高電平,就會(huì)產(chǎn)生高電平輸出。如果A和B均為高電平,那么同相輸入端的電壓將保持為略低于VDD,而反相輸入端被拉至VDD——導(dǎo)致輸出低電平。(注:對(duì)于任何邏輯電路,選定的電阻值應(yīng)足夠大以使所有電流處于1~10mA范圍內(nèi),這樣比較器的輸出驅(qū)動(dòng)電路才能容易地驅(qū)動(dòng)邏輯)。

2011-12-23 11:49:06

這是一款簡(jiǎn)單而快速的電平轉(zhuǎn)換電路,可以將輸入時(shí)鐘調(diào)節(jié)為適應(yīng)正、負(fù)電壓電平。upg4hw電平轉(zhuǎn)換電路包括快速切換的晶體管Q1和Q2。用戶選擇電平轉(zhuǎn)換為高和轉(zhuǎn)換為低,這是直流偏置電壓,連接到晶體管的射極

2013-09-30 17:02:18

邏輯電平開(kāi)關(guān)電路

2019-11-07 03:51:49

需要選擇一款帶寬在2MHz以上、采樣率在20MSPS、位數(shù)最好是16位的高速ADC,對(duì)于有正有負(fù)的正弦脈沖信號(hào)應(yīng)選擇怎樣的ADC進(jìn)行采樣?附件print_26.bmp2.3 MB

2018-10-26 09:33:24

邏輯電平變換器電路圖

2019-10-10 09:11:31

大、可靠性差;集成電路指把分立元件電路做到一個(gè)很小的硅片的電路,成本低、體積小、重量輕、功耗低、可靠性高。 8、 正邏輯和負(fù)邏輯: 脈沖信號(hào)的高低可用“1”表示,也可用“0”表示,如果高電平用“1

2011-07-23 13:52:11

一、基本原理在輸入邏輯電平控制下出于“采樣”或“保持”兩種工作狀態(tài)。“采樣”狀態(tài)下電路的輸出跟蹤輸入模擬信號(hào),在“保持”狀態(tài)下電路的輸出保持前次采樣結(jié)束時(shí)刻的瞬時(shí)輸入模擬信號(hào),直至進(jìn)入下一次采樣狀態(tài)

2011-07-28 10:21:06

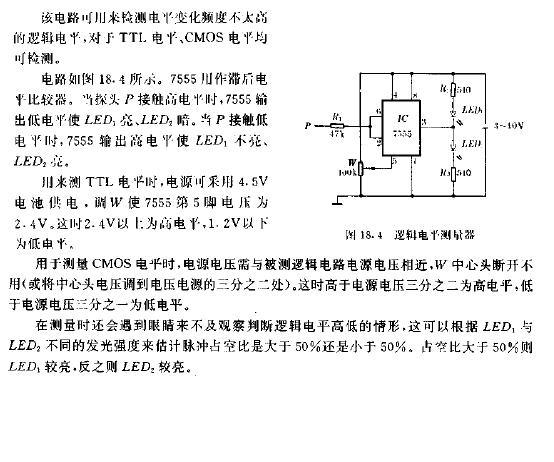

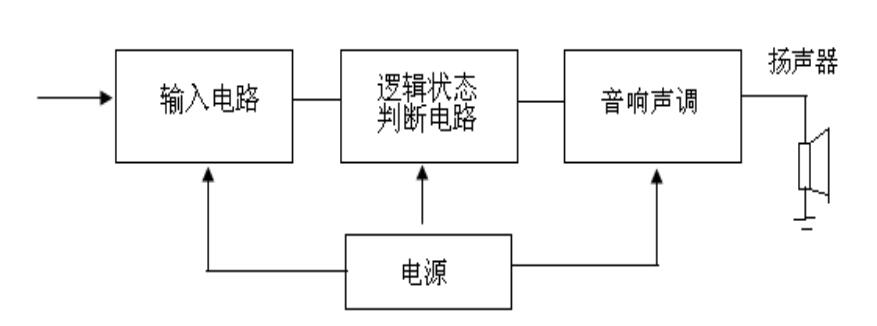

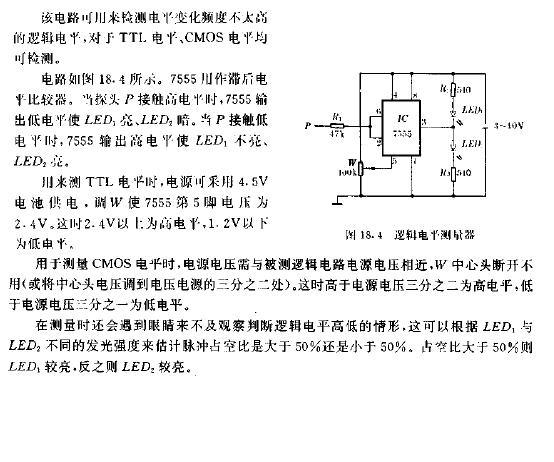

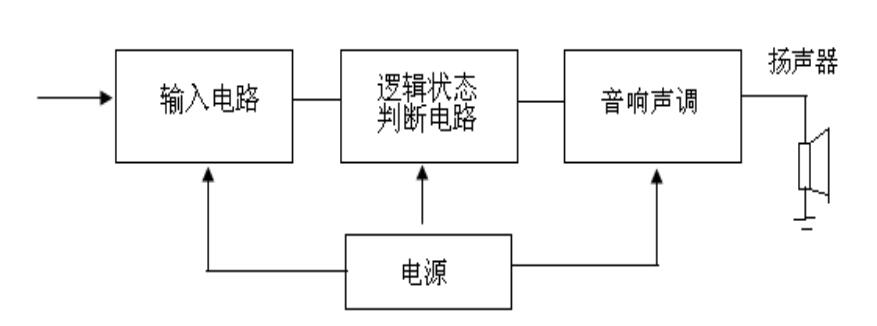

妙用邏輯電平測(cè)試筆電路及制作

2009-04-14 10:24:01 7

7 幾種常用邏輯電平電路的特點(diǎn)及應(yīng)用

幾種常用邏輯電平電路的特點(diǎn)及應(yīng)用

標(biāo)簽/分類:

在通用的電子器件設(shè)備中,TTL和CMOS電路的應(yīng)用非常廣泛。但

2007-08-21 15:34:59 1152

1152

電壓脈沖峰值保持電路

2008-10-20 08:28:21 3636

3636

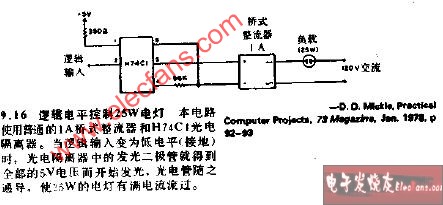

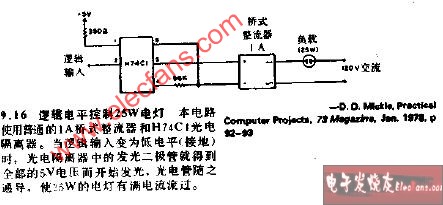

邏輯電平控制25W電燈電路

2009-01-21 01:32:57 2504

2504

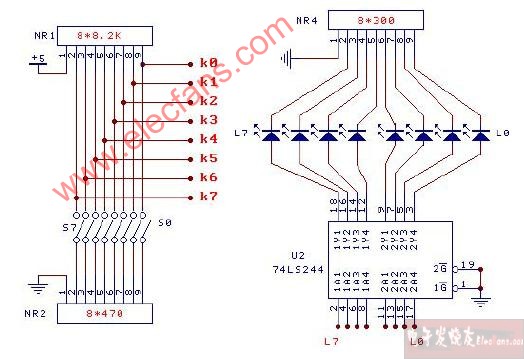

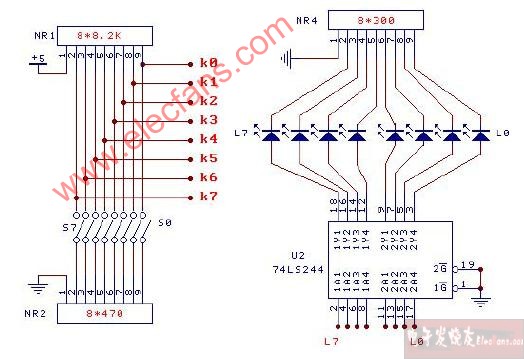

邏輯電平開(kāi)關(guān)電路如圖所示實(shí)驗(yàn)臺(tái)右下方設(shè)有8個(gè)開(kāi)關(guān)K7~K0,開(kāi)關(guān)撥到“1”位置時(shí)開(kāi)關(guān)斷開(kāi),輸出高電平。向下打到“0”位置時(shí)開(kāi)關(guān)接通,輸出低電平。電路中

2009-03-25 09:29:17 6040

6040

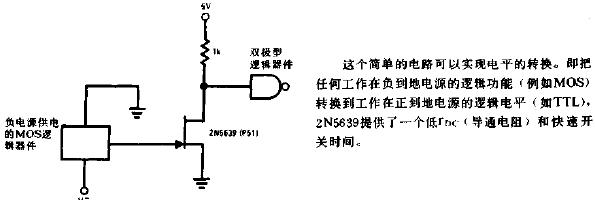

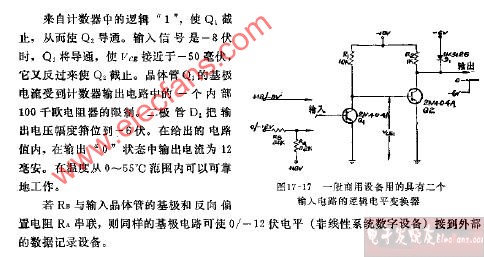

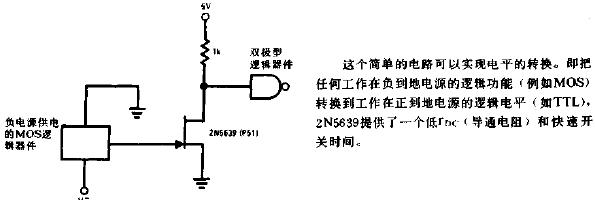

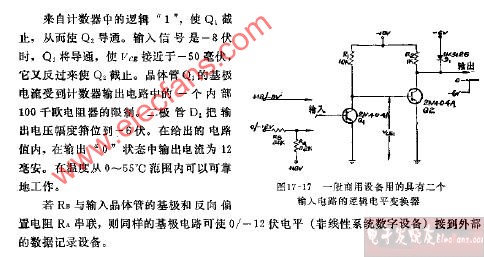

負(fù)-正電源邏輯電平轉(zhuǎn)換器電路圖

2009-04-02 09:19:43 1391

1391

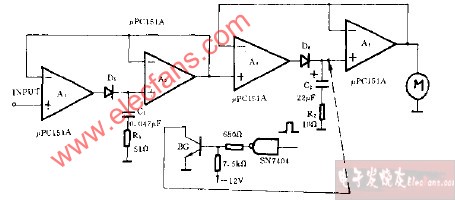

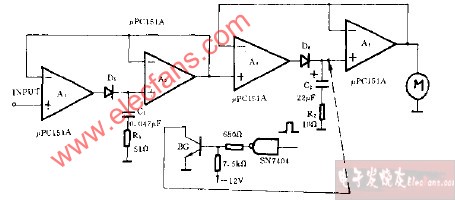

峰值電平指示器電路圖

2009-04-02 09:36:22 1823

1823

二值數(shù)字邏輯和邏輯電平

二進(jìn)制數(shù)正好是利用二值數(shù)字邏輯中的0和1來(lái)表示的。二值數(shù)字邏輯是Binary Digital Logic的譯稱。 與模擬信

2009-04-06 23:37:10 3518

3518

正負(fù)邏輯問(wèn)題

1.正負(fù)邏輯的規(guī)定

在邏輯電路中,輸入和輸出一般都用電平來(lái)表示。若用H和L分別表示高、低電平,則門電路的功能可用下表所示的電平表來(lái)

2009-04-07 00:18:31 4427

4427

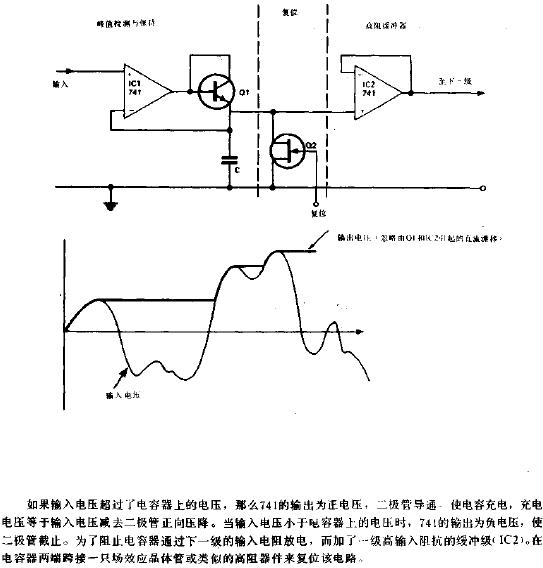

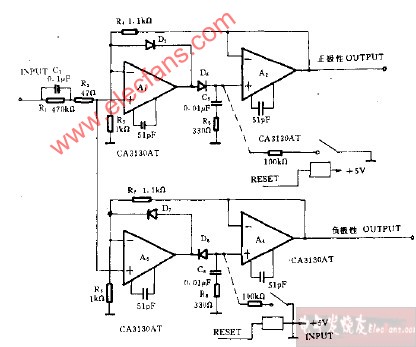

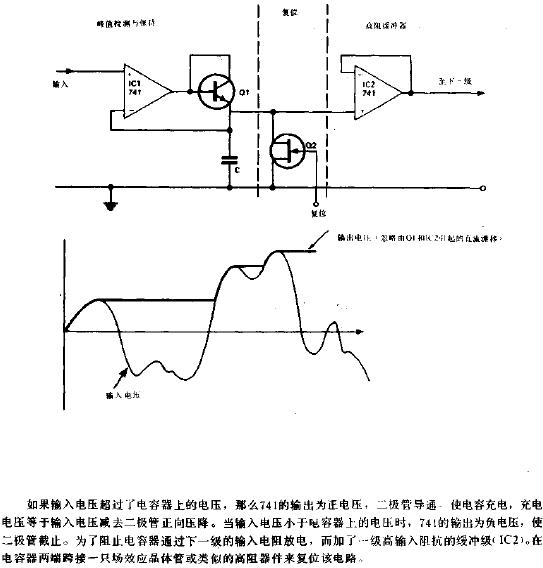

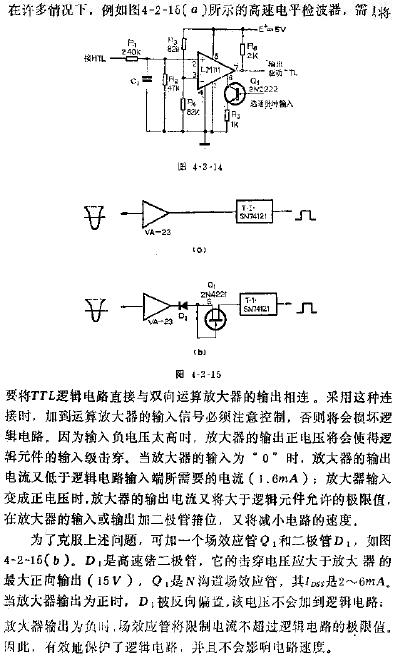

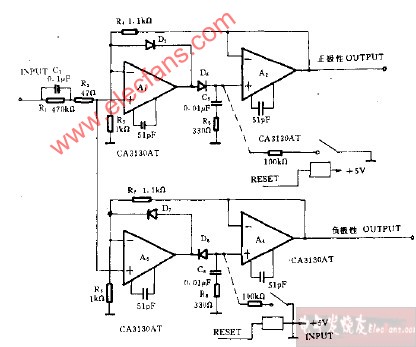

峰值的檢測(cè)與保持電路圖

2009-04-09 09:25:22 3289

3289

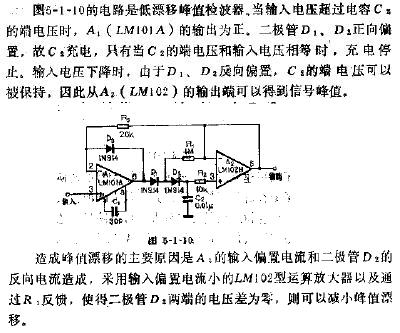

邏輯電平測(cè)量器電路圖

2009-04-09 22:07:43 713

713

邏輯電平測(cè)量器電路圖

2009-04-09 22:09:17 500

500

簡(jiǎn)單的邏輯電平變換電路

2009-04-10 10:08:28 593

593

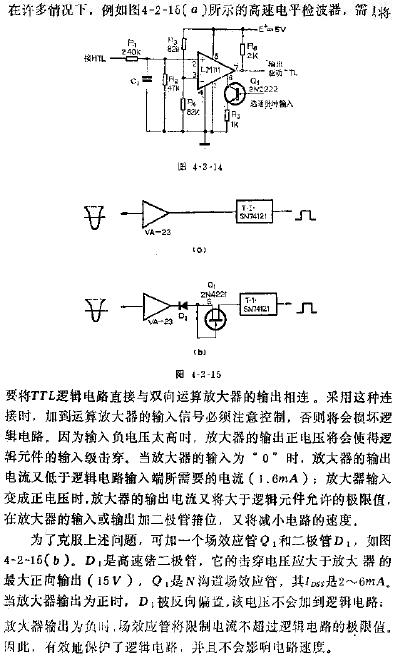

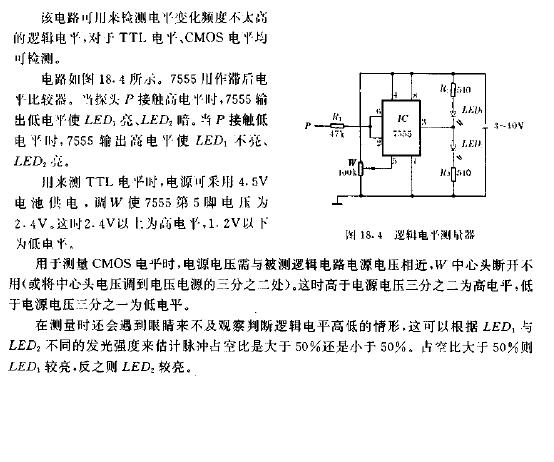

低漂移峰值保持電路

2009-04-11 10:45:27 1016

1016

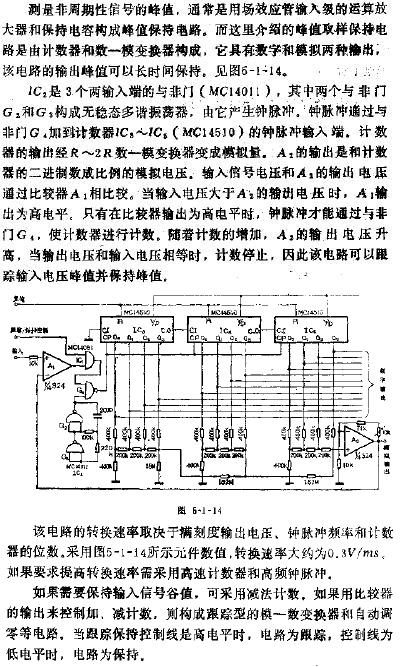

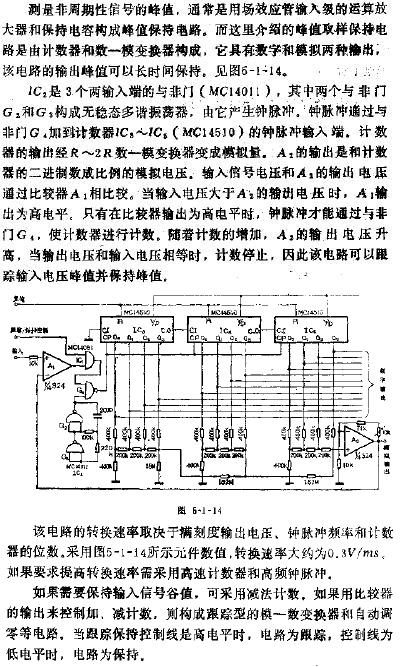

數(shù)字式峰值取樣保持電路

2009-04-11 10:51:13 908

908

音響邏輯電平探頭電路圖

2009-05-19 13:46:38 509

509

檢測(cè)高、低電平的邏輯探頭電路圖

2009-05-19 14:03:53 1612

1612

脈沖峰值保持電路圖

2009-06-20 11:15:38 1181

1181

邏輯電平變換器電路圖

2009-07-03 13:08:04 606

606

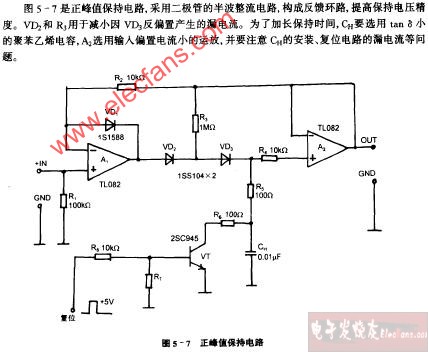

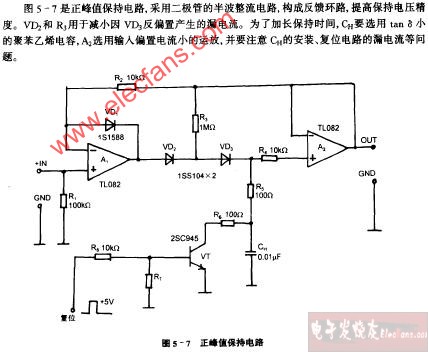

正峰值保持電路圖

2009-07-15 16:45:36 745

745

峰值保持2電路圖

2009-07-17 11:37:46 452

452

峰值保持電路圖

2009-07-17 11:38:08 1533

1533

高速峰值保持電路圖

2009-07-17 11:38:31 798

798

正峰值保持電路圖

2009-07-17 11:43:30 951

951

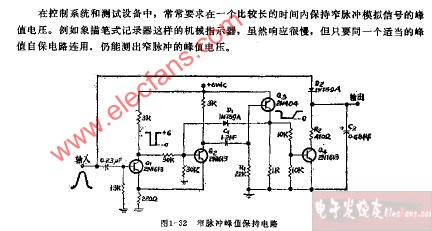

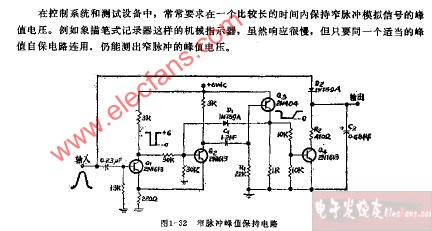

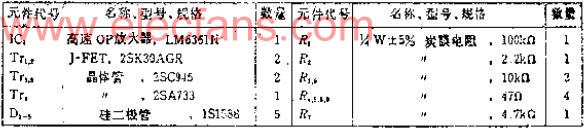

窄脈沖高速峰值保持電路

電路的功能

“6-6”介紹的峰值保持電路,

2010-05-05 13:55:24 1601

1601

微分系數(shù)為零的峰值時(shí)間檢測(cè)電路

電路的功能

用峰值保持電路可以

2010-05-05 15:12:53 1032

1032

3路模擬輸入“或”峰值選擇電路

電路的功能

本電路是一種輸入單極

2010-05-05 15:30:23 811

811

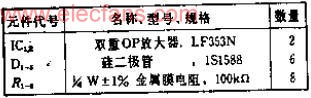

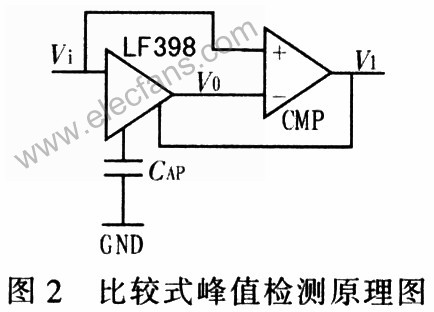

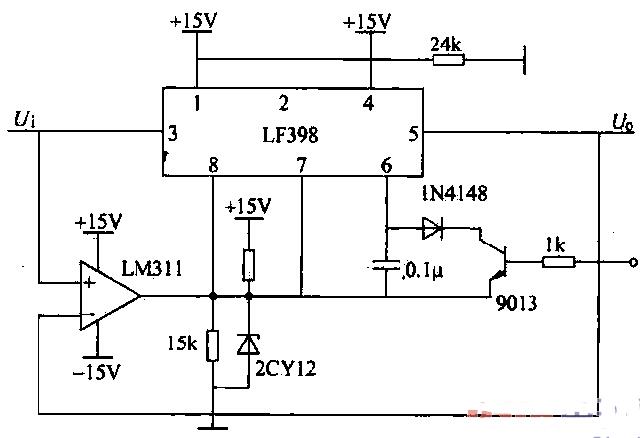

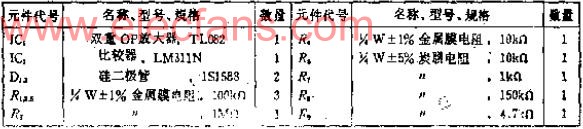

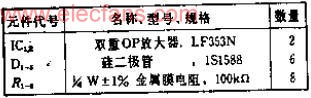

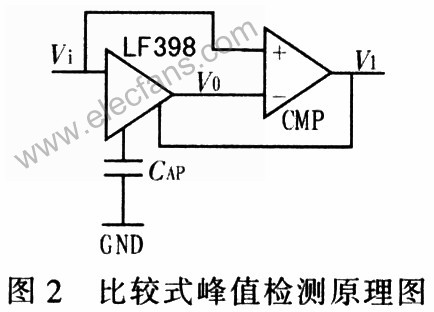

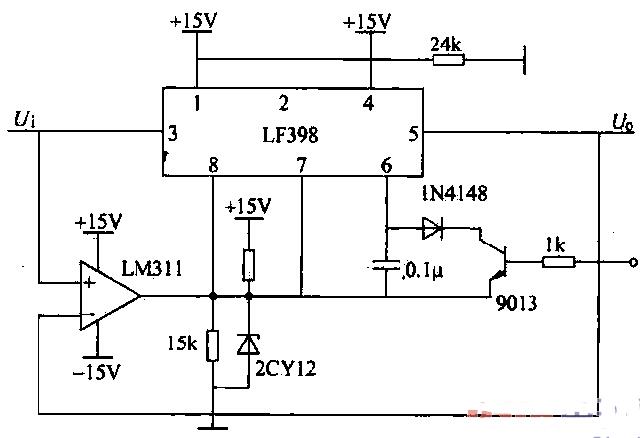

峰值采樣電路通常由采樣/保持器和比較器組成。如網(wǎng)2所示。LF398是采樣/保持器,CMP是比較器,CAP是保持電容。當(dāng)Vi>Vo時(shí),V1為高電平,并控制LF398采樣;當(dāng)經(jīng)過(guò)峰值后,Vi<Vo,

2010-08-19 11:10:42 7171

7171

圖中所示是簡(jiǎn)單而又實(shí)用的邏輯電平測(cè)試器線路.它采用雙色發(fā)光二極管作邏輯電平顯示.

2010-11-22 15:29:46 2402

2402

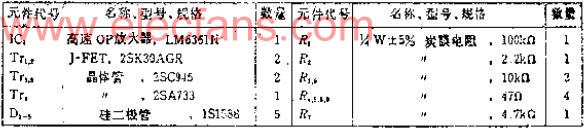

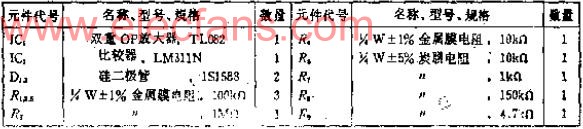

為滿足能譜分析中多道脈沖幅度分析器A/D轉(zhuǎn)換的要求,設(shè)計(jì)了一種高速脈沖峰值保持電路。以高速電壓比較器LM311、采樣/保持芯片LF398作為主要器件,具有幅度判別、波形采樣、峰值保

2012-06-28 17:16:15 639

639 邏輯電平設(shè)計(jì),個(gè)人收集整理了很久的資料,大家根據(jù)自己情況,有選擇性的下載吧~

2015-10-28 09:25:24 41

41 介紹了一種以采樣/ 保持器L F398 芯片為主要器件的峰值保持電路。該電路具有結(jié)構(gòu)簡(jiǎn)單、調(diào)試方便、性能優(yōu)良等優(yōu)點(diǎn)可廣泛應(yīng)用于各種脈沖分析系統(tǒng)。

2016-03-16 14:48:35 131

131 邏輯電平設(shè)計(jì)規(guī)范

2017-01-22 20:29:21 33

33 摘要 :本文介紹了一種以采樣/ 保持器 L F398 芯片為主要器件的峰值保持電路。該電路具有結(jié)構(gòu)簡(jiǎn)單、調(diào)試方便、性能優(yōu)良等優(yōu)點(diǎn) ,可廣泛應(yīng)用于各種脈沖分析系統(tǒng)。

2017-11-04 10:07:35 24454

24454

問(wèn)題而寫。文章先介紹常用的幾種邏輯電平,然后給出其與光模塊的接口電路。 TTL 電路的電平就叫 TTL 電平,CMOS 電路的電平就叫 CMOS 電平。 TTL 集成電路的全名是晶體管-晶體管邏輯集成電路(Transistor-Transistor Logic),標(biāo)準(zhǔn) TTL 輸入高電平最小 2V,輸出高電平

2017-11-06 16:50:08 100

100 峰值保持電路具有保持和采樣2個(gè)狀態(tài)。處于采樣狀態(tài)時(shí),電路的輸出始終跟隨輸入信號(hào);處于保持狀態(tài)時(shí),電路的輸出保持著前一次采樣結(jié)束前瞬間的輸入模擬量。在高速脈沖峰值采集過(guò)程中,為保證A/D轉(zhuǎn)換精度

2018-07-10 08:23:00 2326

2326

三態(tài)指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗?fàn)顟B(tài)。本文開(kāi)始介紹了三態(tài)門的定義,其次介紹了三態(tài)門的邏輯符號(hào),最后介紹了三款三態(tài)門邏輯電路。

2018-03-01 14:03:10 73763

73763

關(guān)鍵詞:SMP04 , 檢波電路 如圖所示為由SMP04與運(yùn)放構(gòu)成的具有保持控制的正、負(fù)峰值檢波電路。放大器A用于正峰值檢波,放大器B用于負(fù)峰值檢波。假定SMP04內(nèi)部采樣保持開(kāi)關(guān)閉合,當(dāng)正輸入電壓

2019-01-28 18:38:01 1136

1136 峰值電壓采樣保持電路:峰值電壓采樣保持電路如圖12-50所示。峰值電壓采樣保持電路南一片采樣保持器芯片LF398和一塊電壓比較器LM311構(gòu)成。LF398的輸出電壓和輸入電壓通過(guò)LM3J1進(jìn)行比較t當(dāng)U.》Uo時(shí).

2020-01-21 17:21:00 14502

14502

邏輯電平0和1的世界

2020-02-05 11:46:08 4650

4650

邏輯信號(hào)電平測(cè)試器電路由五部分組成:輸入電路、邏輯狀態(tài)判斷電路、音響電路、發(fā)音電路和電源。

2020-03-09 15:25:56 5353

5353

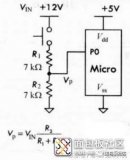

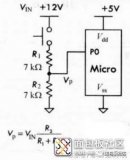

可靠的邏輯高電平I/O電路(輸入) 微控制器I/O端口線能承受的最大電壓不超過(guò)5V(不同微控制器有所區(qū)別),否則有可能燒壞I/O端口。本電路中,即使使用較大的電源電壓,分壓網(wǎng)絡(luò)也會(huì)送一個(gè)安全的(5V

2021-08-16 14:52:33 6469

6469

常見(jiàn)的單端邏輯電平及電路符號(hào)綜述

2021-09-10 15:30:02 1

1 單端邏輯電平之互聯(lián)綜述

2021-09-10 15:37:26 2

2 如果現(xiàn)在給大家出一個(gè)題目,要求用最低成本,穩(wěn)定可靠的實(shí)現(xiàn)一個(gè)按鍵開(kāi)關(guān)電路,也就是按一下按鍵,IO口輸出1,再按一下,IO口輸出0,并且電平要保持狀態(tài)。看到這里,大家估計(jì)要笑我了,這不是很簡(jiǎn)單

2021-12-08 13:36:07 1

1 由于各種邏輯電平的輸入、輸出電平標(biāo)準(zhǔn)不一致,所需的輸入電流、輸出驅(qū)動(dòng)電流也不同,為了使不同邏輯電平能夠安全、可靠地連接,邏輯電平匹配將是電路設(shè)計(jì)中必須考慮的問(wèn)題。

2022-11-10 10:01:54 8501

8501 為了精簡(jiǎn)電路 電器中會(huì)用到邏輯電平代替復(fù)雜的接線 他們都是如何設(shè)計(jì)的呢? CMOS器件與TTL器件? ? CMOS電平與TTL電平 ? 如何利用MOS管實(shí)現(xiàn)雙向電平轉(zhuǎn)換 ? 什么是LVDS電平

2022-12-14 11:36:07 437

437 自TTL和5V CMOS成為邏輯電路的主要標(biāo)準(zhǔn)以來(lái),電子設(shè)計(jì)發(fā)生了很大變化。現(xiàn)代電子系統(tǒng)的日益復(fù)雜導(dǎo)致邏輯電壓降低,這反過(guò)來(lái)又可能導(dǎo)致系統(tǒng)內(nèi)邏輯系列的輸入和輸出電平不兼容。例如,工作在1.8V的數(shù)字

2023-03-02 13:55:39 1164

1164

差分邏輯電平之間的匹配,主要應(yīng)用于時(shí)鐘和高速信號(hào)。

2023-06-25 14:56:13 1499

1499

峰值保持電路是用于捕捉變化的輸入信號(hào)的峰值,是利用記錄儀記錄峰值的關(guān)鍵電路,其有各種電路結(jié)構(gòu),分析也相對(duì)簡(jiǎn)單。

2023-10-13 15:08:25 3130

3130

Metal-Oxide-Semiconductor)。 TTL是一種基于晶體管的數(shù)字邏輯電平標(biāo)準(zhǔn),使用5V電源供電,邏輯高電平(1)通常在2.4V以上,邏輯低電平(0)在0.4V以下。TTL邏輯電平的優(yōu)點(diǎn)是速度快、噪聲容忍度高,常見(jiàn)于早期的數(shù)字電路。然而,由于功耗較大,現(xiàn)在更常用的是

2023-11-17 14:16:06 650

650 邏輯電平是數(shù)字電子系統(tǒng)中的關(guān)鍵概念之一。它決定了信號(hào)被認(rèn)定為高電平還是低電平,并進(jìn)一步影響著數(shù)字電路的正確操作。邏輯電平是用來(lái)表示數(shù)字信號(hào)狀態(tài)的電壓水平。在數(shù)字電子系統(tǒng)中,常用的邏輯電平有高電平

2023-11-24 08:20:20 1681

1681

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論