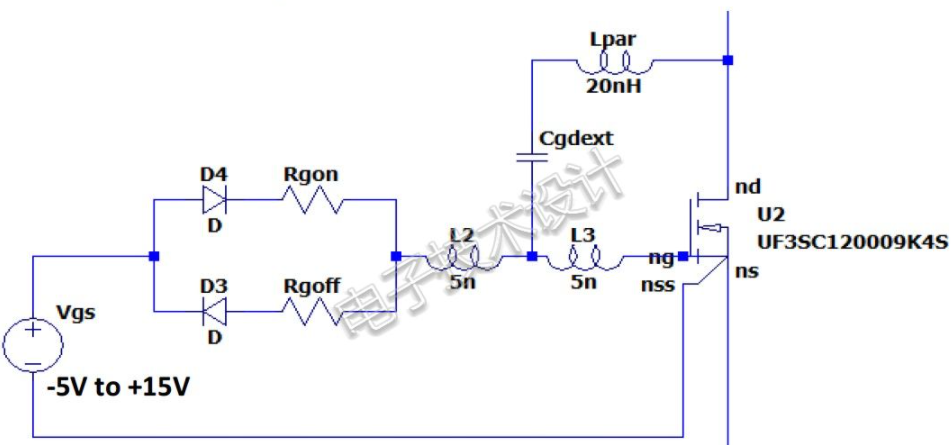

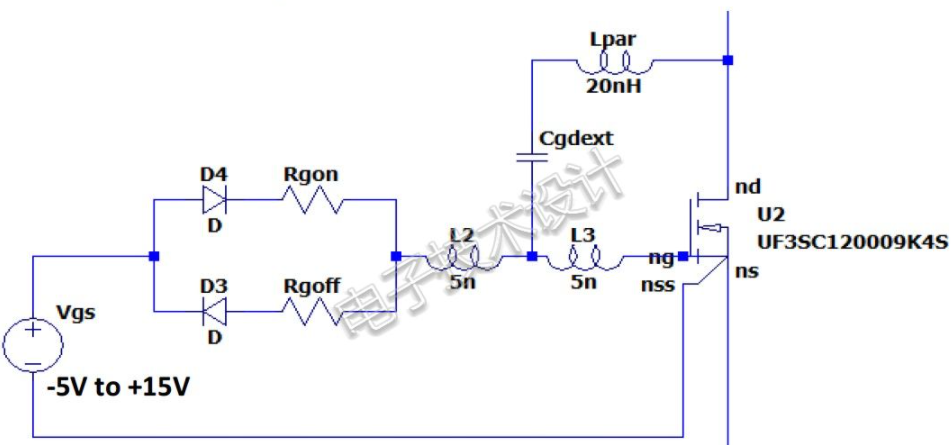

當熱插拔控制電路的輸出發生短路時,會觸發內部斷路器功能并斷開電路。但在內部斷路器做出反應之前,剛開始的短路電流可能達到數百安培。通常熱插拔控制器斷路器的延遲時間是200ns至400ns,再加上柵極下拉電流有限,柵極關閉時間可能需要10μs至50μs。在此期間,會產生較大的短路電流。

2019-03-18 14:11:00 26

26 本文重點而又全面地介紹了三種將dv/dt從45V/ns降至5V/ns而不帶來過長開/關延遲時間的方法:使用外部柵漏電容器、對器件增加RC緩沖電路,以及使用JFET直接驅動。在每種情況下,都是

2021-01-05 16:10:32 2844

2844

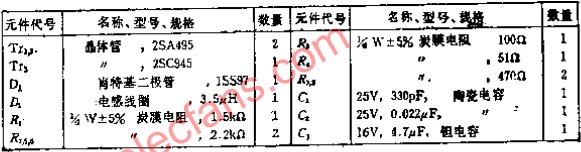

20個常用模擬電路分享

2023-09-08 10:26:55 2886

2886

100歐姆 1K,10K三檔量程怎么自動換擋的電路圖

2011-08-31 12:27:35

200Smart模擬量變頻器控制應用一、變頻器控制1.開關量多段速2.模擬量控制PLC輸出0-10V或者0-20mA控制變頻器的頻率為0-50HZ給PLC0-27648,PLC會輸出標準模擬

2021-07-02 08:08:12

200NS - Standard Recovery Diodes (Stud and Flat Base Type) - Naina Semiconductor ltd.

2022-11-04 17:22:44

20個模擬電路,

2011-11-28 02:45:28

20個經典模擬電路 介紹的都是基本電路 很值得小白去學習!!!

2016-06-29 10:46:16

20個經典模擬電路, 你必須會的哦.

2013-06-09 10:57:24

正向壓降(VSD)為1.5V,反向恢復時間(trr)為158NS。 20N20參數描述型號:20N20封裝:TO-220F特性:低功耗場效應管電性參數:20A 200V連續二極管正向電流

2021-12-02 16:32:11

針對模擬電路中存在的非線性問題,提出一種以模擬電路分形特征為輸入量的故障診斷方法。通過對多測試分量數據進行分形特征提取,輸入神經網絡建立信息融合中心融合處理各分形特征量,利用多源性互補信息減少模擬

2010-05-06 08:57:26

值、相位都和仿真值接近,但用示波器觀測輸出信號時發現,輸出波形有非常大的底噪,并且測了一會電路莫名其妙失效了,輸入為10Hz,6V幅值的正弦波,運放的in-和out端只能輸出-11.84V直流,沒有

2018-11-26 15:03:16

` 本帖最后由 僅侑的執著 于 2017-11-1 09:55 編輯

產品簡介 ASD906A(20V/10A)模擬電池電源具有輸出供電和輸入充電功能,可模擬電池的充電、放電。該設備主要

2017-10-31 13:46:47

無毛刺 。 可 ADuM3200 的輸出 卻總是 存在 10nS 到20nS 的毛刺。 急求 AD 公司 技術專家 給予 解答 ,萬分感謝 。。急。。

2018-08-17 06:59:53

Photodiode 200ns

2023-03-28 18:44:36

Photodiode 200ns

2023-03-28 18:44:36

您好,我們公司已購買示波器:“MSOX3024A示波器:200 MHz,4,模擬增強16數字通道”。我們在測試的硬件設備中對SDRAM執行測量信號。信號周期可以是0.5ns(10 ^( - 9)秒

2019-02-14 16:47:49

”,REFCKF_FREQUENCY是200.0(默認值)如果我將CNTVALUEIN設置為31(最高抽頭),那么我得到2.5 ns的DATAOUT延遲(應該是5 ns而不是?)。如果我訂

2020-06-13 08:47:07

本帖最后由 現在/明白 于 2018-1-24 10:10 編輯

門延遲大于cpu時鐘?那cpu中的運算器是怎樣工作的呢?它內部是不是低于1ns延遲的門電路呀?

2018-01-24 10:07:29

線3D7428-2.5延遲線DDU222F-200延遲線3D7428-4延遲線DDU222F-250延遲線3D7428-5延遲線DDU224F-10延遲線3D7428-7.5延遲線DDU224F-20延遲

2021-06-04 17:02:58

特征?總延遲62ns?2ns延遲步進增量?在±5V電源下運行?高達122MHz帶寬?低功耗?20 Ld QFN(5毫米x 5毫米)包裝?無鉛(符合RoHS)應用?RGB的傾斜控制?模擬波束形成

2020-09-17 17:22:08

Cyclon IV FPGA做個信號采集轉換的電路,加了個IS61WV5128BLL的ram,按手冊FPGA用50MHz(20ns)讀寫RAM正常,但換到100MHz時鐘時就出現讀出的數據是上個地址寫入的數據,手冊上貌似這個RAM是可以10ns讀寫的啊。。。

2018-05-23 16:21:19

我的程序和仿真都沒有問題,但是仿真的時候,發現軟件默認的周期是200ns,我想要得到周期20ns的應該怎么設置?先謝謝給位前輩了{:soso_e183:}!!

2012-05-05 15:10:02

各位前輩,我是一個新手,我在做仿真的時候需要一個周期為20ns的時鐘信號,但是發現軟件系統默認的是200ns的,請問我在如何設置?{:soso_e183:}小生在這里先謝謝各位前輩了!

2012-05-05 15:18:22

盛鉑科技SWFA200捷變頻頻率綜合器是一款在頻率范圍內任意兩點頻率的跳頻時間在4uS以內的高速跳頻源,其輸出頻率范圍為200MHz至20GHz,頻率的咨詢4006218906最小步進為10

2021-11-04 13:46:16

詳細說明:TLP352是可直接驅動中等容量IGBT或者功率MOSFET的DIP8封裝的IC耦合器。該產品的延遲時間為200 ns,光電耦合器之間的傳輸延遲時間差(PDD*) 為90 ns(上述

2019-09-20 09:03:36

有沒有大佬知道TMS320C6748IO口中斷的響應和建立時間是多少啊? 手里現在打算用IO口中斷檢測一個周期為200ns的FPGA時鐘信號,但是測試時發現IO中斷很慢,和需求差別很遠,這個FPGA

2021-10-14 15:17:35

UPS的延遲啟動電路及UPS輸出負載百分比指示電路

2019-05-10 11:31:13

·集成階躍恢復二極管輸出:50Ω,SMA(母);·< 60ps過渡時間;兩路2.5V~6V可調幅度輸出;·±1ns時間偏移,1ps步進;·200ns~4μs脈沖寬度;1μs~1s內部時鐘周期

2017-06-21 09:47:01

在Verilog的建模中,時間尺度和延遲是非常重要的概念,設置好時間尺度和延遲,可以充分模擬邏輯電路發生的各種情況和事件發生的時間點,來評估數字IC設計的各種要求,達到充分評估和仿真的作用。注意延遲

2021-08-16 14:16:54

類型,因此參考clk為200M,因此最大延遲時間約為2.5ns(31 * 78ps)。對? 我該怎么做才能產生3 ns的dq延遲?以上來自于谷歌翻譯以下為原文Hi,I am adding a NAND

2019-03-29 14:03:35

在stm32f1中,如何使用定時器對一個脈寬為200ns的脈沖(模擬信號)進行計數。是否可以用內置比較器對脈沖信號進行整流后再用定時器計數?f1系列能否完成200ns的采樣?

2020-04-27 14:53:08

9300超低壓降:45mV/20mA, 2.3V至5.5V的工作電壓,電流匹配精度為±1%;NS9300驅動4路LED,每路電流20mA;NS9300 PWM調光:調光頻率高達50KHz;NS9300內置過熱保護電路,無EMI和開關噪聲, 關機電流

2011-08-07 19:33:26

; data_b = 1;//200ns之后,data_a=0;data_b=1;13#200 data_a = 1; data_b = 0;//200ns之后,data_a=1;data_b=0

2019-12-13 16:43:08

,剛開始的短路電流可能達到數百安培。通常熱插拔控制器斷路器的延遲時間是200ns至400ns,再加上柵極下拉電流有限,柵極關閉時間可能需要10μs至50μs。在此期間,會產生較大的短路電流。本電路用于

2019-03-18 14:01:13

LMH7220的上升和下降時間約為 0.6 ns,而傳播延遲時間約為2.7 ns。5V供電時,中心頻率為70MHz,帶寬為10Hz-20MHz。根據芯片資料,這款芯片應該能對80MHz的正弦信號進行

2023-03-20 16:22:35

4.5v,Convb信號200ns,低脈沖,Busy始終為低電平。若只提供3.3v供電,AVCC實測為2.5v,Busy信號正常,為4us左右的高脈沖。

現想咨詢這個情況該如何排錯?電路參考的是手冊中9電容的電路圖/

2023-12-04 06:14:01

進行音量自動調節,延遲時間可以控制的自動增益延遲音響放大器。基本要求1) 輸入音頻信號(10Hz~1KHz),輸出可以帶200Ω負載或驅動8Ω喇叭(2~5W),輸出波形基本不失真。(20分)2) 當

2016-05-23 19:48:14

如何使用ucf約束文件為輸入數據添加一個小延遲?我試圖為來自名為“chana_rd”的引腳的輸入數據添加一個小延遲,如何添加此延遲?另外,我對chana_rd有一個約束如下。這會如何影響延遲

2019-03-28 12:03:32

我有什么: STM32L496,模擬信號輸入。我需要的是:在某種級別的模擬信號上,以一定的延遲開始 ADC 轉換(80...200 ns。基本上,55-80 ns 是內置比較器的傳播延遲,20 ns

2023-01-06 07:11:14

**第一至第三章**Q1. 若存儲器的數據總線寬度為32位,存取周期為200ns,則存儲器的帶寬是多少?存儲器的帶寬指單位時間內從存儲器進出信息的最大數量。存儲器帶寬 = 1/200ns ×32位

2021-07-28 06:23:01

對于晶振為24M的,C8051F310.延遲10us的 延遲函數怎么編寫{:4:}{:4:}{:4:}

2014-08-13 13:13:38

當今的一些高精密模擬系統需要低噪聲正負電壓軌來為精密模擬電路供電,這些電路包括模數轉換器 (ADC)、數模轉換器 (DAC)、雙極放大器等等。如何產生清潔、穩定的正負電壓軌為噪聲敏感型模擬組件供電是擺在我們面前的一個設計挑戰。

2019-08-13 06:03:34

1.7ns?以下引自DS152:2.如果上述問題的答案是肯定的,我該如何處理不同的ADC采樣率?例如,如果ADC以20MHz @ 10bit運行,則LVDS輸出頻率為100MHz,位寬為5ns。如果我將

2020-06-17 16:16:23

若存儲器的數據總線寬度為32位,存取周期為200ns,則存儲器的帶寬是多少?說明刷新有幾種方法?指令是指什么?

2021-10-19 10:20:42

指針式萬用表RX10K檔電壓為12V,其它電阻檔為2.4V。那么為什么會有電壓呢,這樣測量電阻時會不會破壞電阻啊

2014-09-15 15:41:11

約為16 ns,但我試圖將其降低到10 ns以內。我嘗試了OFFSET約束,它將延遲從21ns降低到16ns。但是我還能用什么來進一步降低延遲?或者,如果這是最好的FPGA芯片(Spartan 3E

2019-03-25 14:59:33

(ADC0809的說明書要求start的脈沖寬度不超過200ns,典型值為100ns),請大佬們幫幫忙若是需要換一個頻率較大的晶振,請問這樣還能與PC機進行通信嗎?波特率會受影響嗎?使用較大晶振后,再編寫程序,會有什么影響(使用的keil 4)?麻煩大佬們幫忙

2018-03-01 17:46:04

有個問題身邊也沒有人問 只能來論壇請教了 請各位大神指導啊!!!想實現FPGA接DA芯片輸出模擬電壓,DA芯片為SPI傳輸,FPGA程序為計數,計數一次步長時間為200ns左右,FPGA時鐘頻率為

2015-04-24 22:35:09

LTC2325-12

1 應用:通過MCU軟件控制ADC進行不定時的單次采樣,可能數秒鐘1次或者連續以200ns時間間隔采集n組數據等突發式的采集。ADC不進入待機狀態。這種數秒鐘1次的單次或者

2024-01-08 06:55:22

分五檔 10,15,20,25,30,自動改變轉速

2015-12-27 16:46:06

選擇1X檔時,信號是沒經衰減進入示波器的。而選擇10X檔時,信號是經過衰減到1/10再到示波器的。當選擇10X檔時,應該將示波器上的讀數也擴大10倍,這就需要在示波器端可選擇X10檔,以配合探頭

2019-05-20 14:43:22

問題:能否在200 ns內開啟或關閉RF源?

2019-03-01 08:56:59

提出一種獨特但簡單的柵極脈沖驅動電路,為快速開關HPA提供了另一種方法,同時消除了與漏極開關有關的電路。實測切換時間小于200 ns,相對于 1 μs 的目標還有一些裕量。其他特性包括:解決器件間差異

2018-10-24 10:21:59

如題 請教!時鐘:內部64M為何我實際測量約在400ns而不是200ns左右?

2019-03-01 08:23:26

有沒有辦法在電路包絡模擬中使用延遲元件,這樣只會延遲包絡波形(而不是RF波形)? 以上來自于谷歌翻譯 以下為原文Is there a way to use a delay element

2019-07-22 06:46:33

大家好,我目前正在為我的項目尋找評估委員會。我的設計中有一條時間關鍵路徑。該路徑需要4個觸發器,2個多路復用器和一個用于操作的邏輯門。通過該路徑的傳播時間(延遲)應小于30ns。這可能與FPGA有關嗎?如果是這樣,可以推薦哪種評估板和時鐘頻率?最好的祝福

2019-09-26 10:12:35

輸入信號。 SY89296L是一款可編程延遲線,可通過數字控制和模擬控制延遲輸入信號。延遲時間從2.2ns到12.43ns不等。此外,輸入為LVPECL,使用2.5V或3.3V電源

2019-03-05 08:20:02

工程師應該掌握的20個模擬電路

對模擬電路的掌握分為三個層次。初級層次是熟練記住這二十個電路,清楚這二十個電路的作用。只要是電子愛

2010-03-29 11:35:15 1323

1323 本文提出了一種數字延遲單元的設計方案,該方案能夠實現0.1ns的延遲度精度和10ms的動態范圍,通過調節該方案的工作參數可以很方便的實現更大的動態范圍。該電路在Virtex5系列的FPGA

2010-07-17 18:03:31 19

19

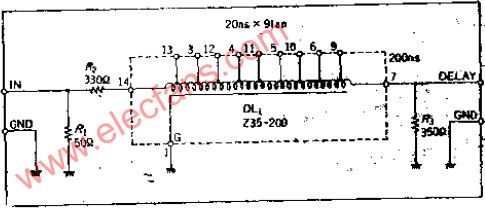

具有20ns轉換時間的精密振蕩器電路圖

2009-04-15 09:31:02 474

474

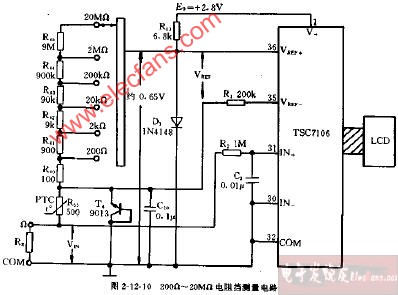

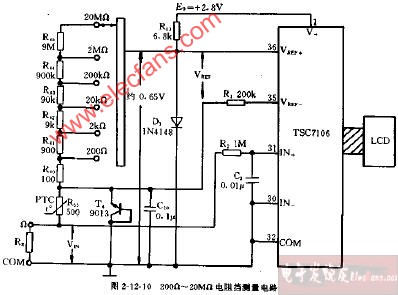

DT890B型200Ω~20MΩ電路圖

2009-07-18 17:26:15 1062

1062

延遲線電路,延遲線電路是什么意思

延遲線電路的定義

2010-03-09 11:30:46 1148

1148 延遲時間在5NS以內的高速響應微分脈沖發生電路

電路的功能

使用

2010-05-10 16:54:51 1460

1460

電子電路工程師必備的20種模擬電路電子電路工程師必備的20種模擬電路

2016-01-11 14:04:33 0

0 工程師應該掌握的20個模擬電路,入門必備

2016-02-17 15:31:12 37

37 20個經典模擬電路資料_全學懂后基礎就扎實了。

2016-06-21 17:02:48 145

145 包含電子工程師應該掌握的20個經典的模擬電路

2016-08-25 15:52:39 79

79 工程師應該掌握的20個模擬電路,感興趣的小伙伴們可以瞧一瞧。

2016-09-18 17:34:53 0

0 基于NS2模擬器的TCP仿真的設計和實現_錢開國

2017-03-17 17:32:28 2

2 WSF25N10-TO-252 N 200V20A

2017-07-10 14:06:25 11

11 電子發燒友網為你提供Broadcom(ti)ASMT-BB20-NS000相關產品參數、數據手冊,更有ASMT-BB20-NS000的引腳圖、接線圖、封裝手冊、中文資料、英文資料,ASMT-BB20-NS000真值表,ASMT-BB20-NS000管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-07-04 11:58:02

手冊本文檔的主要內容詳細介紹的是NS-SW300和NS-SW200型超低音揚聲器的維修手冊免費下載。

2019-11-19 08:00:00 19

19 學習51單片機及模擬電路資料包括20個模擬電路和C語言程序免費下載。

2021-03-12 17:40:45 42

42 LT1721 Demo Circuit - 0ns to 10ns Pulse Width Generator

2021-03-24 21:46:28 9

9 LTC6994/LTC6993演示電路延遲單次(延遲50ms,單次10ms)

2021-04-10 10:35:33 4

4 初學者必知的20個模擬電路

2021-05-29 09:27:46 436

436 LT1721演示電路-0 ns至10 ns脈沖寬度發生器

2021-06-03 16:35:16 25

25 LTC6994 LTC6993演示電路延遲單次(延遲50ms,單次10ms)

2021-06-09 20:54:37 93

93 由于內部斷路器延遲和有限的MOS柵極下拉電流,許多熱插拔控制器在短路輸出后的前10μs至50μs內不限制電流。結果可能是幾百安培的短暫流量。一個簡單的外部電路通過最小化初始電流尖峰并在200ns至500ns內終止短路來解決這個問題。

2023-03-17 11:34:07 623

623

由于內部斷路器延遲和有限的MOS柵極下拉電流,許多熱插拔控制器在短路輸出后的前10μs至50μs內不限制電流。結果可能是幾百安培的短暫流量。一個簡單的外部電路通過最小化初始電流尖峰并在200ns至500ns內終止短路來解決這個問題。

2023-03-31 11:15:30 570

570

電子發燒友App

電子發燒友App

評論