有時會失敗。現在越來越難了。雖然原來的設備在互聯網的陰暗角落里仍然可用,但我想嘗試用PIC作為替代品。問題是,像幾乎所有74系列IC一樣,原始設備上的+V電源引腳處于上升狀態。嗯,對了,在引腳20上,因為

2019-10-17 10:26:11

一直都認為,如果在ADA4932-2的Vocm引腳上加多少的電壓,四路輸出的直流分量就是多少電壓。可是今天測量發現,改成0.5V或者0.25V,輸出都是1V的直流分量。我是用+5V和gnd供電的。輸入的數據不帶直流分量。為什么是這樣呢?這個1V是怎么得到的呢?

2023-12-25 08:09:07

使用 10V 電位輸入,如果一個人在他們的面包板上“接線錯誤”……我們會損壞什么東西嗎?如果我犯了一個編程錯誤并指定沒有衰減但在 ADC 輸入引腳上施加 10V,這會損壞什么東西嗎?這個有一個線程詢問默認電壓范圍....

2023-03-01 08:33:59

在我們的設計中,BPI-up模式用于Virtex 5配置。在這種情況下,并行閃存的復位通過外部上拉電阻直接連接到FPGA的program_b引腳。此連接應足以進行正確配置。但是在prog_b引腳

2019-01-23 06:10:35

我想在 I35 和 I39 引腳上使用中斷,如果在 I39 引腳上打開 WiFi 模塊中斷它不能正常工作,如果關閉 WiFi 模塊在 I39 引腳上正常工作中斷。所以我在

2023-04-12 09:00:39

對于NuMicro?家族所有系列,VREF引腳必須外接一個電容,其電容值需要抑制電壓紋波,應小于ADC的一個LSB大小,以避免電源噪聲干擾ADC精確度。例如,12-bit ADC、VREF電壓為3.3v,其紋波大小應在3.3/(2^12) = 0.8mV以下。

2023-06-16 07:05:24

的影響。形成懸浮地或是懸浮電源,在復雜的系統中完成各部分地線或是電源的協調匹配,有源器件在開關時產生的高頻開關噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個局部的直流電源給有源器件,以減少開關噪聲在

2020-12-02 09:34:28

引腳上產生耦合的情形是怎么樣的?

2021-04-07 06:02:58

,以及一些重要的控制腳上的直流電壓。 (2)在沒有所要檢查的集成電路各引腳標準工作電壓數據時,要利用各引腳外圍電路的特征來判別引腳電壓的明顯異常現象。實在無法確定時,可找另一臺相同型號的電器設備

2020-12-08 17:48:30

輸出高電平的值。2、OC門電路必須加上拉電阻,才能使用。3、為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻

2019-08-05 04:36:09

波動對輸入級/高電壓增益級的影響;3.形成懸浮地或是懸浮電源,在復雜的系統中完成各部分地線或是電源的協調匹 有源器件在開關時產生的高頻開關噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個局部

2016-07-24 20:49:21

我在使用AD421的過程中,測得LOOPRTN 引腳對COM引腳的電壓在+1.6V,COM引腳是接GND的。但是AD421的技術手冊說LOOPRTN引腳對COM腳 電壓為-2V到+0.5V。為什么出現負的電壓?這兩個腳的電壓究竟是對少?附件AD421.JPG77.1 KB

2018-12-26 09:11:59

AD7616在空載時,輸入引腳上的電平為1.6V左右是為什么,因為偏置電流的影響嗎,該芯片偏置電流多大,怎么計算的?

2024-01-26 06:34:59

我正在使用AURIX? TC399,在我的項目中,我使用大約 40 個引腳作為輸入引腳。 我需要在這些引腳上設置邊緣觸發中斷。 我找到了 ERU 示例代碼。 但我無法將所有這些引腳設置為中斷引腳。 是否有辦法使用 ERU 為這些 GPIO 配置中斷?

或者有其他配置方法嗎?

2024-03-04 07:06:29

的是 BTA26)。GATE 和 MT1 之間的關系是否受 MT1 引腳上驅動的負載影響?事實上,我更喜歡在 MT2 引腳上放置感性負載,但設計可能需要我將負載放在 MT1 引腳上。要切換的電源電壓為 L1 和中性線 (120VAC)。請指教。

2023-01-09 08:56:51

) FT_xx 引腳上的輸入電壓,除了 FT_c = VDD + 4.0 最大值2) FT_c 引腳上的輸入電壓 = 5.5 最大值3) 任何其他引腳上的輸入電壓 = 4.0 伏最大值我

2023-01-06 06:21:32

我有一個 GPIO 被下拉到“公共”地面,我正在從 10v 信號觸發中斷(上升)。

我有一個 10kohm 和 4.7kohm 的分壓器,所以當有信號時,我的引腳上的電壓剛好超過 3 伏,這工作正常

2023-05-29 07:42:26

=α1OWF3EIQ4M另外我附上了方案。功率是3.3V。我測試了多個控制器,它們工作相同。我試過用例子來編程,也有同樣的問題。引腳上的電壓不會下降到GND。也許,有人知道我應該去哪里找麻煩嗎?當做。示意性打印13.9

2019-01-18 08:21:20

CT 引腳上的絕對最大額定電壓是多少?Datasheet 只有差分電壓范圍和這個注釋: 我想知道 MC33772 是否能夠承受任何 CT 引腳中的電池短路 (12V)。

2023-03-27 07:19:56

電壓點亮紅色或綠色的LED。奇怪的是,AN1輸出4.42伏,它從分壓器中取出2.97伏,當在引腳處測量時,將其網到3.5伏。我必須假設我沒有正確配置。此外,當供電,沒有發生,直到我聯系MCLR到VDD。我想把配置設置為MCLRE_OFF時,引腳被降級為輸入端口。仍然在學習,所以請解釋我做錯了什么。謝謝

2019-09-30 08:19:23

大家好,我剛買了一套ST-LINK-V3。另外,我檢查了 vcc 引腳上的信號,但 vcc 上沒有電壓。這是對的嗎?

2023-02-03 06:44:15

根據 RM 的說法,我認為可以在單個引腳上使用多個模擬功能。我們可以對數字引腳做同樣的事情嗎?我需要的是在同一個引腳上放置一個定時器通道(作為輸入)和一個外部中斷輸入。

2022-12-20 06:30:23

當 GPIO 引腳通過磁性開關連接到外部設備時,從 STM32 的角度來看,它如何知道磁性開關是開還是關?ON -> 設備電源打開同樣關閉。STM32 能否檢測到 GPIO 引腳上的電流變化?任何建議將不勝感激。

2023-01-03 08:41:23

TC275 ADC通道引腳如何映射到復用引腳上去,函數上怎么配置?

2024-02-19 07:46:21

adc引腳懸空時,串聯在adc引腳上的電阻有0.1v的分壓,難道adc懸空時,引腳不是高阻態?

2024-03-05 08:20:17

pcb走線為什么直接連不到芯片引腳上呢?

2023-04-10 16:29:30

電容掉到VDIO0引腳上嗎?多謝雨果埃利亞斯 以上來自于百度翻譯 以下為原文Hi all, I'm laying out a very space constrained PCB with a

2019-03-21 14:59:25

和高電平,比如有可能1 ~ 2v為邏輯0,5 ~ 6v為邏輯1。一、上拉電阻1. 應用場景上拉電阻應用在引腳低電平有效的情況。2. 作用為什么在低電平有效的引腳上,要連一個上拉電阻呢?我們希望引腳只有兩個邏輯狀態,即0和1,但如果某低電平有效的引腳不接上拉電阻,它就只有0和未知的狀態:當接低電

2022-01-14 07:37:02

你好。我已經做了一個用于脈沖生成的小型sysgen模型,并用示波器在kintex7開發板的GPIO引腳上觀察該脈沖,但是我在GPIO引腳上獲得的脈沖與我在sysgen中生成的脈沖不匹配。脈沖恰好是硬件上的一半而不是軟件。

2019-10-24 09:41:09

到額外的時鐘脈沖)時,我們在FPGA引腳的GPMC_CLK信號上添加了一個510歐姆的下拉電阻。大大減少了問題但沒有消除它。小電阻應該消除任何串擾。然后,我們在該FPGA引腳處添加了一個220pF電容

2019-08-08 06:49:12

我無法使這部分工作。既然相當簡單。我想知道你的頭頂是什么原因導致輸出不會根據輸入引腳上的電壓而改變(我使用的是上拉電阻)。對我來說,負輸入保持在2.5V,正輸入可以在0V-3V之間,但當我達到

2019-07-26 11:05:36

旁路是把輸入信號中的干擾作為濾除對象,去耦是把輸出信號的干擾作為濾除對象。旁路電容要盡量靠近負載器件的供電電源引腳和地引腳,這樣能夠很好的防止輸入值過大而導致的地電位抬高和噪聲。去耦電容起到一個電池

2019-05-22 08:22:54

P1_5的電平就會跳變導致電機自動打開,我在引腳外接了一個上拉電阻都沒用,我現在懷疑是板子內部電壓變化引起的引腳上電平的跳變,求教各位大神怎么樣才能保持引腳上電平的穩定,先在此謝過了~

2015-09-05 11:25:53

IAM使用PIC32 MX795F512LMI設備I/O與MIL連接器引腳連接,能幫助我計算I/O引腳上的輸出電壓嗎? 以上來自于百度翻譯 以下為原文 Iam using

2019-04-18 06:14:54

你好..我正在嘗試使用 pulseIn 函數讀取 D0 引腳上的脈沖..不幸的是,它給了我零..我做了一些研究,發現這個函數只適用于 D3,D4 引腳..是否可以工作與其他引腳?(代碼:全選

2023-02-28 08:41:35

改變FMC的Vadj引腳上的電壓?2.我可以通過以下方法更改FMC的電壓:TI數字電源控制器軟件,以及UC90120A電源序列發生器和監視器的編程

2019-09-29 12:03:24

我正在用PIC18F45 K20工作。我有一個板與外部振蕩器連接到RA2。這并不打算是一個校準引腳,但我被要求一些如何計數這個引腳上的振蕩。我可以將外部振蕩器配置為時鐘RA2,但我很困惑如何在RA2

2019-11-04 10:51:45

引出,電路圖中一般在輸出引腳旁標注“OUT”字符。其輸出引腳的外電路特征是:通過電容、電阻、變壓器等耦合元件與后續電路的輸入端連接或者直接驅動揚聲器、發光二極管、指示表頭等負載,如下圖所示: 跟

2021-03-16 10:46:38

我需要一些關于我正在考慮的項目的建議。我們家里有一個使用油的舊加熱器,我認為看看它運行/燃燒多少會很酷。所以我取下它的燃燒器蓋,發現在它的診斷連接器上的兩個引腳上,它在運行時發出了大約 3v 的電壓

2023-02-24 08:34:24

大家好,我使用的是DSPIC33 FJ256MC710A DSP。我無法理解如何選擇IO引腳上的上拉或下拉電阻。我查閱了數據表,它指出:可選擇的開放漏極、上拉和下拉。在輸入輸出引腳的參考指南中,我

2019-08-07 14:05:23

,且寄生參數越大,振蕩的幅度也越大,甚至損壞開關管。該高頻振蕩會通過SW節點與輸出VOUT之間的寄生電容耦合到輸出電壓,也就是輸出電壓中的高頻噪聲。圖1. Buck電路的寄生參數第二部分:輸出電壓噪聲

2022-11-07 08:01:47

親愛的艾莉最近得到了MPLAB XPress評估板。我正在尋找一個代碼示例來讀取模擬引腳上的電壓。有什么幫助嗎?許多感激的安東尼奧 以上來自于百度翻譯 以下為原文 Dear all I have

2019-04-28 07:38:41

【說明】程序將CAN引腳重映射到了PD0和PD1引腳上。由于打開了Loopback模式,所以這兩個引腳不需要接任何器件,懸空就行。必須要設置CAN消息過濾寄存器(CAN filter

2021-08-19 08:47:15

將輸入引腳的狀態反映到輸出引腳上的高效、低延遲方式是什么?有什么比將輸入引腳配置為 EXTI 更自動化,然后在中斷處理程序中讀取它并相應地設置輸出引腳的狀態?可以用比較器或定時器來完成嗎?

2023-01-10 07:01:07

下面是配置字設置和其他電阻設置。我已經配置RA5引腳作為輸出。上拉電阻禁用。但是它仍然在RA5引腳上產生5V輸出(它隨機產生,并不總是,有時工作正常,有時產生假電壓)。#pragma config

2020-03-17 10:38:12

嗨,伙計們,我需要檢測引腳上是否有電壓。我不需要測量精確的電壓。只需要知道它是否接通。我應該使用模擬端口,還是數字端口就足夠了?謝謝!秋子

2019-09-27 12:29:28

我想在LCD引腳上移動數據,它連接在PIN號12、13和15端口上,將為PORTB提供邏輯工作,引腳0到7,然后12到15引腳。我使用的是P24FJ64 GC010控制器 以上來自于百度翻譯 以下

2019-03-20 08:56:36

引腳上面出現了如圖的綠叉,網上查了說設置最小間距,但是我改了0也沒用,甚至兩個電阻電容之間的互聯也有這種問題另外再問一個相關的,我用的芯片引腳間距可能阻焊層比較近,一開始都是綠的,經測試要7mil間距一下這些引腳才能正常,但是我的連接線要10mil,會不會有什么問題

2019-08-05 01:25:33

什么是I/O和控制引腳上的總注入電流?所有I/O和控制引腳上的總注入電流的值是多少?

2021-10-15 09:36:08

我無法在INT2引腳上產生中斷。但我可以在INT1引腳上生成具有相同配置的中斷。好像我錯過了一些明顯的東西,或者數據表缺少一些關鍵的東西!我試圖從Z軸檢測180度翻轉。在平坦的表面上,Z軸向上指向

2019-04-16 13:33:16

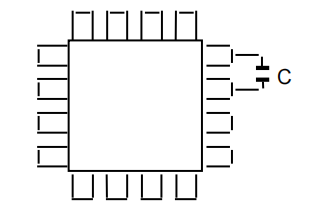

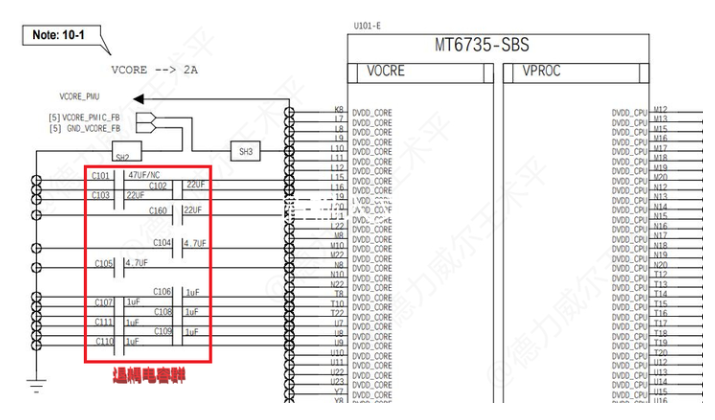

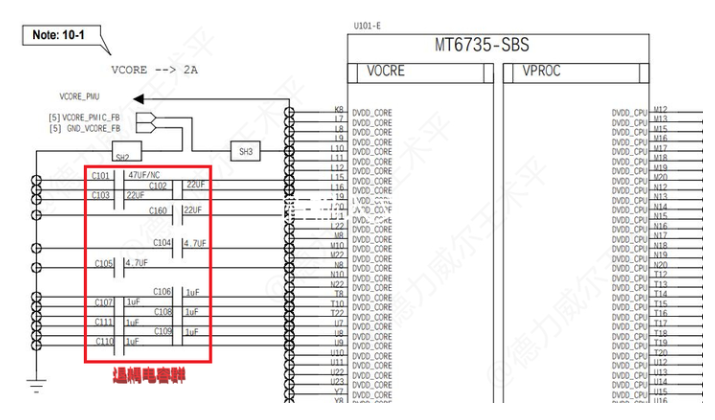

dsp中的電源引腳一般是要加電容(如:5510的N6、N10等),是不是它的每一個電源引腳都有加一個電容如果不是,如何確定要加幾個電容,以及在芯片的那幾個引腳上加?

2023-06-19 08:19:37

器件繪制2MA和一個繪制1Ma的SPI器件,當它們連接到IO引腳時,IO引腳電壓下降到大約2.8伏。I2C線和SPI線連接到PIC,PIC為其供電。當I2C設備在沒有SPI設備的情況下供電時,電壓

2018-12-26 16:05:54

的耦合嗎?還有,是不是電源噪聲會對控制電壓線有干擾從而造成頻率抖動呢??我全都不是很確定,所以來這里求證,順便還望高人能夠補充,減小電源噪聲影響的措施有哪些呢?看到論文上說全差分可以減小電源噪聲

2021-06-24 06:11:40

你好。A 有我的帶有 STM32G431CBU 微控制器的定制板。我板上的電源域如圖所示:我想測量 Vref+ 引腳上的電壓。CubeMX的模擬域設置為:單ADC采集代碼:HAL_ADC_Start

2023-01-05 08:14:35

請教大神,靠近芯片的哪些電容應該貼近芯片引腳,還有去耦,濾波,旁路,耦合電容怎么區分,各有什么特點

2016-08-04 22:55:31

嗨!我用zc706板。我需要訪問zync-7000的可編程邏輯中的uart(tx和rx)引腳。配置處理系統以便在emio引腳上檢索uart的步驟是什么?如果我是對的,那么我可以通過使用EMIO將UART數據通過UART1指向PL。考慮到我有ZC706板,有人可以詳細解釋如何這樣做嗎?謝謝芭芭拉

2019-09-20 11:30:59

請問: 我們選用了貴公司的檢波芯片AD8319,有幾個問題想咨詢下. 我們自身產品分別工作在1-30M 及 30-2700MHz兩個頻段,問下Tadj引腳上分別應接多大電阻比較合適.另,CLPF引腳的電容值應該選多大的? 謝謝!

2018-09-21 14:24:11

如題,我有一個板在Vbat引腳上串一個電阻后接到紐扣電池,檢查時發現引腳電壓總是4V多,高于電池的3V,以為是電池問題,后來斷開電阻一量,還是有4V電壓,也就這個電壓是從芯片內部出來的,不是電池的電壓,想請教一下,這個Vbat引腳不是從外部供電的嗎?沒供電時為何還有電壓呢?

2023-06-26 08:18:29

為了使ADC或DAC具有更好的性能,是否應在VREF 引腳接電容?

2019-08-08 04:11:38

此款芯片有一個COMP腳,應該是調整頻率誤差的,但是不知道這個引腳上的電阻電容大小是怎么確定的,求助!

2019-07-03 08:10:19

親愛的ALI AM使用PIC16(L)F1526/ 7,從數據表看來,我不能下降-0.2V,-20mA。我想知道如果我用一個電壓:-2.047V,802.6uA-7.946mV,3.11uA-640mV,251.0u來插入一個輸入引腳會發生什么,非常感謝你的幫助。

2019-10-25 10:45:05

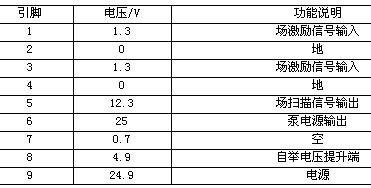

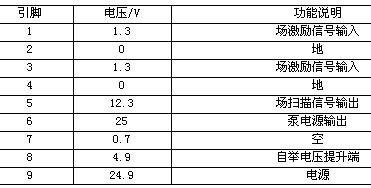

tda9859各引腳功能圖及引腳電壓

2008-01-16 14:04:49 60

60 TDA8361引腳功能圖及引腳電壓Q�D�j!D�Q-q9Z�N u Q�[腳號 電壓/V 引腳

2008-01-16 13:08:48 25841

25841 tda9373各引腳功能圖及引腳電壓

TDA9373是超大規模解碼、微處理集成電路,其內部包含微處理器、圖象中放、伴音中

2008-01-16 13:34:18 26289

26289 TDA9383各引腳功能圖及引腳電壓

引腳 電壓(V) 功能 說明

1 4/0 待機/開機控制

2 4 總線時鐘線

2008-01-16 13:37:43 28838

28838 tda4661引腳功能圖與引腳電壓

2008-01-16 21:58:29 1413

1413

TDA4555引腳功能圖與引腳電壓

2008-01-16 22:00:38 1350

1350

TDA3536各引腳功能圖與引腳電壓

2008-01-16 22:07:03 1900

1900

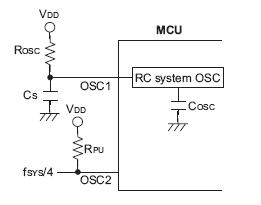

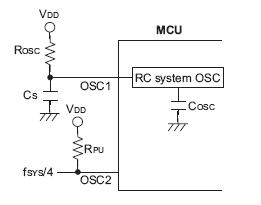

單引腳上拉電阻型RC振蕩器

以下是外接上拉電阻的RC振蕩器電路。

2008-10-24 16:03:11 1209

1209

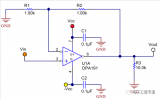

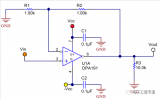

較長的走線路徑可以作為電線,讓高頻噪聲耦合進信號鏈。倒相引腳上的PCB電容會引發穩定性問題。因此,倒相引腳上的接點應該越小越好。將R1和R2移至引腳2旁,可以讓負荷電阻器R3旋轉180度。

2017-11-28 10:29:03 9073

9073

迄今為止,大多數 NEC 的微控制器封狀都有相鄰電源引腳。這引腳使 PCB 設計者能更輕易地減少微控制器與退耦電容之間的電流環路面積,當然,要最小化環路面積,每相鄰電源引腳對之間要有一個電容。不僅降低了環路面積,也減少了退耦電容的連接阻抗。

2022-08-16 09:10:52 1300

1300

補償 NCP1250 OPP 引腳上的負電壓尖峰

2022-11-15 19:51:47 0

0 如何測量 SLA 引腳上的 Bemf

2022-11-15 20:21:59 0

0 555的5引腳為什么接0.01微法的電容?? 555集成電路是一種非常常用的定時器或多諧振器。電路中的引腳分布優雅,引腳的詳細說明為: 1. GND: 接地引腳 2. TRIG: 觸發器輸入 3.

2023-09-13 18:21:27 1264

1264 不斷變革創新,就會充滿青春活力;否則,就可能會變得僵化。——歌德干貨時間來了,關注小欣本期分享,我們一起來學習吧!連接器引腳上錫不良主要表現為引腳下表面與焊點相接不良或不相接,那么導致失效的原因究竟

2023-12-16 08:03:06 494

494

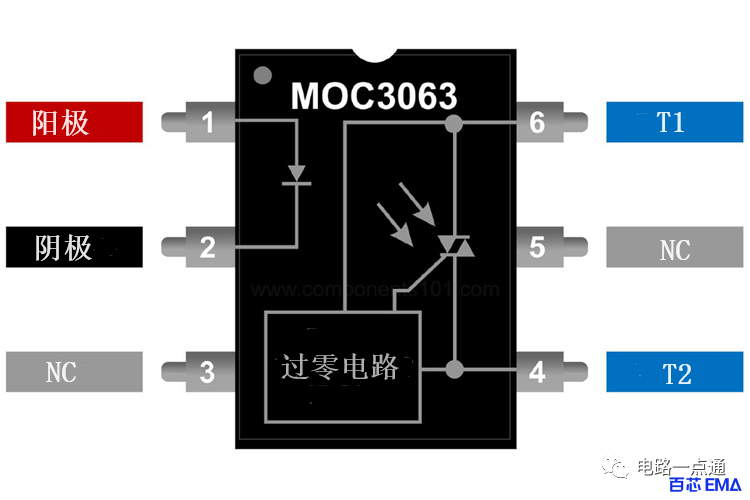

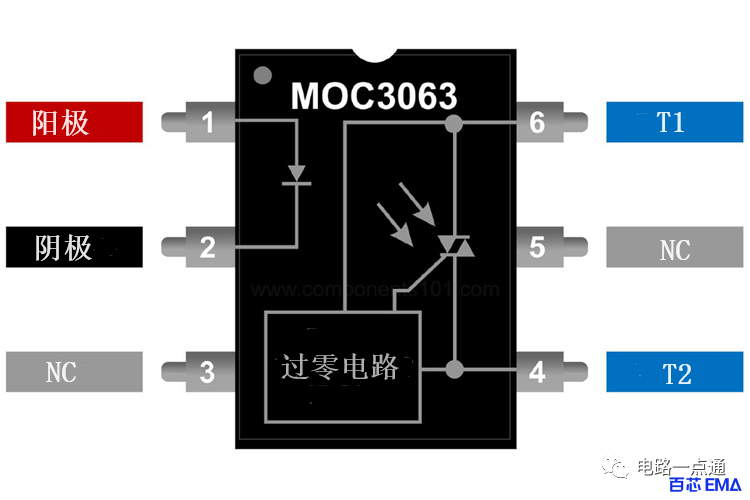

在電子世界中,光耦合器扮演著信息傳遞的使者角色,而MOC3063便是其中一種高效的光耦合隔離器。它由一個發光二極管(LED)和一個單片硅檢測器組成,利用光來傳遞信號,同時提供電氣隔離以防止高電壓

2024-02-16 10:35:00 677

677

去耦電容Q從英文角度看就是連接的意思,那么從電容是上分析就是一個器件事物與另一個器件有練習,當其中一個器件發生改變同時也引起另一個器件信號發生改變,我們把這個關系稱之為“耦合“。

2024-02-18 15:36:02 153

153

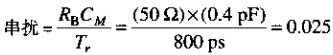

計算由電路1傳入電路2的串擾百分比:串擾=R2CM/T10%-90%

計算由電路1傳入電路2的串擾百分比:串擾=R2CM/T10%-90%

電子發燒友App

電子發燒友App

評論