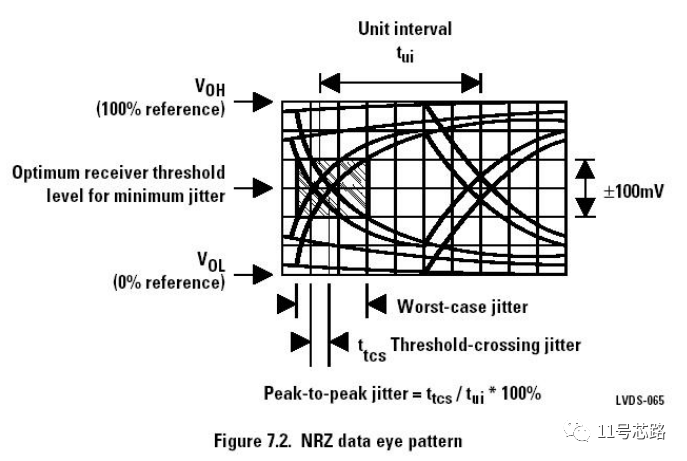

LVDS是一種低擺幅的差分信號技術(shù),它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅(qū)動輸出實現(xiàn)了低噪聲和低功耗。

2023-10-02 16:44:00 591

591

新系列,專門用于實現(xiàn)多點電纜或背板應用。它不同于標準的LVDS,提供增強的驅(qū)動電流,以處理多點應用中所需的雙重傳輸。BLVDS具備大約250mV的低壓差分信號以及快速的過渡時間。這可以讓產(chǎn)品達到自

2016-04-15 16:13:33

Low Voltage Differential Signaling,英文簡稱:LVDS,中文全稱:低壓差分信號技術(shù)接口,是一種為了克服TTL電平方式傳輸寬帶高碼率數(shù)據(jù)時功耗大、EMI電磁干擾等缺點

2020-12-29 13:46:50

晶帆電子【CBEC】: 低壓差分信號傳輸晶體振蕩器(LVDS,LV-PECL輸出),頻率范圍:30MHz~2000MHz;工作電壓:1.8V,2.5V,3.3V,Low JitterSTM32專用

2012-10-13 13:34:13

的CLOCK等要求等長的匹配要求是+/-10mils之內(nèi)。誤區(qū)三:認為差分走線一定要靠的很近。讓差分走線靠近無非是為了增強他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消對外

2016-09-22 09:06:56

什么是差分信號差分信號與單端信號的區(qū)別差分信號的優(yōu)點差分信號在做pcb設計時的處理方法

2021-03-03 07:09:27

什么是差分信號差分信號與單端信號的區(qū)別差分信號的優(yōu)點差分信號在做pcb設計時的處理方法

2021-01-28 06:01:01

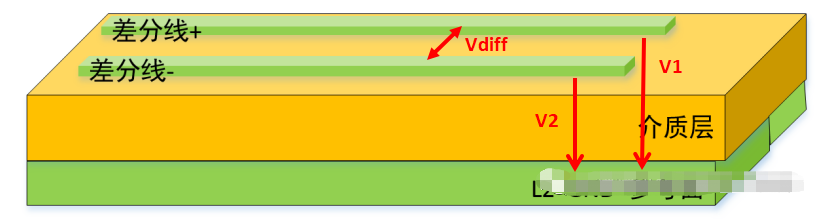

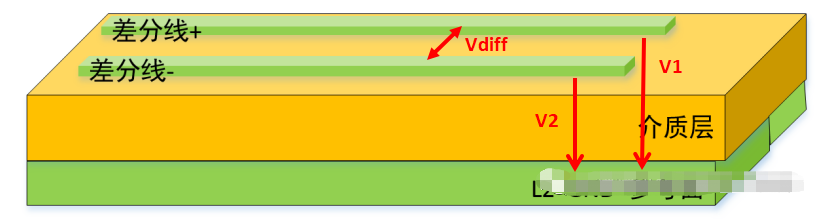

對差分信(VDS)號而言,對其影響最大的因素是它們的對地阻抗是否一致,也就是對地平衡度,它們之間相對的阻抗影響并不特別重要,之間分布電容大了只會衰落信號強度,不會引入噪聲和干擾,也就是對信噪比不會

2019-05-31 08:23:03

差分信號布線時信號完整性問題;影響SI的因素;解決問題的設計辦法;

2016-09-07 11:25:46

差分信號是指使用兩根信號線傳輸一路信號,依靠信號間電壓差進行判決的電路,既可以是模擬信號,也可以是數(shù)字信號。實際的信號都是模擬信號,數(shù)字信號只是模擬信號用門限電平量化后的取樣結(jié)果。因此差分信號對于

2022-01-20 08:19:47

分信號的CLOCK等要求等長的匹配要求是+/-10mils之內(nèi)。誤區(qū)三: 認為差分走線一定要靠的很近。讓差分走線靠近無非是為了增強他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消

2016-09-29 11:27:50

在本文中,我們將探討差分信號的優(yōu)勢以及這些優(yōu)勢如何對您的高速設計產(chǎn)生積極影響。TTL、CMOS 以及其更低電壓的同類 LVTTL 與 LVCMOS 等單端信號都是數(shù)字電路設計中的常用技術(shù)。然而

2022-11-22 06:07:48

降低。LVPECL 和 CML 差分信號具有更高的輸出電壓擺幅,因此功耗比 LVDS 及 M-LVDS 信號略高。差分信號傳輸?shù)牡诙€優(yōu)勢在于共模噪聲抗擾度。由于差分信號由幅值相等、極性相反的正負信號

2018-09-17 16:34:43

在高速 PCB 設計中,差分信號的應用越來越廣泛,這主要是因為和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優(yōu)勢。作為一名(準)PCB 設計工程師,我們當然需要充分理解差分信號!

2021-02-05 07:27:44

如果接一路差分信號是不是用信號源雙路信號分別接差分的IQ端,然后剩下的黑線都接地線,并且信號源設置雙端信號輸出,并且信號反向?那如果接雙路差分信號呢?一個信號源夠用嗎?

2017-03-01 12:06:47

導線來替代單根導線,增加了任何相關接口電路的復雜性。那幺差分信號提供了什幺樣的有形益處,才能證明復雜性和成本的增加是值得的呢?差分信號的第一個好處是,因為你在控制'基準'電壓,所以能夠很容易地識別小信號

2009-09-06 08:58:06

下載資料需要積分,怎樣才能增加積分?

2019-12-12 09:23:32

怎樣才能學好arduino?

2015-11-13 21:26:35

選為2.5V,如下圖所示:然后我們?nèi)タ碔/O Standard的下拉列表,根本就沒有Bus LVDS的選項,也就是說,沒有辦法把這個信號定義為差分信號。如果我們先定義I/O Standard為Bus

2018-09-03 11:08:41

大家好假設我有一個IO信號Ain verilog設計。我想用它來使用差分信號標準LVDS。我是否必須在我的verilog代碼中使用IOBUFDS?或者有一種更簡單的方法,只需在ucf中將A設置為

2019-01-18 07:03:58

電路顯示兩個系列堿性電池經(jīng)過調(diào)節(jié),提供1.8V電源,充分利用了LTC3035卓越的壓差特性

2019-08-02 08:45:14

5V 電源操作時,經(jīng)常就會出現(xiàn)這種情況。 當不采用單端信號而采取差分信號方案時,我們用一對導線來替代單根導線,增加了任何相關接口電路的復雜性。那幺差分信號提供了什幺樣的有形益處,才能證明復雜性和成本

2019-05-31 08:01:24

為何要隔離 LVDS(低壓差分信號傳輸)?

2020-12-23 07:45:02

對處于惡劣環(huán)境中的外部接口需要予以電流隔離,以增強安全性、功能性或是抗擾能力。這包括工業(yè)測量和控制所用數(shù)據(jù)采集模塊當中的模擬前端,以及處理節(jié)點之間的數(shù)字接口。低壓差分信號傳輸(LVDS)是一種在更高

2018-11-01 10:49:03

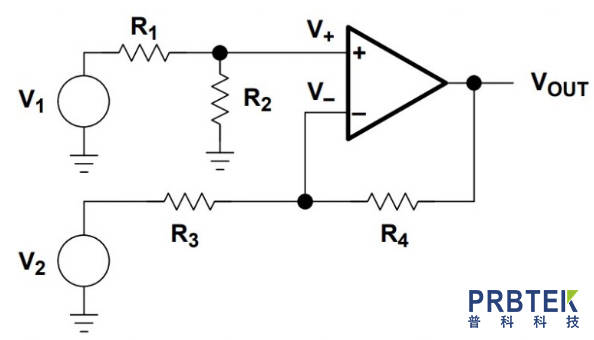

什么是差分信號?為什么要用差分信號?差分放大電路的基本結(jié)構(gòu)和作用差分放大電路的應用電路

2021-03-11 08:21:01

一個差分信號是用一個數(shù)值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統(tǒng)里,系統(tǒng)'地'被用作電壓基準點。當'地'當作電壓測量

2016-07-14 14:56:43

一個差分信號是用一個數(shù)值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統(tǒng)里,系統(tǒng)'地'被用作電壓基準點。當'地'當作電壓測量

2016-07-14 09:48:32

你知道什么是差分信號嗎?一個差分信號是用一個數(shù)值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統(tǒng)里,系統(tǒng)'地'被用作電壓

2016-08-19 11:35:46

單端信號和差分信號會有差異嗎? 他們有何差異,還有在數(shù)據(jù)傳輸中 為什么使用LVDS或M-LVDS?

2021-03-09 08:40:24

嗨,我需要在XC7K325T FPGA中充分利用GTX資源。結(jié)果,我必須以這種方式使用一個四邊形,它的兩個頻道應該服務于10Gb / s鏈路和另外兩個--1Gb / s鏈路。這意味著,兩個通道必須

2020-07-22 13:25:20

基于LTC4410的USB兼容充電器充分利用USB輸入提供的電源。當USB存在時,USB直接支持系統(tǒng)負載。這允許系統(tǒng)負載最大2.5W

2020-06-17 10:25:53

,光纖配線箱為各種應用提供了更豐富的功能和更靈活的布線環(huán)境。選擇正確的光纖配線箱,充分利用光纖配線箱至關重要。下面我將告訴大家如何在數(shù)據(jù)中心里充分利用光纖配線箱,使布線環(huán)境更為靈活。靈活布線中的重要

2016-09-13 15:59:30

電子設計人員使用的工具箱日新月異。要找到適合工作的工具,不僅需要了解手頭上的任務和現(xiàn)有工具,還要知道如何充分利用這些工具。對于設計人員來說,在隔離柵內(nèi)移動信號和電源是一項常見的挑戰(zhàn)。為了提高

2021-12-31 06:42:10

在之前的文章(《如何實現(xiàn)比4G快十倍?毫米波技術(shù)是5G的關鍵》)中我們介紹了如何利用毫米波技術(shù)獲得更多的頻譜資源,接下來的問題是如何充分利用這些頻譜資源——如何讓多個用戶通訊但又互不干擾,專業(yè)術(shù)語叫做頻譜復用。圖片來源:Phoenix

2019-07-11 07:09:25

本文充分利用了低端的FPGA 器件(Field Programmable Gate Array)的靈活性和快速性,實現(xiàn)提取通過不同路徑的同一信號時間差。

2021-05-10 06:35:32

為了解決彈上記錄器和地面測試臺之間高速數(shù)據(jù)流遠距離傳輸問題,提出一種利用低電壓差分信號(LVDS)接口器件實現(xiàn)數(shù)據(jù)遠距離傳輸?shù)脑O計方案。實驗證明該方案傳輸速度達到20 Mh/s,傳輸距離達到300 m,傳輸速度和傳輸距離得到顯著提高。該優(yōu)秀的長線傳輸技術(shù)已成功應用于在某項目中。

2021-04-30 06:02:11

我們可以將LvCmos 2.5 i / o轉(zhuǎn)換為Fpga內(nèi)的差分信令(Lvds)嗎?因為我想使用GTx收發(fā)器,收發(fā)器只接受差分信號..我可以這樣做嗎?你可以幫忙嗎?/

2020-06-16 14:27:26

充分利用磁場的相反極性來抵消對外界的電磁干擾。雖說這種做法在大多數(shù)情況下是非常有利的,但不是絕對的,如果能保證讓它們得到充分的屏蔽,不受外界干擾,那么我們也就不需要再讓通過彼此的強耦合達到抗干擾和抑制

2018-09-18 15:55:05

在開關電源轉(zhuǎn)換器中,如何充分利用SiC器件的性能優(yōu)勢?

2021-02-22 07:16:36

如題,需要一個差分信號輸入仿真,不知道怎么產(chǎn)生差分信號。。。。

2012-11-28 14:48:55

分對組成。我選擇其中一個并在AB7引腳上設置輸出。我收到的信號不是差分信號,而是單端信號。我該怎么做才能產(chǎn)生差分信號?

2020-08-07 06:27:32

應用進行靈活處理。 3、認為差分走線一定要靠的很近。讓差分走線靠近無非是為了增強他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消對外界的電磁干擾。雖說這種做法在大多數(shù)情況下是非

2017-03-02 10:58:00

。 3、認為差分走線一定要靠的很近。讓差分走線靠近無非是為了增強他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消對外界的電磁干擾。雖說這種做法在大多數(shù)情況下是非常有利的,但不是絕對

2017-11-19 13:45:25

讓你的內(nèi)存每秒都能充分利用:內(nèi)存釋放專家

2009-06-01 18:45:26

對處于惡劣環(huán)境中的外部接口需要予以電流隔離,以增強安全性、功能性或是抗擾能力。這包括工業(yè)測量和控制所用數(shù)據(jù)采集模塊當中的模擬前端,以及處理節(jié)點之間的數(shù)字接口。低壓差分信號傳輸(LVDS)是一種在更高

2019-07-23 07:27:54

要靠的很近。實際上,讓差分走線靠近無非是為了增強他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消對外界的電磁干擾。雖說這種做法在大多數(shù)情況下是非常有利的,但不是絕對的,如果能保證讓它們

2018-07-20 16:48:38

怎樣將單端信號轉(zhuǎn)換成差分信號呢?變壓器有哪些最優(yōu)匹配方法?如何改善ADC的增益平坦度并保持它的動態(tài)性能呢?

2021-04-22 06:35:25

可能實現(xiàn))L2RAM和SHRAM的地址都不是連續(xù)的……怎樣才能最為充分的利用這384KRAM呢?求大神探討一下~

2019-06-12 07:15:20

請問一下怎樣才能充分發(fā)揮FPGA浮點IP內(nèi)核的優(yōu)勢?

2021-04-30 06:49:20

自制膽機怎樣才能出好聲:制作一部電子管機,要想獲得好聲,在線路的設計或選用,元件的搭配,制作工藝和調(diào)校工作等方面都有一定的要求。本文就談談這方面的體會,供焊機者

2009-12-02 15:10:18 98

98 基于低電壓差分信號(LVDS)的高速信號傳輸

2010-12-17 17:21:46 40

40 什么是lvds信號

LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號

2008-10-16 13:49:11 7845

7845 LVDS差分信號抗噪特性

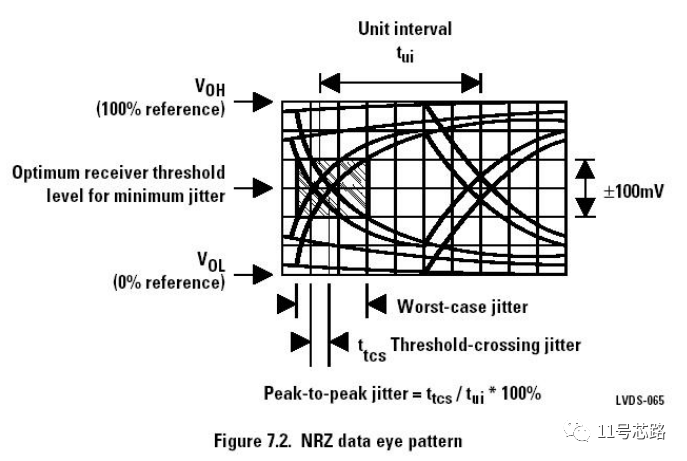

從差分信號傳輸線路上可以看出,若是理想狀況,線路沒有干擾時,在發(fā)送側(cè),可以形象理解為:

2008-10-16 13:53:16 1508

1508 摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-04-24 16:05:19 1274

1274

摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-05-01 11:14:27 1655

1655

充分利用MAXQ®處理器的非易失存儲服務

摘要:需要非易失數(shù)據(jù)存儲的應用通常都需要使用外部串行EEPROM。這篇文章介紹了僅使用MAXQ微控制器中已有的閃存提供非易失

2009-05-02 09:28:54 777

777

筆記本電池——怎樣才能不爆炸?(組圖)

2009-11-10 13:48:51 956

956 魏少軍: 兩岸業(yè)者應充分利用歷史機遇加緊合作

前大唐微電子總經(jīng)理、董事長魏少軍盡管已暫別產(chǎn)業(yè)界投身教職,不過他仍穿梭兩岸產(chǎn)學界,目前亦擔任中國半導體協(xié)

2009-11-20 10:04:05 489

489 怎樣才能使本本達到最優(yōu)性能

問題:我是一個最近購本的菜鳥,請問怎樣才能使本本達到最優(yōu)的性能?

回

2010-01-25 14:39:02 482

482 充分利用 FTP分類賬戶設置經(jīng)驗談

我校建立FTP是在2003年,經(jīng)過一段時間的摸索,F(xiàn)TP服務在我校已經(jīng)很成熟,不但方便了老師、服務了教學,還極大地

2010-01-29 13:50:17 498

498 怎樣才能選擇一張合適的投影幕?

再好的投影機,也需要有好的屏幕,才能投出最佳的投影效果。那么如何選擇才能找到這

2010-02-10 11:01:55 521

521 并行編程無進展使多核芯片未能充分利用

《福布斯》文章指出,為什么應用軟件總是無法充分利用芯片的強大功能呢?如何充分有效地利用處

2010-04-01 16:43:43 614

614 充分利用太陽能電池節(jié)省光熱費

核心提示:要想不花光熱費,不僅需要導入燃料電池,還需要將太陽能電池增至5kW,并積極導入LED照

2010-04-06 08:45:43 582

582 隨著數(shù)字電路數(shù)據(jù)量的提高,數(shù)據(jù)的傳輸速率也越來越快,LVDS(低壓差分信號)標準越來越多的應用在FPGA和ASIC器 件中。文章對LVDS信號的特點進行了分析,說明了PCB設計中差分走線的注意事項并結(jié)合實際應用設計了一塊LVDS接口板。 關鍵詞: LVDS; PCB設計;接口;阻抗

2011-02-23 09:54:03 340

340 一名設計工程師怎樣才能真正充分利用串行I/O的各種技術(shù)呢?在開始設計之前,我們需要知道什么對于實現(xiàn)串行I/O是有益的。我們需要研究一些基于串行設計的單元器件,從而了解一下

2012-04-01 15:01:36 29

29 LVDS,即Low Voltage Differential Signaling,是一種低壓差分信號技術(shù)接口。它是美國NS公司(美國國家半導體公司)為克服以TTL電平方式傳輸寬帶高碼率數(shù)據(jù)時功耗大、EMI電磁干擾大等缺點而研

2012-07-19 16:01:53 5328

5328

簡要介紹提供8kV IEC ESD保護的ADI MLVDS(多點低壓差分信號)收發(fā)器。概要說明MLVDS的應用領域、特性及其與LVDS的比較。

2019-07-05 06:11:00 1987

1987 近年來,在建設智慧城市的過程中,如何充分利用新基建所涵蓋的新技術(shù)來解決城市建設中遇到的各項問題,吸引了全世界智慧城市的建設者和管理者的高度關注。其中,區(qū)塊鏈和人工智能對智慧城市建設和管理的影響尤為重要。

2020-07-22 16:41:36 2257

2257 充分利用超級大寫電腦

2021-05-21 19:04:42 0

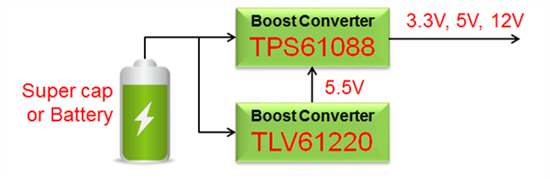

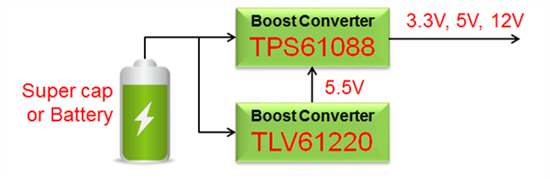

0 對于您的SSD或便攜式系統(tǒng),請通過讓您的超級電容器完全耗盡電能而使其得到充分利用。一種微型低成本升壓轉(zhuǎn)換器可從相同尺寸的超級電容器中汲取30%以上的電能。您還想讓哪些其它系統(tǒng)耗盡所有電能呢?

2022-02-06 09:41:00 1583

1583

LVDS(Low Voltage Differential Signal)即低電壓差分信號。

2022-07-03 15:20:13 2534

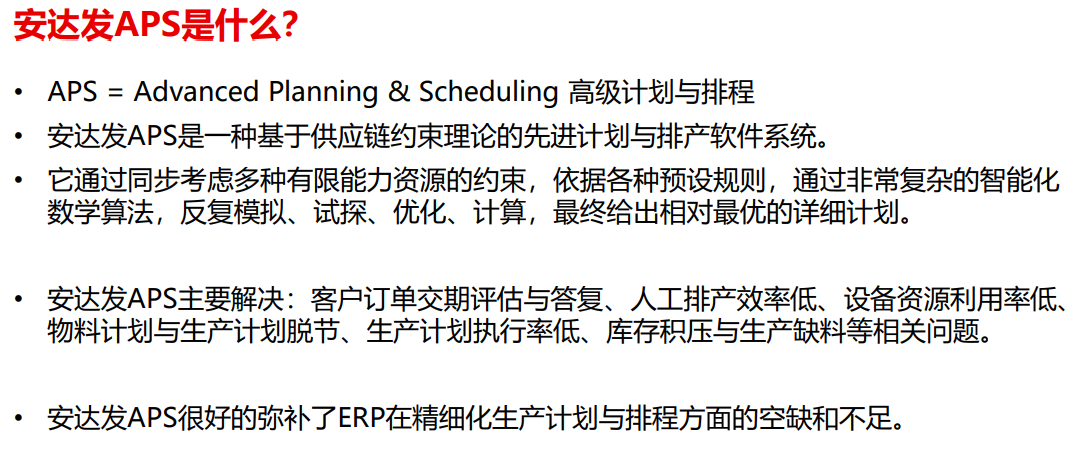

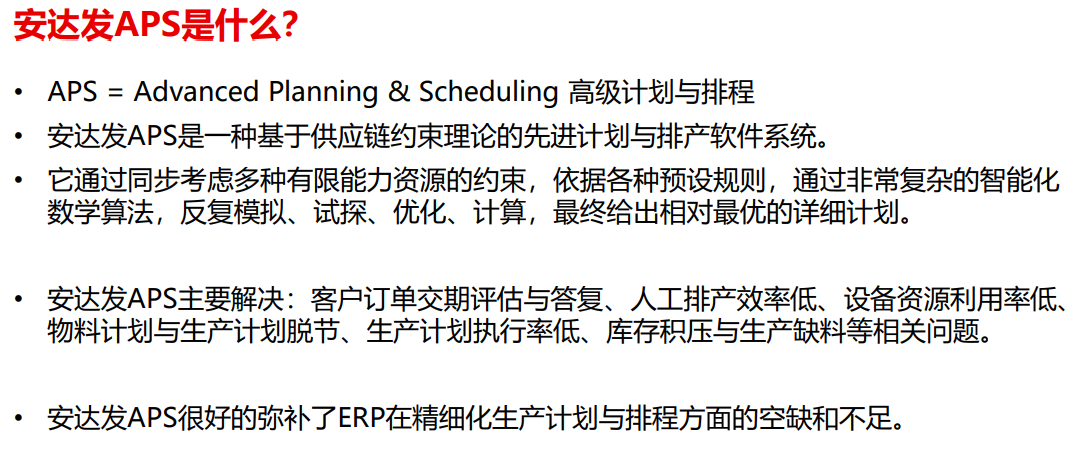

2534 APS排程可以充分利用設備產(chǎn)能,提高設備利用率,減少停機換產(chǎn)損失,實現(xiàn)設備、人員、物料等約束。

2022-10-20 17:09:59 500

500

APS生產(chǎn)排產(chǎn)可以實現(xiàn)生產(chǎn)資源的約束,將生產(chǎn)管理標準化,幫助企業(yè)充分利用設備產(chǎn)能,提高設備利用率,將交期最大準時化。

2022-11-03 17:34:06 520

520

充分利用電位計 — 別讓旋轉(zhuǎn)亂套!

2022-11-07 08:07:15 0

0 使用低壓差分信號的帶電插入

2022-11-14 21:08:29 0

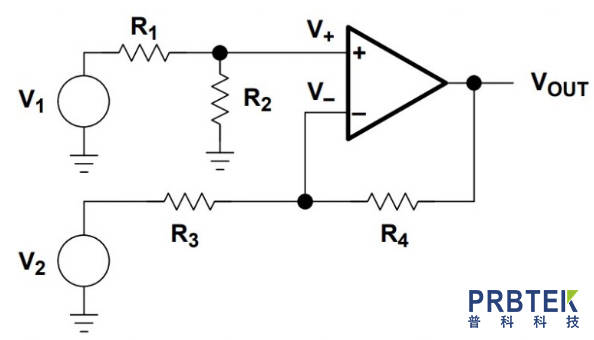

0 差分信號是一種常見的信號形式,它是指由兩個信號之間的差值構(gòu)成的信號。在許多應用中,我們需要處理低壓差分信號,這就要求電路設計者使用帶有低偏置和高共模抑制的差分放大器。

2023-04-03 11:14:55 1285

1285

LVDS (Low Voltage Differential Signaling)是一種小振幅差分信號技術(shù),它使用非常低的幅度信號 (250mV~450mv)通過一對平行的PCB走線或平衡電纜傳輸數(shù)據(jù)是一種專業(yè)的低電壓差分信號

2023-04-06 09:46:43 1289

1289 差分信號是指利用兩個輸出驅(qū)動pin去驅(qū)動兩根傳輸線。這兩根傳輸線,一根傳輸信號,另一根傳輸它的互補信號。接收端看到的信號是這兩條傳輸線上的信號壓差。差分對就是用來傳輸一對差分信號,并且存在耦合關系的傳輸線。例如LVDS就是一種常見的低壓差差分信號。

2023-05-06 16:02:47 6086

6086

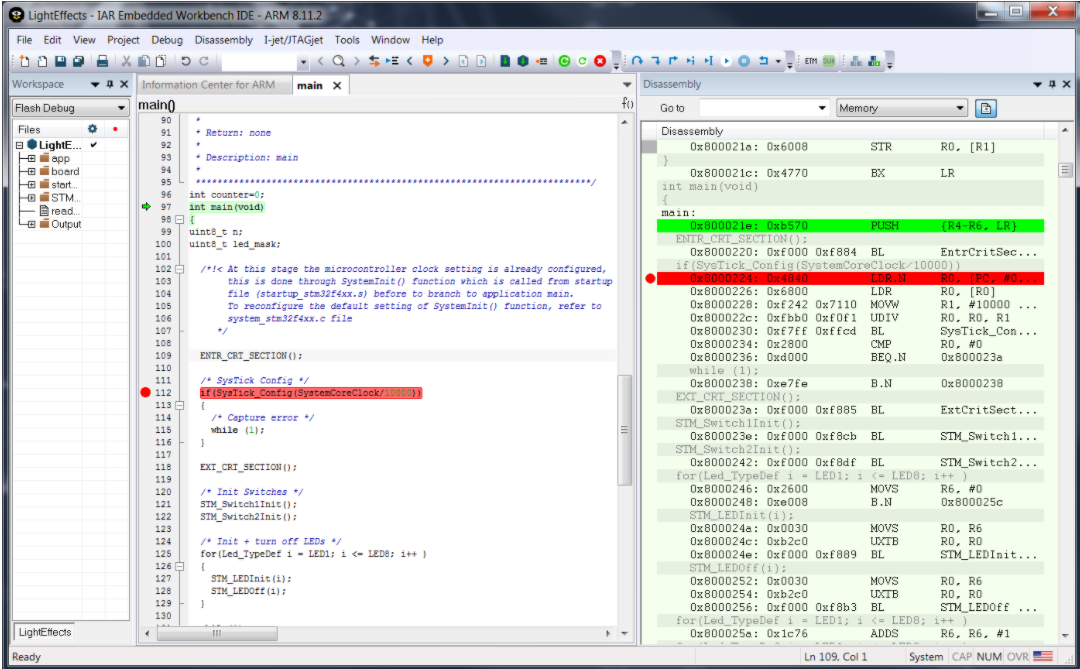

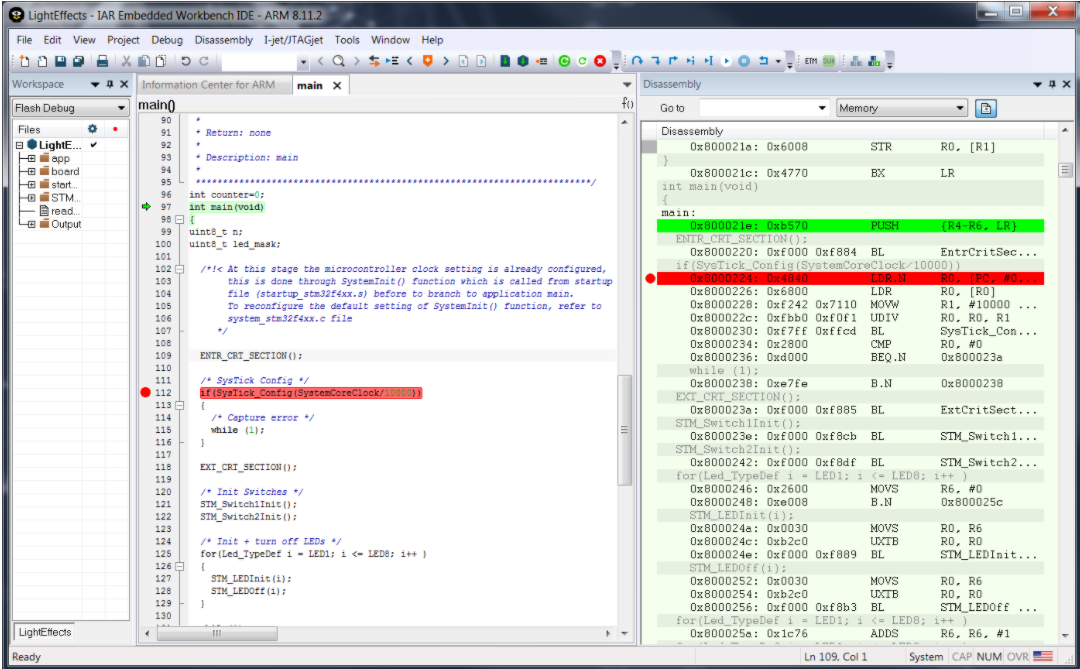

在MCU開發(fā)中如何充分利用各種類型的斷點?

2023-09-18 16:22:34 360

360

差分信號進入ADC芯片,怎樣才能保證兩差分信號自動均衡呢? 差分信號進入ADC芯片時,為了保證兩差分信號自動均衡,可以采取以下措施: 1. 去除共模干擾:共模干擾是指差分信號的兩個輸入端引入的信號

2023-11-09 09:55:38 629

629 如何充分利用單片機(MCU)的非易失性存儲器 單片機(MCU)的非易失性存儲器(NVM)是存儲數(shù)據(jù)和程序的重要組成部分。它可以保留數(shù)據(jù),即使在斷電或復位后也不會丟失。為了充分利用MCU的NVM,我們

2023-12-15 10:10:49 507

507

電子發(fā)燒友App

電子發(fā)燒友App

評論