構建一個4位二進制計數(shù)器,計數(shù)范圍從0到15(包括0和15),計數(shù)周期為16。同步復位輸入時,將計數(shù)器重置為0。

2022-12-02 09:20:28 3111

3111 74LS90是一種常用的二進制計數(shù)器芯片,它可以實現(xiàn)二進制數(shù)的加法或減法計數(shù)。本文將介紹如何使用74LS90設計一個六進制加法計數(shù)器。 74LS90是一種雙時鐘輸入的二進制計數(shù)器芯片,具有異步

2023-12-14 17:30:11 2281

2281 概述:CD4060是一款14級二進制串行計數(shù)/分頻器,它是由一振蕩器和14級二進制串行計數(shù)器位組成,振蕩器的結構可以是RC或晶振電路,CR為高電平時,計數(shù)器清零且振蕩器使用無效。所有的計數(shù)器位均為主從觸發(fā)器。

2021-04-08 07:40:14

如題,LZ采用外部50M時鐘作為輸入,通過PLL鎖相環(huán)分頻得到100K的時鐘。將100K的時鐘作為二進制計數(shù)器的clk.但在SignalTap中發(fā)現(xiàn),采到的數(shù)據(jù)在上升沿變化后,等時鐘維持穩(wěn)定時,數(shù)據(jù)出現(xiàn)了變化。怕自己沒說清楚,附上時序圖和程序

2019-11-28 21:53:14

用二進制計數(shù)器實現(xiàn)控制選擇不同的開關,電路輸入信號為一路方波,當此信號的第一個方波信號輸入時,電路使用開關1,當此信號的第二個方波信號輸入時,電路使用開關2,本人小白,麻煩回答具體點,附上簡單的電路圖,謝謝啦

2017-06-26 09:30:44

這是一個可以對照顯示0~9這10個數(shù)字的二進制和十進制的電路。二進制數(shù)字用4個發(fā)光二極管顯示;它們排成一行,亮表示1,滅表示0。十進制數(shù)字用一個數(shù)碼管表示。數(shù)字的變化采用CD4040組成加法計數(shù)器,手動加1計數(shù)。

2021-04-27 07:21:40

。而絕對式編碼器是直接輸出數(shù)字量的傳感器,它是利用自然二進制或循環(huán)二進制(格雷碼)方式進行光電轉換的,編碼的設計一般是采用自然二進制碼、循環(huán)二進制碼、二進制補碼等。特點是不要計數(shù)器,在轉軸的任意位置

2011-03-08 14:16:59

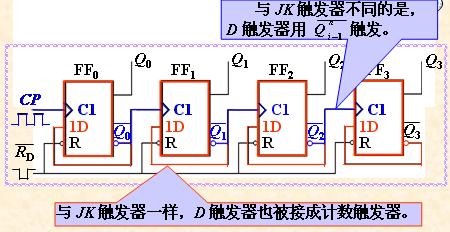

Altera EPM7128SLC84-15,時鐘,四位八段數(shù)碼管。三、實驗內(nèi)容1、用D觸發(fā)器設計異步四位二進制加法計數(shù)器。2、用JK觸發(fā)器設計異步十進制減法計數(shù)器。3、用74161兩個宏連接成八位二進制同步

2009-10-10 11:47:02

; S92 Q2 Q1 GNDT4290(T1290、74LS290、T210),是一個二-五-十進制計數(shù)器,能夠進行二進制、五進制計數(shù)、通過簡單聯(lián)線組成十進制計數(shù)

2008-07-05 13:41:26

我的實訓作業(yè),求各位幫忙設計一個十二進制計數(shù)器,要電路仿真圖設計任務與要求1.每隔1s,計數(shù)器增1。2.用數(shù)碼管顯示計數(shù)值。3. 當定時器遞增到12時,定時器會自動返回到01顯示,然后繼續(xù)計時。我

2013-12-10 11:15:27

我想制作一個以8個LED的形式實現(xiàn)二進制計數(shù)器。該計數(shù)器通過USART發(fā)送一個8位二進制數(shù),并讓8個LED顯示數(shù)字(如果位為0,則指示燈熄滅,當位為1時指示燈亮)。這樣做的最佳方法是什么?

2018-10-08 14:07:42

二進制運算規(guī)則二進制的運算算術運算二進制的加法:0+0=0,0+1=1 ,1+0=1, 1+1=10(向高位進位);二進制的減法:0-0=0,10-1=1(向高位借位) 1-0=1,1-1=0 (模

2019-12-11 17:49:02

嗨,我需要使用LUT設計一個4位二進制上變頻計數(shù)器。我正在嘗試遵循多路復用器方法。任何想法都非常感謝。謝謝小學以上來自于谷歌翻譯以下為原文Hi , I need to design a 4bit

2019-02-14 11:29:07

大家好,由于我是初學者,我盡可能多地嘗試,看看我是否能夠克服編程FPGA的學習曲線。這次我用VHDL實現(xiàn)了一個二進制計數(shù)器。圖書館IEEE;使用IEEE.STD_LOGIC_1164.ALL

2020-03-13 09:16:40

請問各位,同步二進制減法計數(shù)器的狀態(tài)表該怎么畫?之前只做過同步加法和異步減法,現(xiàn)在混淆了,同步減法的次態(tài)是代入特性方程算出來之后再作為下一個初態(tài),還是直接遞減不用算?

2022-11-23 20:44:42

求十二進制 減法計數(shù)器

2013-04-28 14:34:12

④ 構成脈沖分頻器集成十進制計數(shù)器【74LS290】集成十進制計數(shù)器【74LS390】1. 集成四位二進制計數(shù)器【74LVC161】(1) 邏輯符號CR:CR:CR: 異步置0端。優(yōu)先級最高。PE:PE:PE:并行置數(shù)端。次高優(yōu)先級。TC:TC:TC:進位信號。CEP,CET:CEP

2021-07-29 07:20:09

TTL 二進制同步可逆計數(shù)器

2009-08-03 09:05:53 26

26 設計一脈沖異步二進制加1/減1計數(shù)器.電路有一輸入線X,其信號為脈沖.另一信號M是電位,當M=0時,電路為加1計數(shù)器,當M=1時電路為減1計數(shù)器。使用鐘控D鎖存器實現(xiàn)。

2010-09-28 10:30:47 0

0 十進制計數(shù)器

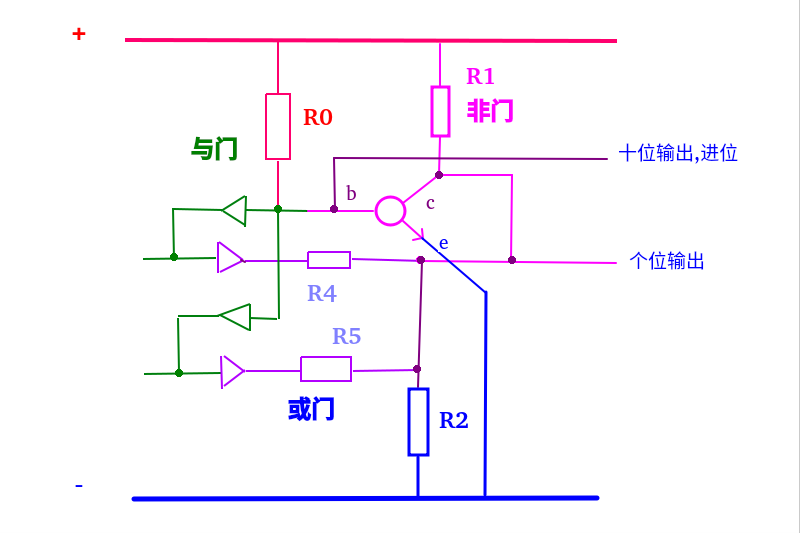

二進制計數(shù)器具有電路結構簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數(shù),特別是當二進制數(shù)的位數(shù)較多時,閱讀非常困難,還

2007-06-20 13:46:05 4188

4188 4位二進制同步計數(shù)器74LS161引腳圖及功能表

4位二進制同步計數(shù)器74LS161

2007-11-22 12:51:59 52149

52149

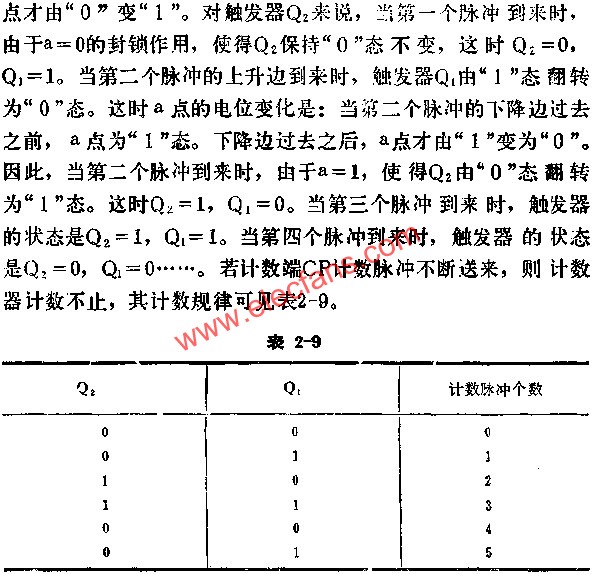

十進制計數(shù)器工作原理

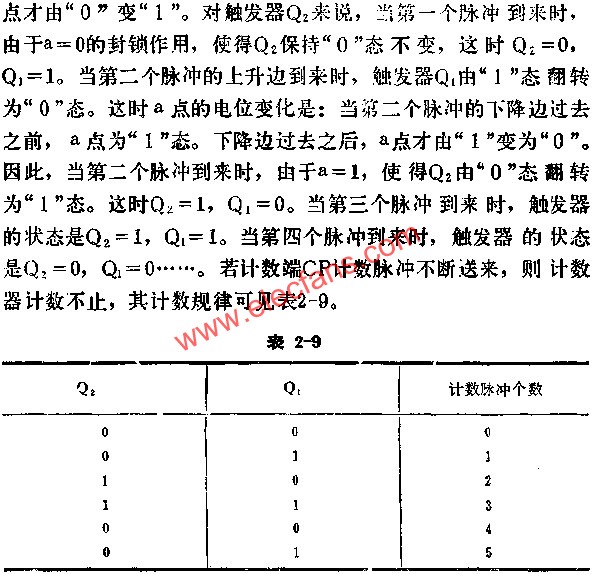

同二進制計數(shù)器相比,十進制計數(shù)器較為復雜。分析步驟一般是:

2008-01-21 13:15:22 28596

28596

兩片4位二進制數(shù)加法計數(shù)器74LS161級聯(lián)成五十進制計數(shù)器。

2009-03-28 10:10:23 34301

34301

第二十五講 同步計數(shù)器

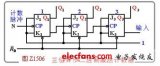

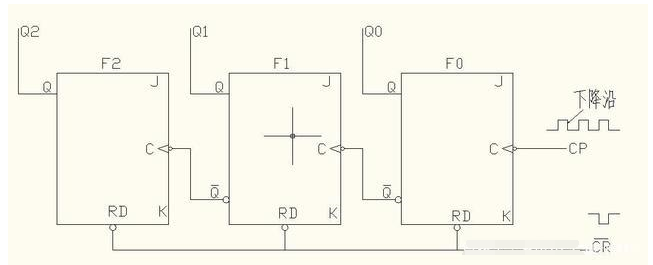

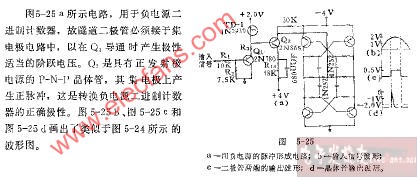

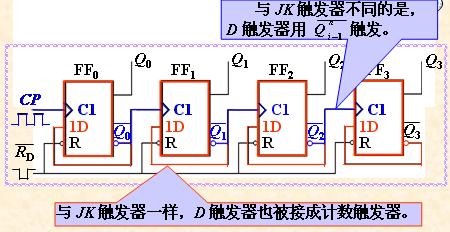

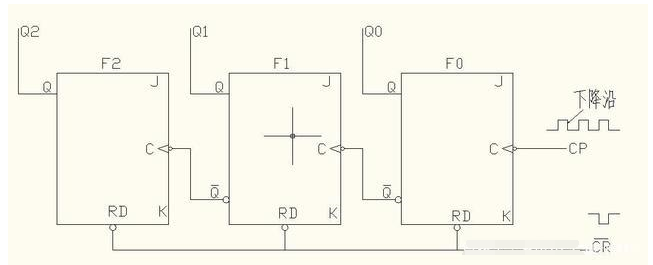

7.3.2 同步計數(shù)器一、同步二進制計數(shù)器1.同步二進制加法計數(shù)器JK觸發(fā)器組成的4位同步二進制加法

2009-03-30 16:28:45 8597

8597

二進制

二進制與十進制的區(qū)別在于數(shù)碼的個數(shù)和進位規(guī)律有很大的區(qū)別,顧名思義,二進制的計數(shù)規(guī)律為逢二進一,是以2為基數(shù)的計數(shù)體制。10這個數(shù)在二進

2009-04-06 23:48:01 7548

7548

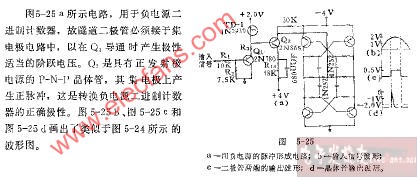

電源二進制計數(shù)器電路圖

2009-06-26 13:16:13 1071

1071

12位二進制計數(shù)器

2009-09-16 15:56:08 6097

6097

異步二進制計數(shù)器

1. 電路構成與工作原理

2009-09-30 18:33:25 13905

13905

同步二進制計數(shù)器

1. 同步與異步二進制加法計數(shù)器比較態(tài)序表和工作波形一樣電路結構不同: 異步二進制加法

2009-09-30 18:37:29 11186

11186

什么是二進制計數(shù)器,二進制計數(shù)器原理是什么?

計數(shù)器是數(shù)字系統(tǒng)中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數(shù),還可以實現(xiàn)

2010-03-08 13:16:34 30352

30352 十進制計數(shù)器,十進制計數(shù)器原理是什么?

二進制計數(shù)器具有電路結構簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數(shù),特

2010-03-08 13:19:54 24108

24108 本的二進制加法/減法器,本的二進制加法/減法器原理

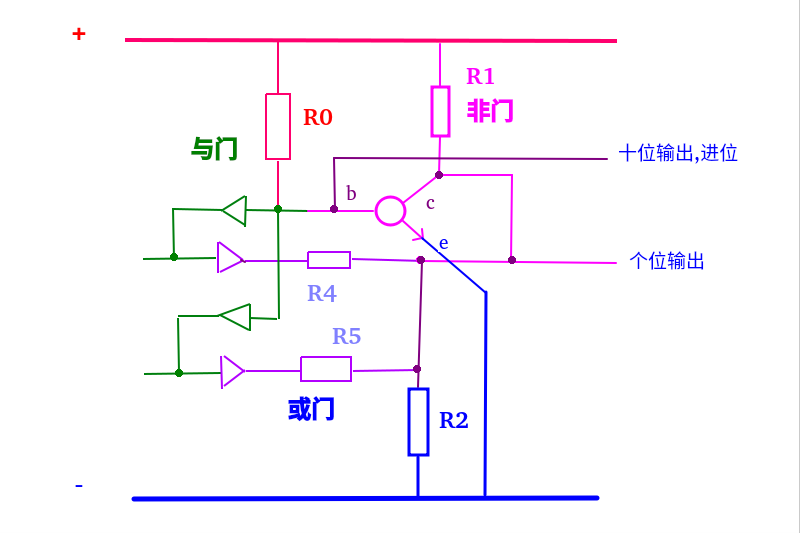

兩個二進制數(shù)字Ai,Bi和一個進位輸入Ci相加,產(chǎn)生一個和輸出Si,以及一個進位輸

2010-04-13 11:11:55 5132

5132 圖中所示是用與非門組成的二進制計數(shù)器,實際上它是用與非門組成的維持-阻塞觸發(fā)器而組成的計數(shù)器.圖

2010-09-19 00:54:13 2416

2416

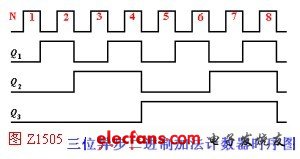

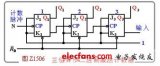

當把圖Z1504中的CP端改接到 端,就構成了如圖Z1506所示的3位異步二進制減法計數(shù)器。令計數(shù)器初始狀態(tài)為000。

2011-04-19 11:33:49 20093

20093

介紹了集成4位二進制計數(shù)器 74LS161 異步置零法構成任意進制計數(shù)器的 Multisim 仿真方案,即以波形方式顯示計數(shù)器的計數(shù)過程、過渡狀態(tài)形成異步置零信號的過程,用四蹤示波器以面板

2011-08-05 14:25:22 336

336 CC4060 由一震蕩器和14 極二進制串行計數(shù)器位組成,震蕩器的結構可以是RC 或晶振電路。CR 為高電平時,計數(shù)器清零且振蕩器使用無效,所有的計數(shù)器位均為主從觸發(fā)器。

2012-03-29 15:01:57 198

198 介紹計數(shù)器的基本原理(如異步,同步二進制計數(shù)器,以及對誤差,性能的分析)

2015-12-17 14:52:39 3

3 二進制加法程序【匯編版】二進制加法程序【匯編版】二進制加法程序【匯編版】二進制加法程序【匯編版】

2015-12-29 11:02:06 0

0 二進制加法程序【C語言版】二進制加法程序【C語言版】二進制加法程序【C語言版】二進制加法程序【C語言版】

2015-12-29 11:03:51 0

0 二進制加法程序【C語言+匯編版】,多種集合,符合同時愛好C語言+匯編的學習者的胃口。

2016-01-06 11:10:18 0

0 Harris CD74HC4020和CD74HCT4020為14級紋波進位二進制計數(shù)器。所有計數(shù)器級都是主從觸發(fā)器。階段狀態(tài)提前一次計數(shù)每個輸入脈沖的負時鐘轉換;a高MR線上的電壓水平將所有計數(shù)器重置為零狀態(tài)所有輸入和輸出都經(jīng)過緩沖。

2022-07-10 10:25:33 12

12 SAR開關時序的非二進制結構

2017-04-05 16:08:27 5

5 基于VHDL的EDA實驗---3位二進制計數(shù)器

2017-11-08 17:45:53 1

1 二進制加計數(shù)器

2017-11-24 14:31:30 6

6 本文主要介紹了74LS161集成計數(shù)器電路(2、3、4、6、8、10、60進制計數(shù)器)。74LS161是4位二進制同步計數(shù)器,該計數(shù)器能同步并行預置數(shù)據(jù),具有清零置數(shù),計數(shù)和保持功能,具有進位輸出

2018-01-18 10:56:39 353115

353115

CD4040組成加法計數(shù)器,手動加1計數(shù)。

2.二進制與十進制數(shù)字對照顯示實驗 本電路可以形象地顯示0~9的二進制數(shù)。按動加1按鈕AN2,計數(shù)器的輸入端CP得到一個負脈沖信號,計數(shù)器進行

2018-09-20 18:26:41 2326

2326 二進制加法器是半加器和全加法器形式的運算電路,用于將兩個二進制數(shù)字加在一起.

2019-06-22 10:56:38 24316

24316

PLC實例講解之計數(shù)器值以二進制輸出資源下載

2021-04-01 16:59:27 22

22 該計數(shù)器是一個3位二進制異步減法計數(shù)器,它與前面介紹過的3位二進制異步加法計 數(shù)器一樣,是由3個JK觸發(fā)器組成,其中J、K端都懸空(相當于J=1、K=1),兩者的不同 之處在于,減法計數(shù)器是將前一個觸發(fā)器的Q非端與下一個觸發(fā)器的CP端相連。

2021-04-18 11:19:47 16340

16340

將二進制數(shù)視為元胞自動機可能有助于數(shù)字二進制計數(shù)器的設計和實現(xiàn)嗎?

2022-07-28 11:47:10 1181

1181

電子發(fā)燒友網(wǎng)站提供《STEM項目之構建基于繼電器的二進制計數(shù)器.zip》資料免費下載

2022-10-18 09:19:35 0

0 帶輸出寄存器的8位二進制計數(shù)器;三態(tài)-74HC590

2023-02-09 21:57:18 2

2 雙二進制計數(shù)器-HEF4520B_Q100

2023-02-10 18:33:54 0

0 雙二進制計數(shù)器-HEF4520B

2023-02-10 18:34:09 0

0 12級二進制紋波計數(shù)器-HEF4040B_Q100

2023-02-15 18:40:02 1

1 12級二進制紋波計數(shù)器-HEF4040B

2023-02-15 18:40:14 0

0 14級二進制計數(shù)器-HEF4020B_Q100

2023-02-15 18:41:58 0

0 14級二進制計數(shù)器-HEF4020B

2023-02-15 18:42:12 0

0 14 級紋波進位二進制計數(shù)器/除法器和振蕩器-HEF4060B_Q100

2023-02-15 18:53:56 0

0 14 級紋波進位二進制計數(shù)器/除法器和振蕩器-HEF4060B

2023-02-15 18:54:07 1

1 雙 4 位二進制紋波計數(shù)器-74HC_HCT393

2023-02-15 18:58:50 0

0 雙 4 位二進制紋波計數(shù)器-74HC_HCT393_Q100

2023-02-15 19:05:13 0

0 可預置同步4位二進制計數(shù)器;異步復位-74LVC161

2023-02-15 19:23:09 0

0 可預置同步 4 位二進制向上/向下計數(shù)器-74HC191

2023-02-15 19:39:04 1

1 帶振蕩器的 14 級二進制紋波計數(shù)器-74HC_HCT4060

2023-02-15 19:39:20 0

0 帶振蕩器的 14 級二進制紋波計數(shù)器-74HC_HCT4060_Q100

2023-02-15 19:39:32 0

0 可預置同步 4 位二進制向上/向下計數(shù)器-74HC_HCT193_Q100

2023-02-15 19:39:51 0

0 可預置同步 4 位二進制向上/向下計數(shù)器-74HC_HCT193

2023-02-15 19:40:01 0

0 12級二進制紋波計數(shù)器-74HC_HCT4040_Q100

2023-02-15 19:40:11 0

0 14級二進制紋波計數(shù)器-74HC_HCT4020

2023-02-15 19:40:50 1

1 12級二進制紋波計數(shù)器-74HC_HCT4040

2023-02-16 20:14:26 2

2 可預置同步4位二進制計數(shù)器;同步復位-74LVC163

2023-02-16 20:48:19 0

0 帶振蕩器的 14 級二進制紋波計數(shù)器-74LV4060_Q100

2023-02-16 21:04:08 0

0 帶振蕩器的 14 級二進制紋波計數(shù)器-74LV4060

2023-02-16 21:04:20 0

0 雙 4 位二進制紋波計數(shù)器-74LV393_Q100

2023-02-16 21:08:11 0

0 雙 4 位二進制紋波計數(shù)器-74LV393

2023-02-16 21:08:21 0

0 可預置同步4位二進制計數(shù)器;異步復位-74HC161_Q100

2023-02-16 21:10:00 1

1 可預置同步4位二進制計數(shù)器;異步復位-74HC161

2023-02-16 21:10:17 2

2 雙4位同步二進制計數(shù)器-74HC_HCT4520_Q100

2023-02-17 19:22:15 0

0 雙4位同步二進制計數(shù)器-74HC_HCT4520

2023-02-17 19:22:25 1

1 14級二進制紋波計數(shù)器-74HC_HCT4020_Q100

2023-02-17 20:05:22 0

0 7級二進制紋波計數(shù)器-74HC4024_Q100

2023-02-21 18:29:31 0

0 7級二進制紋波計數(shù)器-74HC4024

2023-02-21 18:29:48 0

0 可預置同步4位二進制計數(shù)器;同步復位-74HC_HCT163_Q100

2023-02-21 18:35:38 0

0 可預置同步4位二進制計數(shù)器;同步復位-74HC_HCT163

2023-02-21 18:35:57 0

0 8位同步二進制遞減計數(shù)器-74HC40103

2023-03-03 19:49:59 0

0 在之前的文章里,曾經(jīng)多次提到過二進制加法的數(shù)字電路,這里詳細說說它的細節(jié)。

2023-03-23 13:58:17 1497

1497

用此指令可以對一個整數(shù)計數(shù)器或一個二進制輸出端賦值,并將賦以的信號和一種條件 (布爾算子)相連接。

2023-04-15 09:54:20 1336

1336 電子發(fā)燒友網(wǎng)站提供《構建LED二進制計數(shù)器.zip》資料免費下載

2023-06-12 09:54:30 0

0 電子發(fā)燒友網(wǎng)站提供《使用Arduino UNO構建4位二進制計數(shù)器.zip》資料免費下載

2023-06-25 11:38:50 0

0 電子發(fā)燒友網(wǎng)站提供《異步二進制加法計數(shù)器電路圖.zip》資料免費下載

2023-11-20 14:54:26 6

6 、應用等方面。 一、工作原理 同步計數(shù)器:同步計數(shù)器的工作原理是,在時鐘信號的驅動下,對輸入的二進制數(shù)進行加法或減法運算,從而得到計數(shù)值。在每個時鐘周期內(nèi),同步計數(shù)器的計數(shù)值都會根據(jù)輸入的二進制數(shù)進行更新。因此,同

2023-12-13 14:54:24 1724

1724

電子發(fā)燒友App

電子發(fā)燒友App

評論