異步二進制減法計數器時序分析

- 二進制(41223)

- 計數器(92682)

- 減法(8274)

- 時序分析(22453)

- 異步(17994)

相關推薦

用74ls90設計六進制加法計數器

74LS90是一種常用的二進制計數器芯片,它可以實現二進制數的加法或減法計數。本文將介紹如何使用74LS90設計一個六進制加法計數器。 74LS90是一種雙時鐘輸入的二進制計數器芯片,具有異步

2023-12-14 17:30:11 2281

2281

2281

228114級二進制串行計數分頻器CD4060電子資料

概述:CD4060是一款14級二進制串行計數/分頻器,它是由一振蕩器和14級二進制串行計數器位組成,振蕩器的結構可以是RC或晶振電路,CR為高電平時,計數器清零且振蕩器使用無效。所有的計數器位均為主從觸發器。

2021-04-08 07:40:14

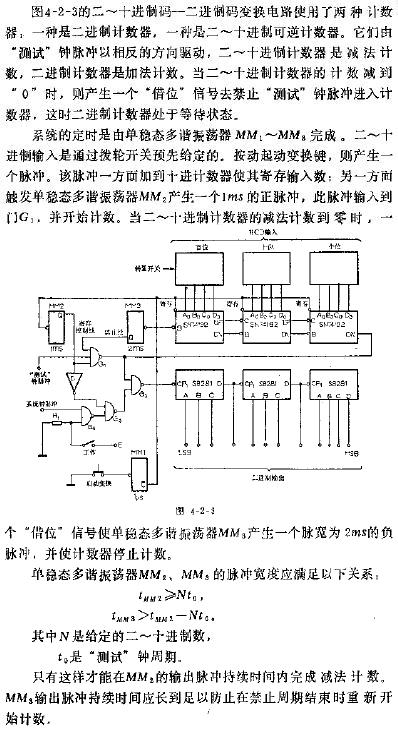

30進制加法計數器和30進制減法計數器

如何用multisim軟件仿真雙時鐘加/減計數器CT74LS192和譯碼器CC4511和譯碼器SM4205構成的30進制加法計數器和30進制減法計數器,求仿真接線圖。PCB打樣找華強 http://www.hqpcb.com/3 樣板2天出貨

2012-10-07 21:13:28

74161設計12進制計數器

74161設計12進制計數器,1.74161為十六進制計數器,設計十二進制計數器時1片就可以滿足要求。2.新建BDF文件及保存工程同前篇。3.將所需要的元器件和引腳拖入區域內并完成連接,如圖1所示圖1十二進制計數器連接圖4.建立VWF文件,仿真后得到結果如圖2

2021-07-22 06:33:31

二進制計數器在時鐘穩定的情況下出現跳變的情況

如題,LZ采用外部50M時鐘作為輸入,通過PLL鎖相環分頻得到100K的時鐘。將100K的時鐘作為二進制計數器的clk.但在SignalTap中發現,采到的數據在上升沿變化后,等時鐘維持穩定時,數據出現了變化。怕自己沒說清楚,附上時序圖和程序

2019-11-28 21:53:14

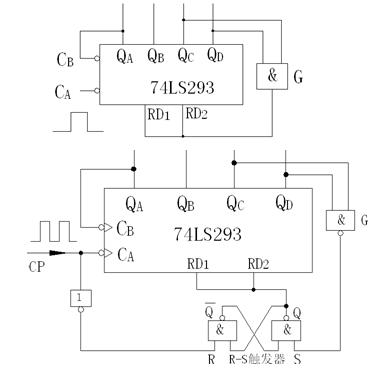

二進制計數器選擇不同的開關

用二進制計數器實現控制選擇不同的開關,電路輸入信號為一路方波,當此信號的第一個方波信號輸入時,電路使用開關1,當此信號的第二個方波信號輸入時,電路使用開關2,本人小白,麻煩回答具體點,附上簡單的電路圖,謝謝啦

2017-06-26 09:30:44

二進制與十進制數對照顯示實驗相關資料下載

這是一個可以對照顯示0~9這10個數字的二進制和十進制的電路。二進制數字用4個發光二極管顯示;它們排成一行,亮表示1,滅表示0。十進制數字用一個數碼管表示。數字的變化采用CD4040組成加法計數器,手動加1計數。

2021-04-27 07:21:40

二進制格雷碼與自然二進制碼的互換

。而絕對式編碼器是直接輸出數字量的傳感器,它是利用自然二進制或循環二進制(格雷碼)方式進行光電轉換的,編碼的設計一般是采用自然二進制碼、循環二進制碼、二進制補碼等。特點是不要計數器,在轉軸的任意位置

2011-03-08 14:16:59

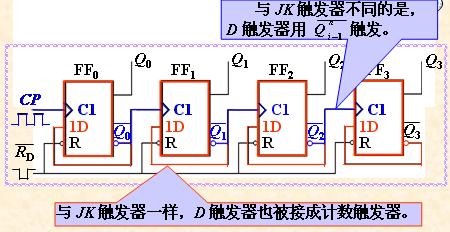

計數器及時序電路原理及實驗

Altera EPM7128SLC84-15,時鐘,四位八段數碼管。三、實驗內容1、用D觸發器設計異步四位二進制加法計數器。2、用JK觸發器設計異步十進制減法計數器。3、用74161兩個宏連接成八位二進制同步

2009-10-10 11:47:02

N進制計數器的實現

; S92 Q2 Q1 GNDT4290(T1290、74LS290、T210),是一個二-五-十進制計數器,能夠進行二進制、五進制計數、通過簡單聯線組成十進制計數

2008-07-05 13:41:26

十二進制計數器

我的實訓作業,求各位幫忙設計一個十二進制計數器,要電路仿真圖設計任務與要求1.每隔1s,計數器增1。2.用數碼管顯示計數值。3. 當定時器遞增到12時,定時器會自動返回到01顯示,然后繼續計時。我

2013-12-10 11:15:27

如何使用USART接收二進制數

我想制作一個以8個LED的形式實現二進制計數器。該計數器通過USART發送一個8位二進制數,并讓8個LED顯示數字(如果位為0,則指示燈熄滅,當位為1時指示燈亮)。這樣做的最佳方法是什么?

2018-10-08 14:07:42

如何理解二進制運算規則 二進制是如何運算的

二進制運算規則二進制的運算算術運算二進制的加法:0+0=0,0+1=1 ,1+0=1, 1+1=10(向高位進位);二進制的減法:0-0=0,10-1=1(向高位借位) 1-0=1,1-1=0 (模

2019-12-11 17:49:02

怎么使用LUT設計一個4位二進制上變頻計數器

嗨,我需要使用LUT設計一個4位二進制上變頻計數器。我正在嘗試遵循多路復用器方法。任何想法都非常感謝。謝謝小學以上來自于谷歌翻譯以下為原文Hi , I need to design a 4bit

2019-02-14 11:29:07

怎么實現二進制計數器?

大家好,由于我是初學者,我盡可能多地嘗試,看看我是否能夠克服編程FPGA的學習曲線。這次我用VHDL實現了一個二進制計數器。圖書館IEEE;使用IEEE.STD_LOGIC_1164.ALL

2020-03-13 09:16:40

求助,同步二進制減法計數器的狀態表該怎么畫?

請問各位,同步二進制減法計數器的狀態表該怎么畫?之前只做過同步加法和異步減法,現在混淆了,同步減法的次態是代入特性方程算出來之后再作為下一個初態,還是直接遞減不用算?

2022-11-23 20:44:42

淺析計數器的組成部分及其功能

計數器(Counter)由基本的計數單元和控制門所組成,是在數字系統中對脈沖的個數進行計數,以實現測量、計數和控制功能,且兼有分頻功能的儀器。計數器按進位制不同,分為二進制計數器和十進制計數器;按

2021-12-08 08:32:28

集成四位二進制計數器

④ 構成脈沖分頻器集成十進制計數器【74LS290】集成十進制計數器【74LS390】1. 集成四位二進制計數器【74LVC161】(1) 邏輯符號CR:CR:CR: 異步置0端。優先級最高。PE:PE:PE:并行置數端。次高優先級。TC:TC:TC:進位信號。CEP,CET:CEP

2021-07-29 07:20:09

異步時序控制器的設計

設計一脈沖異步二進制加1/減1計數器.電路有一輸入線X,其信號為脈沖.另一信號M是電位,當M=0時,電路為加1計數器,當M=1時電路為減1計數器。使用鐘控D鎖存器實現。

2010-09-28 10:30:47 0

0

0

0十進制計數器

十進制計數器

二進制計數器具有電路結構簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數,特別是當二進制數的位數較多時,閱讀非常困難,還

2007-06-20 13:46:05 4188

4188

4188

4188什么是二進制計數器,二進制計數器原理是什么?

什么是二進制計數器,二進制計數器原理是什么?

計數器是數字系統中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數,還可以實現

2010-03-08 13:16:34 30352

30352

30352

30352十進制計數器,十進制計數器原理是什么?

十進制計數器,十進制計數器原理是什么?

二進制計數器具有電路結構簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數,特

2010-03-08 13:19:54 24108

24108

24108

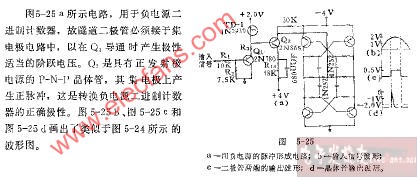

24108本的二進制加法/減法器,本的二進制加法/減法器原理

本的二進制加法/減法器,本的二進制加法/減法器原理

兩個二進制數字Ai,Bi和一個進位輸入Ci相加,產生一個和輸出Si,以及一個進位輸

2010-04-13 11:11:55 5132

5132

5132

5132異步二進制加法計數器時序分析

計數器是一種常用的數字部件,是觸發器的重要應用之一。顧名思義,計數器就是能夠累計輸入脈沖數目的數字電路。它是一種記憶系統,除用作計數外,還可用作分頻、定時等

2011-04-19 11:29:28 12187

12187

12187

12187

74LS161異步置零法構成任意進制計數器的Multisim仿真

介紹了集成4位二進制計數器 74LS161 異步置零法構成任意進制計數器的 Multisim 仿真方案,即以波形方式顯示計數器的計數過程、過渡狀態形成異步置零信號的過程,用四蹤示波器以面板

2011-08-05 14:25:22 336

336

336

336CC4060—14位二進制串行計數器

CC4060 由一震蕩器和14 極二進制串行計數器位組成,震蕩器的結構可以是RC 或晶振電路。CR 為高電平時,計數器清零且振蕩器使用無效,所有的計數器位均為主從觸發器。

2012-03-29 15:01:57 198

198

198

198二進制計數器74hct4020資料

Harris CD74HC4020和CD74HCT4020為14級紋波進位二進制計數器。所有計數器級都是主從觸發器。階段狀態提前一次計數每個輸入脈沖的負時鐘轉換;a高MR線上的電壓水平將所有計數器重置為零狀態所有輸入和輸出都經過緩沖。

2022-07-10 10:25:33 12

12

12

1224進制計數器的設計

集成計數器常見的是多位二進制計數器及十進制計數器,當需要實現其它進制計數器時,通常利用現有的集成計數器進行適當的連接而構成。對于當設計要求沒有限定計數器的狀態編碼時電路設計的靈活性問題已有文獻進行

2017-11-09 16:36:16 81

81

81

81二進制與十進制數對照顯示實驗,十進制,二進制對照

CD4040組成加法計數器,手動加1計數。

2.二進制與十進制數字對照顯示實驗 本電路可以形象地顯示0~9的二進制數。按動加1按鈕AN2,計數器的輸入端CP得到一個負脈沖信號,計數器進行

2018-09-20 18:26:41 2326

2326

2326

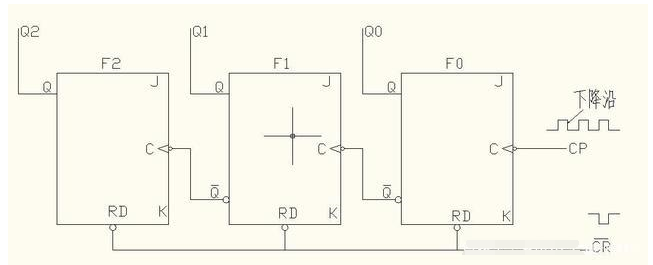

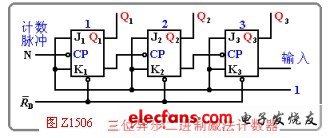

2326減法計數器的結構原理

該計數器是一個3位二進制異步減法計數器,它與前面介紹過的3位二進制異步加法計 數器一樣,是由3個JK觸發器組成,其中J、K端都懸空(相當于J=1、K=1),兩者的不同 之處在于,減法計數器是將前一個觸發器的Q非端與下一個觸發器的CP端相連。

2021-04-18 11:19:47 16340

16340

16340

16340

同步計數器和異步計數器的區別主要在哪里

、應用等方面。 一、工作原理 同步計數器:同步計數器的工作原理是,在時鐘信號的驅動下,對輸入的二進制數進行加法或減法運算,從而得到計數值。在每個時鐘周期內,同步計數器的計數值都會根據輸入的二進制數進行更新。因此,同

2023-12-13 14:54:24 1724

1724

1724

1724 電子發燒友App

電子發燒友App

評論