?

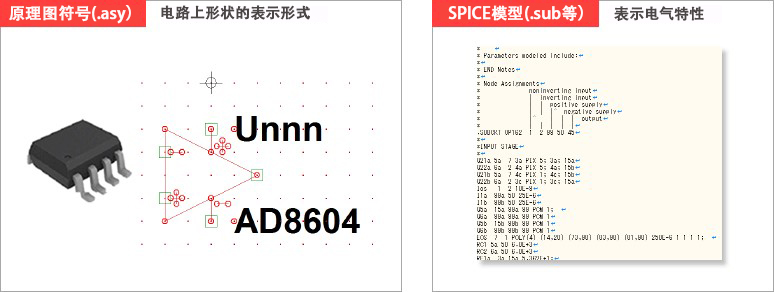

系統工程師們需要所有類型IC的準確模型,他們需要用Spice模型來運行復雜的電路仿真。早期的Spice模型幾乎沒有什么非線性元件,需要以準確性為代價而獲得盡量少的仿真時間,而新方法增加了非線性元件的數量,并改進了準確性。對于小功率低噪聲運算放大器,可以建立一種多級的模型。模型采用了Analog Devices公司的工作成果(參考文獻1),需要對小功率低噪聲精密放大器的建模作一些架構上的改變。模型架構上要通過八級來處理輸入信號。用一個手持計算器就可以簡單地算出八級的一些參數。要理解建模過程,必須有使用Spice的經驗。

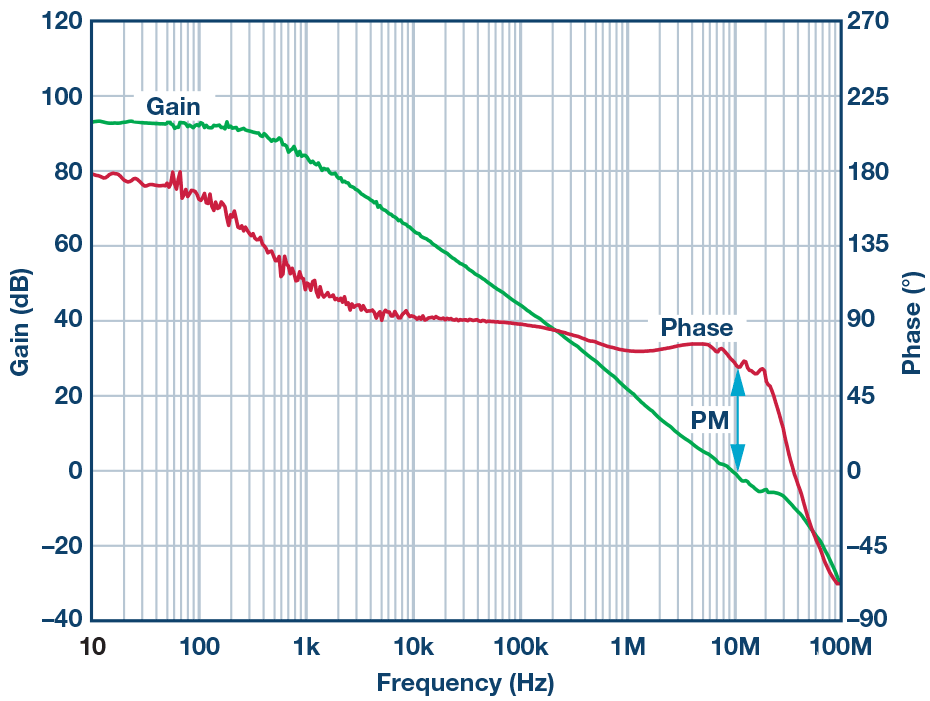

雖然較高速放大器有多個極點和零點,但本模型是針對單極的10 MHz放大器。它可以仿真放大器的主要AC與DC參數。該模型包含的AC參數有:閃爍噪聲和平帶噪聲、轉換速率、CMRR(共模抑制比)、增益和相位。DC參數有VOS(輸入偏移電壓)、IOS(輸入偏移電流)、靜態電流,以及輸出電壓擺幅。模型采用的是25°C典型參數(參考文獻2)。輸入級的模型愈接近實際放大器,則結果就會愈準確。對輸入級晶體管或MOSFET采用一些工藝參數,可以實現放大器性能的準確AC表述。此模型的架構可以對采用多電源的放大器建模。任何信號處理塊中都沒有參考地。經過差分至單端的轉換后,所有內部產生的結點電壓都參考到電源的中點,這非常像一個放大器的真實運行情況。

八個級聯級

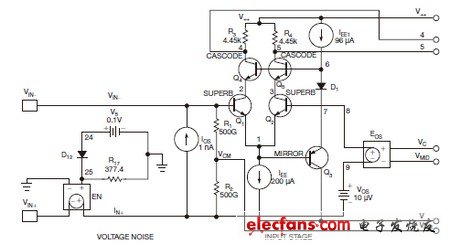

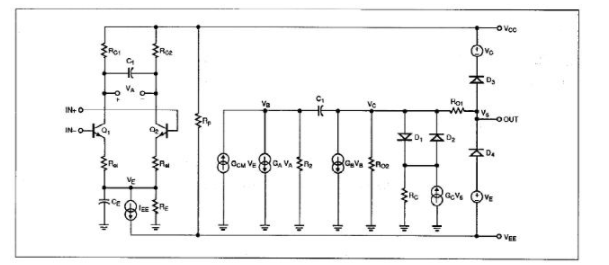

模型的電路邏輯圖包含八個功能塊(圖1)。唯一看起來像放大器的電路是輸入級(見表1)。所有其它級都通過壓控電流源或壓控電壓源來處理輸入信號。這些級還可能包含二極管、直流電源、電阻、電容以及電感。

?

?

?

圖1 ,這個spice模型有八級

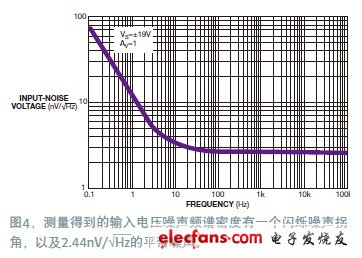

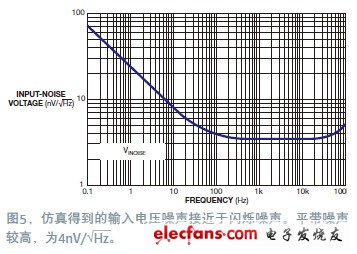

電壓噪聲級產生閃爍與平帶噪聲。要產生一個僅為4nV/√H2的平帶噪聲,要將所有二極管和晶體管的模型參數kf與af分別設為0和1。為了將模型的噪聲背景降低到一位數的納伏水平,可能需要降低模型的Johnson噪聲(參考文獻3),方法是在可能的地方減小電阻值。

減小電阻值以前,先計算出標準的電阻值,并完成所有的仿真調整。然后將電阻值減小到1Ω,就可以調整電壓噪聲級,并且重新計算跨導,以及各級的時間常數,以保持相同的傳遞函數。通常可以將電阻R5、R6、R9、R10、R1和R12設為1Ω。如果要建模的放大器有數百納伏的輸入信號,則不需要降低Johnson噪聲。初始噪聲仿真會告訴你是否需要這一步驟。一旦將模型的平帶噪聲設為低于放大器的噪聲背景,就可以調節DN、R17和V5,改變閃爍噪聲與平帶噪聲。

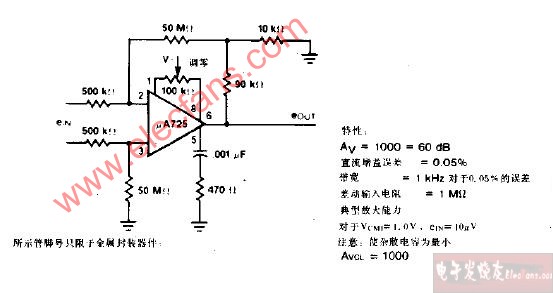

所選運放的輸入級包含有五只雙極晶體管,用于實際IC結構的建模。對于采用NMOS或PMOS級的運算放大器(見附文1,“典型輸入級”)。輸入級包含一個模型的電流源IOS,一個模型的電壓源VOS,以及一個壓控電壓源。R1和R2 決定了器件的CMRR。

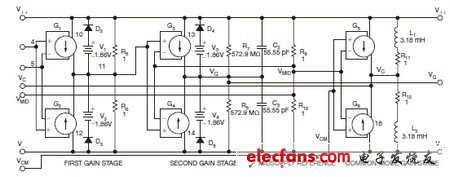

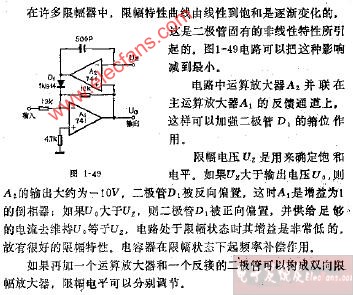

第一增益級將輸入級與第一增益級的聯合增益設為1,這簡化了對第二增益級中轉換速率限制元件的計算工作。二極管D2至D5以及V1至V4用于輸出電壓擺幅的箝位。增加V1至V4的值將減小最大輸出電壓擺幅。通過調節V1和V3可以控制最大輸出電壓擺幅VOH,而最小輸出電壓擺幅VOL受控于V2和V4。限壓必須出現在開環增益級;否則,后面的結點就會試圖模擬大信號(數百千伏)的生成。

?

第二增益級設定開環電壓增益、帶寬以及放大器的轉換速率,方法是調節跨導塊G3和G4,以及元件R7、R8、C2和C3。

中位電源參考級包括兩個等值電阻R9和R10。這些電阻用于生成一個中位基準電壓。將這些電阻值設為1Ω,可以降低模型的Johnson電壓噪聲。流經這些電阻的大電流不會出現在仿真結果中,因為有電源隔離級。

?

共模增益級包括兩個壓控電流源,它驅動兩只等值電阻,兩只電阻與一個連接到電源軌的電感串聯(見附文2,“VCCS級工作原理”)。電感模擬了CMRR在較高輸入頻率時的滾降。控制電流源的是相對于中位電壓的輸入共模電壓。輸入級的電阻R1和R2產生共模電壓。每個源的跨導都設為用相關電阻值除以DC時放大器CMRR后的倒數。電感為共模增益補充了一個Z平面零點,等效于為CMRR增加了一極。在對共模電壓的調節和頻率整形后,再用一個壓控電壓源EOS將其加回到輸入級。

?

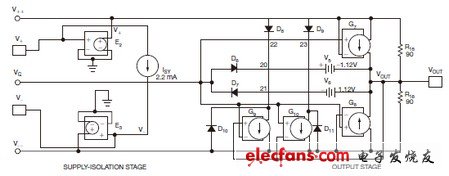

電源隔離級包括兩個壓控電壓源與一個電流源。這樣就能用結點列表中的一項,設定放大器的總電流。它還能將內部電流與仿真器看到的外部電流隔離開來,使模型能夠提供小功率低電壓噪聲放大器的正確靜態電流。設計折中是不能用輸出電流的電路。禁用這個電路后,模型就不用考慮負載電流了。

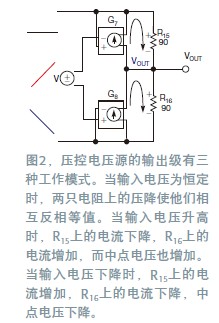

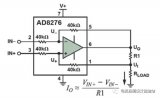

輸出級的工作并不明顯。經過適當的頻率整形后,放大器的輸出信號表現為一個以G7與G8輸入點處中位電源為基準的電壓。跨導塊G7與G8驅動兩只等值電阻,電阻連接到電 源軌。它們作為有源電流發生器。G7與G8產生出正好適當的電流,為其并聯電阻提供所需的壓降(圖2)。

通過模擬正確的輸出電阻,降低了放大器負載的DC開環增益。二極管D6和D7以及DC電源V5和V6用于仿真輸出短路保護功能。在故障情況下,輸出電壓會箝位到前面的頻率整形級。調整V5和V6的值設定輸出短路保護的限制值。

計算參數

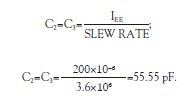

在計算Spice模型的參數時,需要運放數據表的各種規格,以及IC設計信息(表1)。將下列方程置于一個Excel表中,就能夠修改關鍵規格,快速地看到運放性能的效果。從數據表可以將EOS和IOS直接輸入模型。如果模型需要,一般可以從數據表中得到輸入差分電容的規格。通過輸入差分對尾電流IEE與放大器轉換速率的關聯,就可以確定C2和C3的值。這個步驟建立了單極RC網絡的最大頻率,并設定了單位增益帶寬。放大器數據表中很少提供IEE值,因此必須從IC設計者那里獲得該值。對于參考文獻2中的放大器,方程計算結果55.55 pF:

?

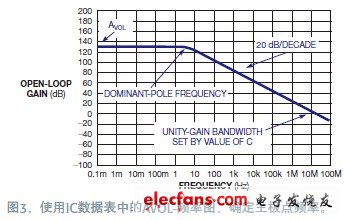

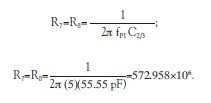

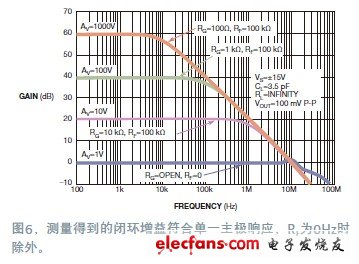

下面,用主極點頻率方程確定R7和R8的值。這個方程設定了RC網絡的斷點。查看放大器數據表的開環增益圖就可以獲得主極點頻率fP1(圖3)。參考文獻2中放大器獲得的值是573 MΩ:

?

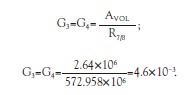

使用數據表中的AVOL 以及電阻值R7/8,以確定壓控電流源的跨導:

?

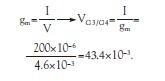

對于參考文獻2中的放大器,跨導部分算得的結果是0.0046。模型使用第一增益級,將輸入級與第一增益級的聯合增益設為1。現在,可以計算得到G3和G4輸入的電壓產生出200×10-6的尾電流,它流經R7和R8。

?

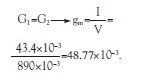

在轉換速率限制期間,200×10-6的電流阱通過電阻R3或R4作電流箝位。在正輸入電壓時,R4承載電流。負輸入電壓則意味著電流會通過R3。這個電流流過4.45kΩ的電阻,產生一個0.89V的壓降。這個壓降出現在G1和G2的輸入端。要將輸入級與第一級的聯合增益設為1,必須計算出G1和G2的跨導,使得當它們的輸入為0.89V時,輸出電壓等于0.0434V。如果將與G1和G2輸出并聯的電阻值設為1Ω,則電壓將等于電流,于是可以算出G1和G2的跨導:

?

如果手頭沒有設計審核文檔,可將R3和R4設為1Ω,以計算在G1和G2輸入上出現的電壓。如果從IC設計者那里得到了集電極電流,則可以將其直接輸入模型中:

?

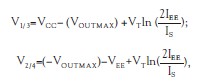

設V1/3和V2/4 電壓為獲得最大輸出電壓擺幅:

?

其中,兩個二極管都是T=25°C時VT=0.02585V,IS=1×10-12A。對于正的輸入電壓擺幅,模型將輸出電壓箝位于一個等于VCC+VD2/4-V1/3的值,對負輸入電壓擺幅為?VEE?V2/4+ VD3/5。從噪聲角度考慮,將R11和R12的值選擇為1Ω:

?

計算出G7和G8的值:

?

查看數據表中的CMRR-頻率圖,可以估算出共模極點頻率fPCM。由該頻率可以算出電感值:

?

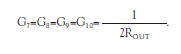

將輸出級的跨導設為2ROUT的倒數:

?

這個步驟通過G7、G8、G9和G10獲得了單位增益。輸出電阻建立為2ROUT,這是考慮了輸出電流必須來自一個電源軌:

?

現在可以算出V5:

?

取第一項的絕對值,就可以得出V6的絕對值:

?

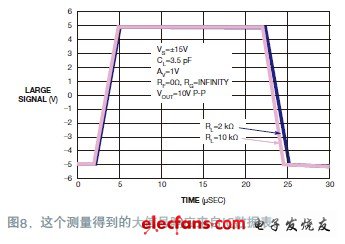

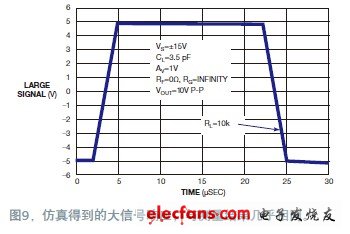

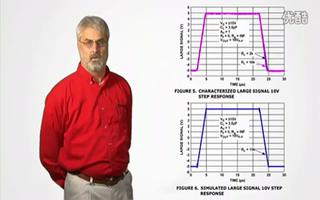

仿真結果

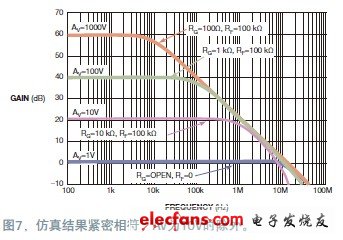

一旦計算完了模型的所有參數,就可以運行仿真了。仿真與數據表給出的器件性能有良好的關聯(圖4至圖9)。IC的數據表提供了仿真與真實結果的更多比較。現代計算機的能力可以快速解算出一個輸入級包含五只雙極晶體管的模型。這些晶體管各自都有專門的模型參數。用這種方法得到的仿真結果接近于器件的測量結果。另外,你可以用這個過程對一位數納伏噪聲的參數作建模。由于這種方法能為小電源電流建模,因此最適用于低噪聲的微功率放大器。

參考文獻

1.Alexander, Mark, and Derek F Bowers, “SPICE-Compatible Op Amp Macro- Models,” Application Note AN-138, Analog Devices, February 1990.

2.“Precision Single and Dual Low Noise Operational Amplifiers, ISL28127, ISL28227,” Intersil Data Sheet, Dec 16, 2010.

3.Bowers, Derek F, “Minimizing Noise in Analog Bipolar Circuit Design,” IEEE Proceedings of the 1989 Bipolar Circuits and Technology Meeting, Sept 18, 1989, pg 107.

?

?

?

?

?

?

附文1,典型輸入級

本文中的模型針對有一個雙極晶體管輸入級的運放。很多現代放大器采用了NMOS輸入晶體管。還有一些現代運放使用了PMOS晶體管輸入級(。你需要確定需要建模運放的輸入級結構,然后才能使用適合的輸入級邏輯圖。JFET輸入的邏輯圖未提供,但它們可在文獻中找到。

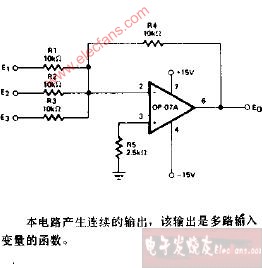

附文2,VCCS級工作原理

當G1和G2的輸入電壓增加時,合成后輸出電流的增加將提高中點的電壓。當輸入的電壓降低時,中點電壓將降低。如果將該級的gm 設定為等于并聯電阻的倒數,則該級有正的單位增益。可以構想一個等效于差分電路的單端電路。這樣有助于想象流經這些級的信號流。

電子發燒友App

電子發燒友App

評論