,所以器件的不匹配性隨著器件尺寸的減小越加明顯。在短溝道CMOS電路中由于不匹配性引起的特性變化可能會(huì)限制器件尺寸的減小而影響工藝水平的發(fā)展,這樣不匹配性的消除就顯得更重要。

2020-08-11 15:29:09 2739

2739

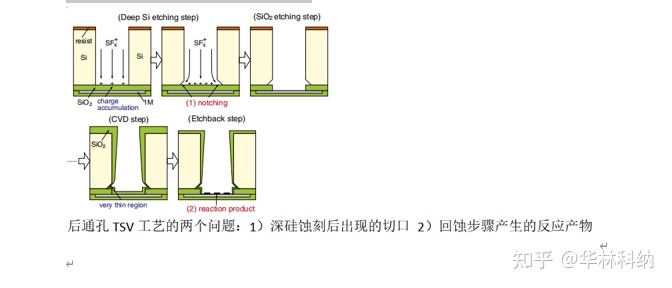

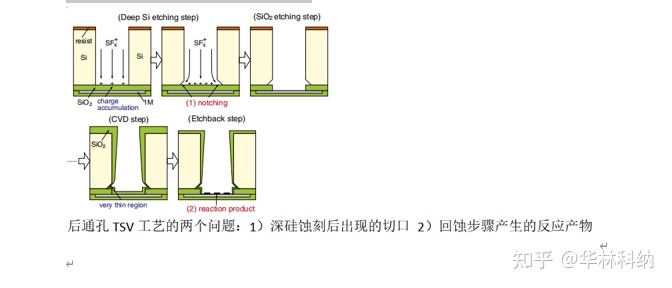

本文報(bào)道了TSV過程的細(xì)節(jié)。還顯示了可以在8-in上均勻地形成許多小的tsv(直徑:6 m,深度:22 m)。通過這種TSV工藝的晶片。我們?nèi)A林科納研究了TSV的電學(xué)特性,結(jié)果表明TSV具有低電阻和低電容;小的TSV-硅漏電流和大約83%的高TSV產(chǎn)率。

2022-06-16 14:02:43 2749

2749

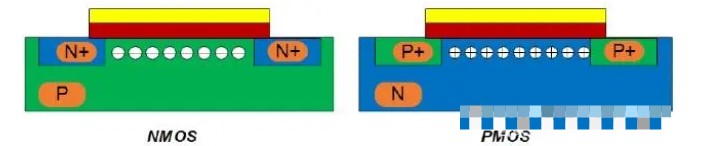

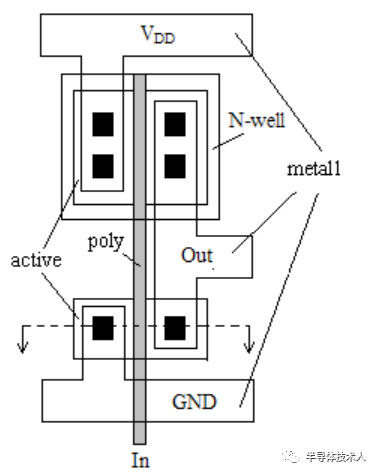

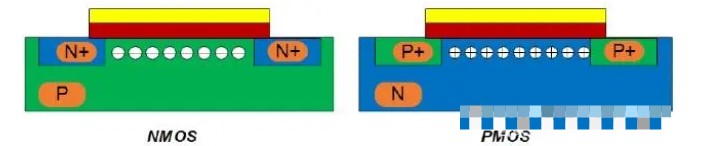

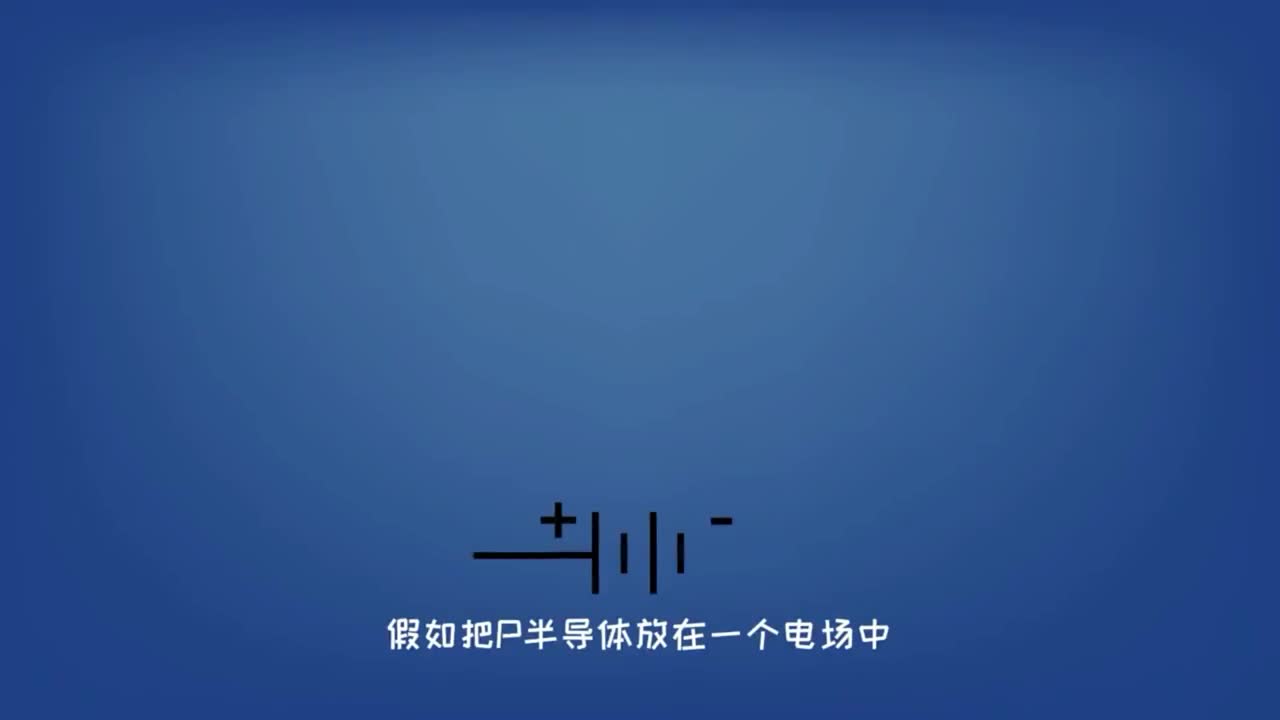

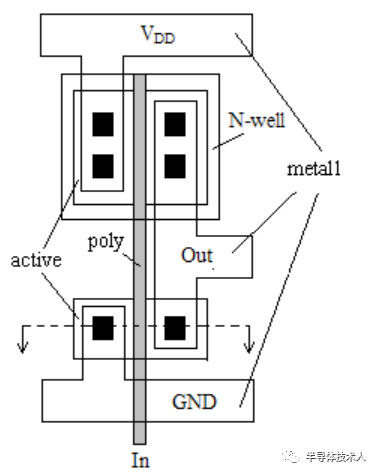

咱們前幾期講的一直是NMOS,導(dǎo)電靠的是溝道中的自由電荷。而PMOS與NMOS結(jié)構(gòu)上的不同點(diǎn)在于半導(dǎo)體基板的材料恰恰相反,是在N型摻雜基板的基礎(chǔ)上加了兩塊重?fù)诫s的P型半導(dǎo)體,這兩塊兩塊重?fù)诫s的P型半導(dǎo)體分別為PMOS的源級(jí)和漏極,金屬部分和NMOS一樣仍然作為柵極。PMOS導(dǎo)電靠的是溝道中的空穴。

2023-02-16 11:41:19 6888

6888

管和N型MOS管之分。由MOS管構(gòu)成的集成電路稱為MOS集成電路,由NMOS組成的電路就是NMOS集成電路,由PMOS管組成的電路就是PMOS集成電路,由NMOS和PMOS兩種管子組成的互補(bǔ)MOS電路,即CMOS電路。

2023-02-16 17:00:15 4430

4430

MOSFET器件是數(shù)字集成電路的最小單位,因?yàn)镸OSFET的開關(guān)特性和輸出曲線特性,由PMOS和NMOS組成的CMOS門電路,則為數(shù)字集成電路最基本的電路結(jié)構(gòu)。

2023-07-11 10:49:58 8009

8009

本帖最后由 gk320830 于 2015-3-8 10:42 編輯

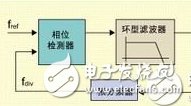

0.18μm CMOS工藝的2.5GHz環(huán)形壓控振蕩器設(shè)計(jì) 誰能給點(diǎn)入門資料以及提供可以用的電路圖萬分感激

2013-04-11 19:56:29

。并研究了非對(duì)稱晶閘管的制作工藝,樣品測(cè)試結(jié)果表明,6.5kV非對(duì)稱型晶閘管的設(shè)計(jì)參數(shù)和制作工藝方案是合理可行的。【關(guān)鍵詞】:電力半導(dǎo)體器件;;非對(duì)稱晶閘管;;模擬;;優(yōu)化設(shè)計(jì);;制作工藝【DOI

2010-05-04 08:06:51

CMOS是一個(gè)簡(jiǎn)單的前道工藝,大家能說說具體process嗎

2024-01-12 14:55:10

問:為什么現(xiàn)在的CMOS工藝一般都是用P襯底而不是N襯底??jī)烧哂惺裁磪^(qū)別啊?答:為什么CMOS工藝采用P襯底,而不用N襯底?這主要從兩個(gè)方面來考慮:一個(gè)是材料和工藝問題;另一個(gè)是電氣性能問題。P型

2012-05-22 09:38:48

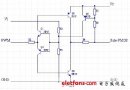

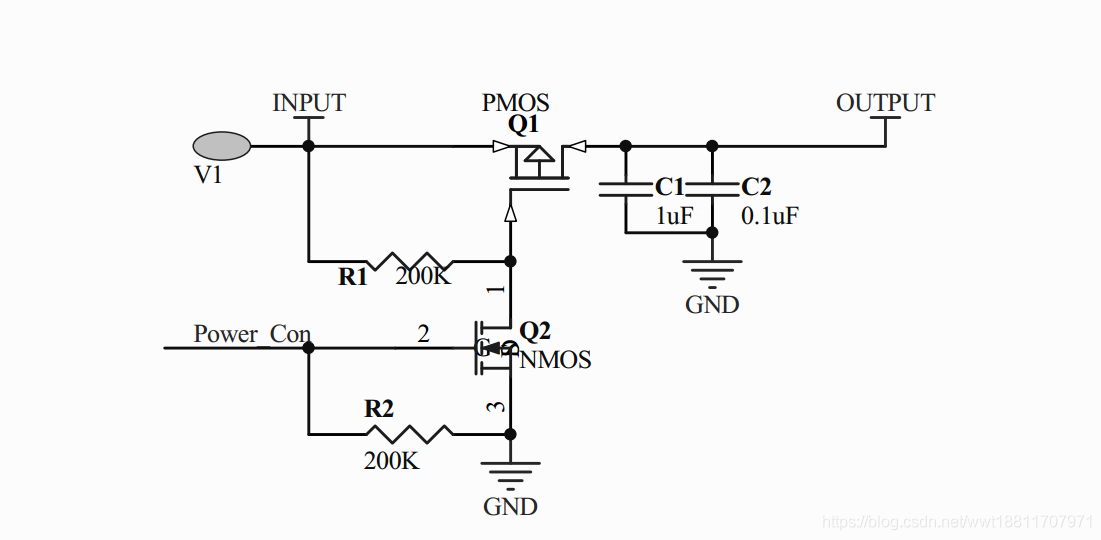

CMOS工藝鋰電池保護(hù)電路圖的實(shí)現(xiàn)

2012-08-06 11:06:35

做得非常小,并且CMOS的集成密度非常高。因此,一般高壓、大功率的MOS管大部分還都得用垂直生產(chǎn)工藝制造的NMOS或PMOS管。

2012-05-21 17:38:20

。由于雙極性器件固有的特性優(yōu)于CMOS器件,因此一些研究人員認(rèn)為射頻CMOS只適用于具有較低性能標(biāo)準(zhǔn),如ISM等低性能系統(tǒng),或者可以通過改進(jìn)CMOS工藝,如蝕刻電感器下面的基底來提高其性能。射頻

2021-07-29 07:00:00

這種場(chǎng)合,大部分都是從工藝,導(dǎo)通電阻 Rds 來解釋,但隨著半導(dǎo)體工藝的進(jìn)步,現(xiàn)今的 PMOS 與 NMOS 之間差距已經(jīng)不大了,從 SOT-23 的封裝來看,兩者的大小也是差不多的。個(gè)人覺得...

2021-10-28 07:04:20

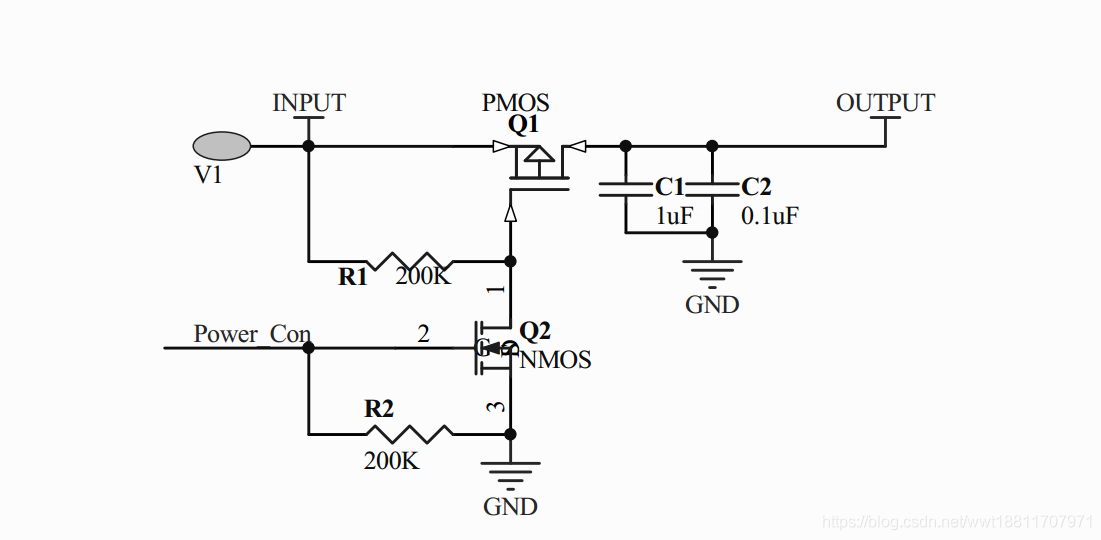

、上位機(jī)等,給新手綜合學(xué)習(xí)的平臺(tái),給老司機(jī)交流的平臺(tái)。所有文章來源于項(xiàng)目實(shí)戰(zhàn),屬于原創(chuàng)。一、原理介紹如上圖,PMOS管是壓控型器件,Vgs大于開啟電壓時(shí),內(nèi)部溝道在場(chǎng)強(qiáng)的作用下導(dǎo)通,Vgs小于開啟...

2021-07-19 07:10:33

PMOS全稱是P型金屬氧化物半導(dǎo)體(positive channel Metal Oxide Semiconductor),MOSFET為壓控型器件。當(dāng)電壓Vgs低于閾值Vth時(shí),PMOS在場(chǎng)強(qiáng)的作用

2022-01-13 08:22:48

COMS工藝制程技術(shù)主要包括了:1.典型工藝技術(shù):①雙極型工藝技術(shù)② PMOS工藝技術(shù)③NMOS工藝技術(shù)④ CMOS工藝技術(shù)2.特殊工藝技術(shù)。BiCOMS工藝技術(shù),BCD工藝技術(shù),HV-CMOSI藝

2019-03-15 18:09:22

我在測(cè)試PMOS管的導(dǎo)通特性發(fā)現(xiàn)了這個(gè)問題,大家?guī)臀铱纯词悄睦锏膯栴},電路圖見附件。

2017-12-29 15:26:33

`SOD323系列普容TVS單向/雙向瞬變二極管 18V DCSD18-HESD 保護(hù)和 TVS 浪涌二極管保護(hù)您的系統(tǒng)免受 ESD 和浪涌沖擊。我們的保護(hù)二極管的特性包括超低電容、低泄漏電流、低鉗

2021-07-12 09:20:36

Sic mesfet工藝技術(shù)研究與器件研究針對(duì)SiC 襯底缺陷密度相對(duì)較高的問題,研究了消除或減弱其影響的工藝技術(shù)并進(jìn)行了器件研制。通過優(yōu)化刻蝕條件獲得了粗糙度為2?07 nm的刻蝕表面;犧牲氧化

2009-10-06 09:48:48

書籍:《炬豐科技-半導(dǎo)體工藝》文章:CMOS 單元工藝編號(hào):JFSJ-21-027作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html晶圓生產(chǎn)需要三個(gè)一般過程:硅

2021-07-06 09:32:40

`書籍:《炬豐科技-半導(dǎo)體工藝》文章:超大規(guī)模集成電路制造技術(shù)簡(jiǎn)介編號(hào):JFSJ-21-076作者:炬豐科技概括VLSI制造中使用的材料材料根據(jù)其導(dǎo)電特性可分為三大類:絕緣體導(dǎo)體半導(dǎo)體

2021-07-09 10:26:01

申請(qǐng)理由:項(xiàng)目描述:1.研究該傳感器的功能2.將該傳感器與變噴桿相結(jié)合,檢測(cè)噴桿轉(zhuǎn)換過程的位置變化,提高噴桿的動(dòng)態(tài)響應(yīng)特性,實(shí)時(shí)控制噴桿變形啟停。

2016-10-08 16:35:04

隨著射頻無線通信事業(yè)的發(fā)展和移動(dòng)通訊技術(shù)的進(jìn)步,射頻微波器件的性能與速度成為人們關(guān)注的重點(diǎn),市場(chǎng)對(duì)其的需求也日益增多。目前,CMOS工藝是數(shù)字集成電路設(shè)計(jì)的主要工藝選擇,對(duì)于模擬與射頻集成電路來說,有哪些選擇途徑?為什么要選擇標(biāo)準(zhǔn)CMOS工藝集成肖特基二極管?

2019-08-01 08:18:10

什么是PMOS管?PMOS管有哪些特性?PMOS管有什么導(dǎo)通條件?

2021-06-16 08:07:07

最近幾年,我們已經(jīng)開始看到一些有關(guān)射頻(RF)CMOS工藝的參考文獻(xiàn)和針對(duì)這些工藝的RF模型參考文獻(xiàn)。本文將探討這類RF所指代的真正含義,并闡述它們對(duì)RF電路設(shè)計(jì)人員的重要性。我們可以從三個(gè)角度

2019-06-25 08:17:16

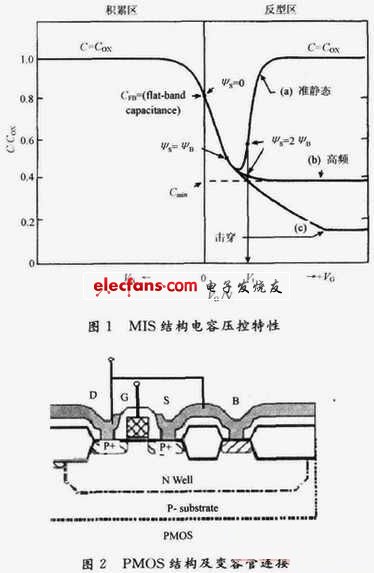

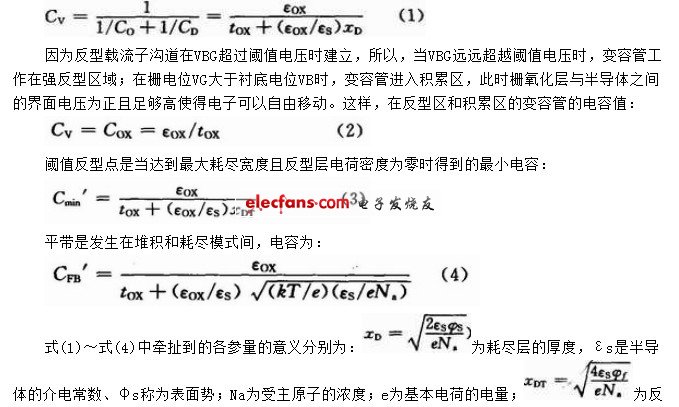

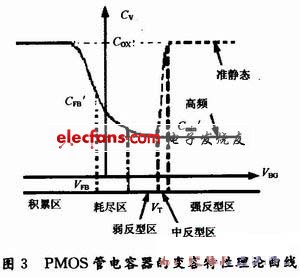

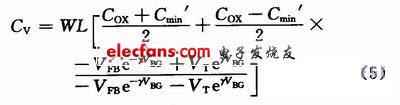

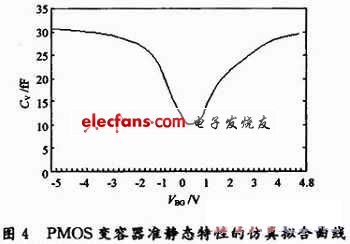

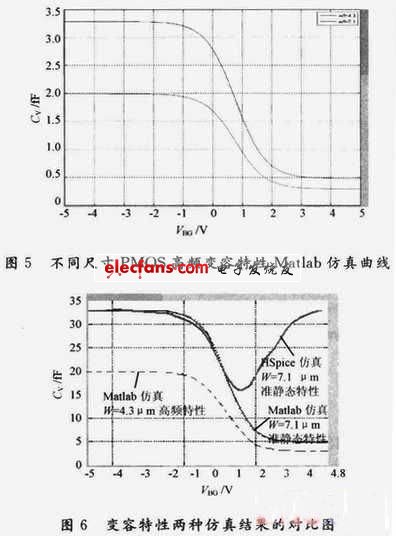

有哪些方法可以獲得MOS變容管單調(diào)的調(diào)諧特性?MOS變容管反型與積累型MOS變容管

2021-04-07 06:24:34

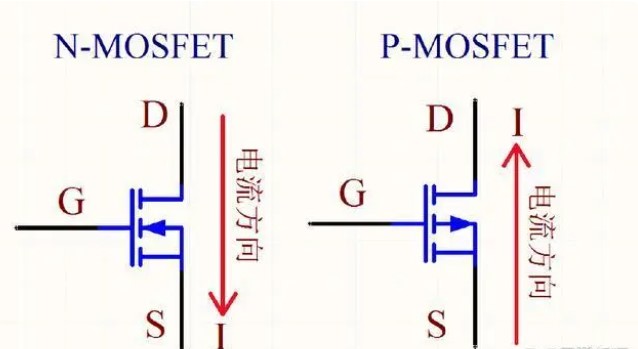

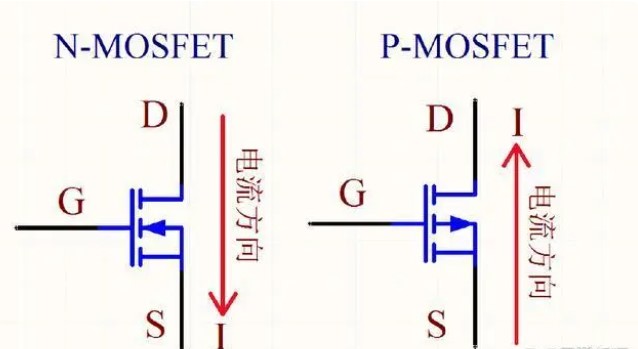

1 MOS管導(dǎo)通截止原理NMOS管的主回路電流方向?yàn)镈—>S,導(dǎo)通條件為VGS有一定的壓差,如 5V(G電位比S電位高)。PMOS管的主回路電流方向?yàn)镾—>D,導(dǎo)通條件為

2023-02-17 13:58:02

小弟正在做一個(gè)單相UPS逆變系統(tǒng)的仿真研究,現(xiàn)在遇到一個(gè)問題,請(qǐng)教一下大家~!在simulink中我用電壓外環(huán)、電流內(nèi)環(huán)實(shí)現(xiàn)逆變器的控制,那么我該怎么產(chǎn)生SPWM波呢?也就是我的三角波載波的幅值該怎么得到?是通過閉環(huán)反饋回來的值還是設(shè)定一個(gè)固定的值?

2014-03-18 15:45:25

摘要: 本文設(shè)計(jì)了一種CMOS工藝下的欠壓保護(hù)電路,首先分析了電路的工作原理,而后給出了各MOS管的參數(shù)計(jì)算,并給出pspice仿真的結(jié)果。此電路結(jié)構(gòu)簡(jiǎn)單,工藝實(shí)現(xiàn)容易,可用于高壓和功率集成電路

2018-08-27 15:54:31

的變?nèi)荻O管作為壓控器件,然而在用實(shí)際工藝實(shí)現(xiàn)電路時(shí),會(huì)發(fā)現(xiàn)變?nèi)荻O管的品質(zhì)因數(shù)通常都很小,這將影響到電路的性能。于是,人們便嘗試采用其它可以用CMOS工藝實(shí)現(xiàn)的器件來代替一般的變?nèi)荻O管,MOS變容管便應(yīng)

2019-06-27 06:58:23

、數(shù)據(jù)傳輸帶寬帶來了巨大壓力,所以為了保障容災(zāi)系統(tǒng)高效穩(wěn)定地運(yùn)行,需要建立一個(gè)存儲(chǔ)容量?jī)?yōu)化機(jī)制來減少數(shù)據(jù)對(duì)存儲(chǔ)容量需求。本課題以“基于重復(fù)數(shù)據(jù)刪除技術(shù)的容災(zāi)系統(tǒng)的研究”為題,在深入研究容災(zāi)備份中存儲(chǔ)容量

2010-04-24 09:19:47

如何利用0.18μm CMOS工藝去設(shè)計(jì)16:1復(fù)用器?以及怎樣去驗(yàn)證這種復(fù)用器?

2021-04-09 06:39:47

本文研究了一個(gè)用0.6μm CMOS工藝實(shí)現(xiàn)的功率放大器, E型功率放大器具有很高的效率,它工作在開關(guān)狀態(tài),電路結(jié)構(gòu)簡(jiǎn)單,理想功率效率為 100%,適應(yīng)于恒包絡(luò)信號(hào)的放大,例如FM和GMSK等通信系統(tǒng)。

2021-04-23 07:04:31

本文采用0.18 μm CMOS工藝設(shè)計(jì)了一種適用于TI-ADC的高速、低功耗開環(huán)T&H電路。

2021-04-20 06:58:59

三角波信號(hào)發(fā)生器的原理是什么?三角波信號(hào)發(fā)生器的設(shè)計(jì)約束是什么?如何采用CMOS工藝去設(shè)計(jì)三角波信號(hào)發(fā)生器?

2021-04-13 06:26:12

本文給出了使用CMOS工藝設(shè)計(jì)的單片集成超高速4:1復(fù)接器。

2021-04-12 06:55:55

近日,微電子所納米加工與新器件集成技術(shù)研究室(三室)在阻變存儲(chǔ)器研究工作中取得進(jìn)展,并被美國化學(xué)協(xié)會(huì)ACS Nano雜志在線報(bào)道。 基于二元氧化物材料的電阻式隨機(jī)存儲(chǔ)器(ReRAM)具有低廉的價(jià)格

2010-12-29 15:13:32

本文選擇了SoC芯片廣泛使用的深亞微米CMOS工藝,實(shí)現(xiàn)了一個(gè)10位的高速DAC。該DAC可作為SoC設(shè)計(jì)中的IP硬核,在多種不同應(yīng)用領(lǐng)域的系統(tǒng)設(shè)計(jì)中實(shí)現(xiàn)復(fù)用。

2021-04-14 06:22:33

近年來,有關(guān)將CMOS工藝在射頻(RF)技術(shù)中應(yīng)用的可能性的研究大量增多。深亞微米技術(shù)允許CMOS電路的工作頻率超過1GHz,這無疑推動(dòng)了集成CMOS射頻電路的發(fā)展。目前,幾個(gè)研究組已利用標(biāo)準(zhǔn)

2019-08-22 06:24:40

,標(biāo)準(zhǔn)CMOS工藝技術(shù)在速度上仍有潛力可挖。 (1)隨著深亞微米工藝技術(shù)的開發(fā),標(biāo)準(zhǔn) CMOS工藝仍有速度潛力。 器件尺寸細(xì)微化一直是設(shè)計(jì)師追求的目標(biāo),器件尺寸小意味著寄生電容小,這種特性有利于制造高速

2018-11-26 16:45:00

化組織(ISO)7637和ISO 16750等行業(yè)標(biāo)準(zhǔn)給出的標(biāo)準(zhǔn)脈沖波形之外,還具有獨(dú)特且廣泛的傳導(dǎo)抗擾度測(cè)試套件。表1列出了幾種欠壓和過壓汽車瞬變特性。 瞬態(tài)原因幅度和持續(xù)時(shí)間相關(guān)標(biāo)準(zhǔn)負(fù)載突降高輸出

2019-03-19 06:45:10

CAD/CAE/CAM 一體化技術(shù)課題,以其中的三個(gè)關(guān)鍵性問題:沖壓方向的確定、壓料面的創(chuàng)建以及工藝補(bǔ)充的自動(dòng)添加為主要研究內(nèi)容,進(jìn)行了從理論分析到程序設(shè)計(jì)的深入研究,該研究成果作為大型覆蓋件模具智能

2009-04-16 13:34:15

背壓是什么?背壓是如何形成的?注塑成型工藝中的背壓到底有多重要?適當(dāng)調(diào)校背壓的好處有哪些?過高的背壓易出現(xiàn)哪些問題?如何去調(diào)校注塑背壓?

2021-07-13 08:38:01

不同特征尺寸的MOS晶體管,計(jì)算了由這些晶體管組成的靜態(tài)隨機(jī)存儲(chǔ)器(SRAM)單粒子翻轉(zhuǎn)的臨界電荷Qcrit、LET閾值(LETth),建立了LETth與臨界電荷之間的解析關(guān)系,研究了特征工藝尺寸

2010-04-22 11:50:00

幾個(gè)傳統(tǒng)的工藝如壓裝,注油,焊接等。其中壓裝工藝在電機(jī)裝配中應(yīng)用最多,也最為廣泛。如壓軸承到轉(zhuǎn)子,壓卡簧,壓硅鋼片到轉(zhuǎn)子,壓換向器,壓軸承到殼體等等。只是一個(gè)簡(jiǎn)單的壓裝其中涉及的知識(shí)點(diǎn)之深,也是讓人感嘆

2018-10-11 11:10:07

,還有幾個(gè)傳統(tǒng)的工藝如壓裝,注油,焊接等。 其中壓裝工藝在電機(jī)裝配中應(yīng)用最多,也最為廣泛。如壓軸承到轉(zhuǎn)子,壓卡簧,壓硅鋼片到轉(zhuǎn)子,壓換向器,壓軸承到殼體等等。只是一個(gè)簡(jiǎn)單的壓裝其中涉及的知識(shí)點(diǎn)之深

2023-03-08 16:21:51

程 序 控 制 電 壓 源 及 其 電 磁 兼 容 性 設(shè) 計(jì)

2012-08-20 16:14:23

礦山車輛胎壓監(jiān)測(cè)是以無損檢測(cè)技術(shù)為基礎(chǔ),通過研究車輛胎壓的實(shí)時(shí)信號(hào),了解礦山車輛的輪胎氣壓的變化特性,從而達(dá)到礦山車輛安全監(jiān)控提供依據(jù)。

2020-03-11 06:52:27

,電流也應(yīng)該是從s到d吧,那USBVCC怎么供電的呢?方向不對(duì)啊4、當(dāng)Vin是0的時(shí)候,通過穩(wěn)壓器不會(huì)輸出5V,所以G的電位經(jīng)過比較器的輸出應(yīng)該是0,S的電位因?yàn)榉€(wěn)壓器不會(huì)輸出5V所以也是0,這樣Vgs沒有壓差,不能滿足PMOS開通條件,那USBVCC是怎么供電的呢?

2016-09-22 10:56:56

各位,請(qǐng)問華強(qiáng)pcb的工藝可以打孔徑10mil,變徑20mil的過孔嗎?

2019-09-06 03:01:32

請(qǐng)問在Cadence中如何測(cè)量MOS電容的伏容特性曲線?

2021-06-24 06:53:00

因?yàn)樵O(shè)計(jì)電路需要正負(fù)10v的輸入電壓,因此設(shè)計(jì)高壓的柵壓自舉開關(guān),VDD=15 ,VSS=-15 CLK=-15到15 VIN幅值10電路工作狀態(tài)為CLK為高電平時(shí),上面接VDD的PMOS和下面接

2021-06-24 06:42:08

串聯(lián)諧振裝置用一節(jié)分壓器變比怎么計(jì)算?串聯(lián)諧振裝置介紹串聯(lián)諧振也稱為串聯(lián)諧振耐壓裝置,是替代直流耐壓采用工頻輸出的方式用于高電壓電氣設(shè)備的絕緣強(qiáng)度,串諧振是由變頻電源,勵(lì)磁變壓器,電抗器、補(bǔ)償,交流

2020-12-14 16:57:42

,G極電壓拉低,PMOS導(dǎo)通;而無負(fù)電, 即0V時(shí),NPN關(guān)斷,G極應(yīng)為6V,PMOS截止。但在仿真中,如附件所示,仿真結(jié)果不符。查詢datasheet,采用的IRF9130 PMOS管的開啟電壓Vth為 -4~-2V,仿真壓差在應(yīng)當(dāng)是符合的吧,但結(jié)果不符是為什么呢?

2019-11-06 01:33:07

全球知名的半導(dǎo)體廠商羅姆(ROHM)公司推出了采用CMOS工藝的具有超低電流消耗特性的高精度監(jiān)控IC,它們符合汽車應(yīng)用的AEC-Q100標(biāo)準(zhǔn),在整個(gè)工作溫度范圍內(nèi)釋放電壓精度為±50 mV。電壓監(jiān)控

2019-03-18 05:17:04

之前一直聽說Pmos的工藝難度難于Nmos,但是一直沒高清楚具體是為什么?不知道論壇的大大們有誰了解的,能給一個(gè)比較完整的答案。渣渣在這里拜謝了!!!!!

2015-05-07 17:07:11

本文在通過對(duì)多種傳統(tǒng)充電方式的研究,綜合各種方式的優(yōu)點(diǎn),提出了限壓變流脈沖充電方式,使實(shí)際充電電流接近充電可接受電流,縮短充電時(shí)間,并有效防止極化,快速、高效、安全。同時(shí),應(yīng)對(duì)電池組中單個(gè)電池狀態(tài)

2021-02-25 07:33:11

霍爾IC芯片的制造工藝霍爾IC傳感器是一種磁性傳感器,通過感應(yīng)磁場(chǎng)的變化,輸出不同種類的電信號(hào)。霍爾IC芯片主要有三種制造工藝,分別為 Bipolar、CMOS 和 BiCMOS 工藝,不同工藝的產(chǎn)品具有不同的電參數(shù)與磁參數(shù)特性。霍爾微電子柯芳(***)現(xiàn)為您分別介紹三種不同工藝產(chǎn)品的特點(diǎn)。

2016-10-26 16:48:22

CMOS觸發(fā)器在CP邊沿的工作特性研究

對(duì)時(shí)鐘脈沖(簡(jiǎn)稱CP)邊沿時(shí)間的要求,是觸發(fā)器品質(zhì)評(píng)價(jià)的重要指標(biāo)之一。觸發(fā)器只有在CP邊沿陡峭(短的邊沿時(shí)

2009-10-17 08:52:12 1622

1622

基于交叉耦合NMOS 單元,提出了一種低壓、快速穩(wěn)定的CMOS 電荷泵電路。一個(gè)二極管連接的NMOS 管與自舉電容相并聯(lián),對(duì)電路進(jìn)行預(yù)充電,從而改善了電荷泵電路的穩(wěn)定建立特性。PMOS 串聯(lián)開

2011-11-02 11:25:47 71

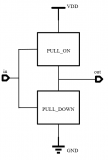

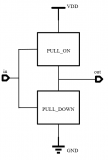

71 PMOS 驅(qū)動(dòng)電路 :

2012-04-01 15:31:21 14031

14031

研究了在熱載流子注入HCI(hot2carrier injection) 和負(fù)偏溫NBT (negative bias temperature) 兩種偏置條件下pMOS 器件的可靠性. 測(cè)量了pMOS 器件應(yīng)力前后的電流電壓特性和典型的器件參數(shù)漂移,并與單獨(dú)

2012-04-23 15:39:37 47

47 近年來,有關(guān)將CMOS工藝在射頻(RF)技術(shù)中應(yīng)用的可能性的研究大量增多。深亞微米技術(shù)允許CMOS電路的工作頻率超過1GHz,這無疑推動(dòng)了集成CMOS射頻電路的發(fā)展。目前,幾個(gè)研究組已利

2012-05-21 10:06:19 1850

1850

CMOS工藝,具體的是CMOS結(jié)構(gòu)對(duì)集成電路設(shè)計(jì)有幫助,謝謝

2016-03-18 15:35:52 21

21 不同吸油率油浸紙板介電特性及電導(dǎo)特性研究_徐征宇

2017-01-08 13:26:49 0

0 本文研究了在CMOS工藝中I/O電路的ESD保護(hù)結(jié)構(gòu)設(shè)計(jì)以及相關(guān)版圖的要求,其中重點(diǎn)討論了PAD到VSS電流通路的建立。

2017-09-07 18:29:51 7

7 近年來,有關(guān)將CMOS工藝在射頻(RF)技術(shù)中應(yīng)用的可能性的研究大量增多。深亞微米技術(shù)允許CMOS電路的工作頻率超過1GHz,這無疑推動(dòng)了集成CMOS射頻電路的發(fā)展。目前,幾個(gè)研究組已利用標(biāo)準(zhǔn)

2017-11-25 11:07:01 4628

4628

而mems即微機(jī)電系統(tǒng),是一門新興學(xué)科和領(lǐng)域,跟ic有很大的關(guān)聯(lián),當(dāng)然mems工藝也和cmos工藝會(huì)有很大的相似之處,現(xiàn)在的發(fā)展方向應(yīng)該是把二者集成到一套的工藝上來.

對(duì)mems不是特別的了)

2018-07-13 14:40:00 19763

19763 本文首先介紹了CMOS反相器的傳輸特性,其次介紹了cmos反相器概念,最后介紹了CMOS反相器的工作原理。

2018-08-16 14:51:04 22529

22529 由前面的基礎(chǔ)可知,CMOS只能實(shí)現(xiàn)基本邏輯的非,比如或邏輯,與邏輯,如果不加反相器,CMOS只能實(shí)現(xiàn)或非,與非邏輯。原因就是上拉邏輯只能用PMOS實(shí)現(xiàn),下拉邏輯只能由NMOS實(shí)現(xiàn),而PMOS的導(dǎo)通需要輸入信號(hào)為0,NMOS導(dǎo)通需要輸入信號(hào)為1。

2018-09-07 14:43:20 5465

5465

不兼容。PMOS因邏輯擺幅大,充電放電過程長,加之器件跨導(dǎo)小,所以工作速度更低,在NMOS電路(見N溝道金屬—氧化物—半導(dǎo)體集成電路)出現(xiàn)之后,多數(shù)已為NMOS電路所取代。只是,因PMOS電路工藝簡(jiǎn)單

2018-11-27 16:46:26 3162

3162 本文檔的主要內(nèi)容詳細(xì)介紹的是CMOS工藝制程技術(shù)的詳細(xì)資料說明。主要包括了:1.典型工藝技術(shù):①雙極型工藝技術(shù)② PMOS工藝技術(shù)③NMOS工藝技術(shù)④ CMOS工藝技術(shù)2.特殊工藝技術(shù)。BiCOMS工藝技術(shù),BCD工藝技術(shù),HV-CMOSI藝技術(shù)。

2019-01-08 08:00:00 75

75 隨著射頻無線通信事業(yè)的發(fā)展和移動(dòng)通訊技術(shù)的進(jìn)步,射頻的性能與速度成為人們關(guān)注的重點(diǎn),市場(chǎng)對(duì)其的需求也日益增多。目前,CMOS工藝是數(shù)字集成電路設(shè)計(jì)的主要工藝選擇,對(duì)于模擬與射頻集成電路來說,選擇

2020-09-25 10:44:00 2

2 不久前,MEMS 蝕刻和表面涂層方面的領(lǐng)先企業(yè) memsstar 向《電子產(chǎn)品世界》介紹了 MEMS 與傳統(tǒng) CMOS 刻蝕與沉積工藝的關(guān)系,對(duì)中國本土 MEMS 制造工廠和實(shí)驗(yàn)室的建議

2022-12-13 11:42:00 1674

1674 用MOS做高側(cè)開關(guān)時(shí),PMOS比NMOS更便于控制,不用額外的電荷泵升壓,柵極拉低和置高就能控制通斷。而隨著半導(dǎo)體工藝的進(jìn)步,PMOS在導(dǎo)通內(nèi)阻方面的參數(shù)漸漸好轉(zhuǎn),逐步縮小了與NMOS的差距,使得

2021-11-07 13:51:03 64

64 CMOS工藝流程介紹,帶圖片。

n阱的形成 1. 外延生長

2022-07-01 11:23:20 27

27 Pre-CMOS/MEMS 是指部分或全部的 MEMS 結(jié)構(gòu)在制作 CMOS 之前完成,帶有MEMS 微結(jié)構(gòu)部分的硅片可以作為 CMOS 工藝的初始材料。

2022-10-13 14:52:43 5875

5875 CMOS 集成電路的基礎(chǔ)工藝之一就是雙阱工藝,它包括兩個(gè)區(qū)域,即n-MOS和p-MOS 有源區(qū)

2022-11-14 09:34:51 6645

6645 在網(wǎng)上查了一些關(guān)于 PMOS 和 NMOS 哪個(gè)更適合用于電源開關(guān)這種場(chǎng)合,大部分都是從工藝,導(dǎo)通電阻 Rds 來解釋,但隨著半導(dǎo)體工藝的進(jìn)步,現(xiàn)今的 PMOS 與 NMOS 之間差距已經(jīng)不大了,從 SOT-23 的封裝來看,兩者的大小也是差不多的。個(gè)人覺得,PMOS 用于電源開關(guān)更多是為了方便控制。

2023-03-10 13:49:59 4763

4763

利用CMOS設(shè)計(jì)電路需先自行學(xué)習(xí)NMOS和PMOS的基本原理。

2023-04-11 09:01:56 4871

4871 CMOS工藝是在PMOS和NMOS工藝基礎(chǔ)上發(fā)展起來的。

2023-07-06 14:25:01 1786

1786

因?yàn)?b class="flag-6" style="color: red">CMOS工藝易于集成化,并且相對(duì)較低的電路功耗,所以。個(gè)人電腦、互聯(lián)網(wǎng)絡(luò)和數(shù)字革命,強(qiáng)烈推動(dòng)了對(duì)CMOS集成電路芯片的需求,基于CMOS工藝設(shè)計(jì)、加工、生產(chǎn)出來的芯片是電子工業(yè)中最常見的IC芯片

2023-07-24 17:05:38 1131

1131

等。CMOS反相器的工作原理是利用n型金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(NMOS)和p型金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(PMOS)兩種晶體管的互補(bǔ)特性,將它們組合成一個(gè)電路,以實(shí)現(xiàn)信號(hào)的放大、邏輯變換等功能。 在CMOS反相器中,NMOS和PMOS晶體管的連接方式相對(duì)固定,即

2023-09-12 10:57:24 1753

1753 PMOS和NMOS是金屬-氧化物-半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET)的兩種類型。 PMOS和NMOS是MOSFET的兩種互補(bǔ)型式,也稱為CMOS技術(shù),其中C代表互補(bǔ)(Complementary

2023-12-07 09:15:36 1025

1025 NMOS和PMOS是常見的MOSFET(金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管)的兩種類型,它們?cè)陔娮悠骷衅鸬讲煌淖饔谩MOS和PMOS的符號(hào)和電路結(jié)構(gòu)差異體現(xiàn)了它們的不同工作原理和特性。接下來,我們

2023-12-18 13:56:22 1530

1530 影響CMOS反相器特性的因素? CMOS反相器是一種常見的數(shù)字電路,用于將輸入信號(hào)取反輸出。它由一個(gè)P型MOS管和一個(gè)N型MOS管組成,通過控制兩個(gè)管的開關(guān)狀態(tài),實(shí)現(xiàn)輸入信號(hào)的取反輸出。CMOS

2024-01-26 14:21:10 277

277 BCD(Bipolar-CMOS-DMOS)工藝技術(shù)是將雙極型晶體管、CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)和DMOS(雙擴(kuò)散金屬氧化物半導(dǎo)體)晶體管技術(shù)組合在單個(gè)芯片上的高級(jí)制造工藝。

2024-03-18 09:47:41 186

186

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論