設(shè)計(jì)背景: 二進(jìn)制轉(zhuǎn)十進(jìn)制在設(shè)計(jì)應(yīng)用中十分的廣泛。尤其在AD轉(zhuǎn)化中是必須所用到的一個(gè)小知識(shí)點(diǎn),學(xué)習(xí)二進(jìn)制轉(zhuǎn)十進(jìn)制的方法顯的非常的重要。今天就和筆者來(lái)學(xué)習(xí)二進(jìn)制轉(zhuǎn)十進(jìn)制的方法,通過(guò)簡(jiǎn)單的學(xué)習(xí)來(lái)掌握這么

2018-09-20 09:38:39 15588

15588

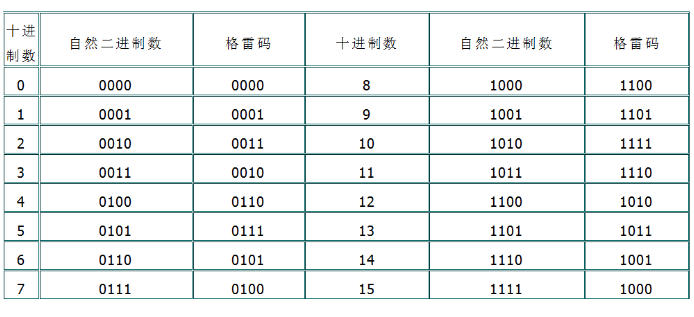

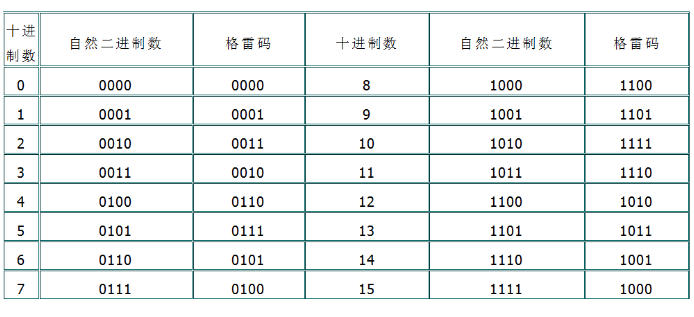

其中采用循環(huán)二進(jìn)制編碼的絕對(duì)式編碼器,其輸出信號(hào)是一種數(shù)字排序,不是權(quán)重碼,每一位沒(méi)有確定的大小,不能直接進(jìn)行比較大小和算術(shù)運(yùn)算,也不能直接轉(zhuǎn)換成其他信號(hào),要經(jīng)過(guò)一次碼變換,變成自然二進(jìn)制碼。

2020-09-23 16:23:04 6149

6149 要求:在ICEcube2 中任選一款芯片,在選擇的芯片上設(shè)計(jì)一個(gè)二進(jìn)制序列檢測(cè)器,當(dāng)檢測(cè)到1010序列時(shí),計(jì)數(shù)器加1,規(guī)定檢測(cè)到一次之后,檢測(cè)器不必回到最初狀態(tài),比如序列0110101011,檢測(cè)器

2014-03-26 14:52:27

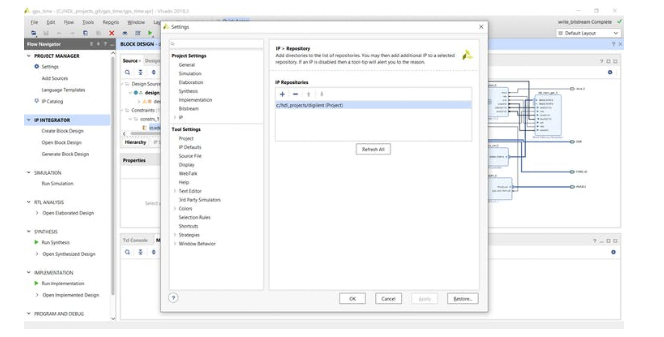

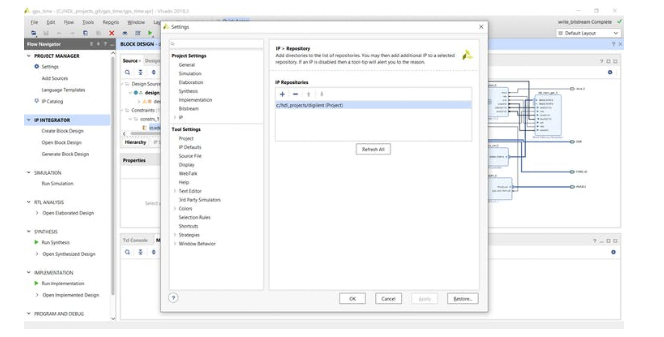

即使在看過(guò)這么多論壇之后,我一直很困惑為我的二進(jìn)制序列檢測(cè)器選擇fpga。最初我想為我的應(yīng)用程序選擇spartan 3E FPGA板,但由于它的成本我拒絕它。我現(xiàn)在對(duì)Elbert感興趣V2

2020-03-23 06:19:19

在文檔中寫(xiě)道,如果啟用閃存加密,加密后的二進(jìn)制文件將存儲(chǔ)到 IRAM 中。如果存儲(chǔ)了整個(gè)二進(jìn)制文件或以某種方式部分執(zhí)行,我找不到更多詳細(xì)信息。因此,我會(huì)問(wèn)是否啟用了加密,二進(jìn)制大小是否限于 IRAM 大小?

2023-04-11 06:35:01

二進(jìn)制控制8位燈的明暗,如何實(shí)現(xiàn)?如111,要求低三位亮,高五位暗,高手指導(dǎo)下!

2012-04-25 16:12:08

置位( 置 1) 其余的幾位, 則可以用另外一個(gè) 8 位二進(jìn)制數(shù)去相“或” , 這個(gè) 8 位二進(jìn)制數(shù)在要保留的相應(yīng) 位上為 0, 在要置位的相應(yīng)位上為 1。例如, 要置位第 0、 3、 7 位而其

2019-12-25 16:36:41

請(qǐng)教各位大神如何將一個(gè)十進(jìn)制數(shù)組變成二進(jìn)制顯示??我是初學(xué)者,在數(shù)組屬性里的顯示格式里,二進(jìn)制不可選,是不是需要數(shù)據(jù)轉(zhuǎn)換???請(qǐng)各位大神不吝賜教,謝謝!!!!!!!

2014-11-28 11:21:16

位、13位、14位或更高位等多種。其中采用循環(huán)二進(jìn)制編碼的絕對(duì)式編碼器,其輸出信號(hào)是一種數(shù)字排序,不是權(quán)重碼,每一位沒(méi)有確定的大小,不能直接進(jìn)行比較大小和算術(shù)運(yùn)算,也不能直接轉(zhuǎn)換成其他信號(hào),要經(jīng)過(guò)一次

2011-03-08 14:16:59

本帖最后由 gk320830 于 2015-3-9 06:39 編輯

二進(jìn)制碼 數(shù)字系統(tǒng)中的信息可分為兩類,一類是數(shù)值,另一類是文字符號(hào)(包括控制符)。 代碼:采用一定位數(shù)的二進(jìn)制數(shù)碼來(lái)

2009-04-06 23:55:36

用二進(jìn)制計(jì)數(shù)器實(shí)現(xiàn)控制選擇不同的開(kāi)關(guān),電路輸入信號(hào)為一路方波,當(dāng)此信號(hào)的第一個(gè)方波信號(hào)輸入時(shí),電路使用開(kāi)關(guān)1,當(dāng)此信號(hào)的第二個(gè)方波信號(hào)輸入時(shí),電路使用開(kāi)關(guān)2,本人小白,麻煩回答具體點(diǎn),附上簡(jiǎn)單的電路圖,謝謝啦

2017-06-26 09:30:44

怎樣分段讀取二進(jìn)制文件啊,比如我想讀取任意時(shí)間段的一段數(shù)據(jù),求大神幫助

2015-09-08 15:25:07

在LabVIEW中,如何實(shí)現(xiàn)一個(gè)十六進(jìn)制的數(shù)取反后加1,如FFFFFFCB表示為二進(jìn)制是11111111111111111111111111001011,取反后

2014-03-15 00:32:43

實(shí)現(xiàn)兩個(gè)二進(jìn)制除法運(yùn)算,并在八個(gè)七段數(shù)碼管上進(jìn)行顯示實(shí)現(xiàn)兩個(gè)二進(jìn)制除法運(yùn)算,并在八個(gè)七段數(shù)碼管上進(jìn)行顯示實(shí)現(xiàn)兩個(gè)二進(jìn)制除法運(yùn)算,并在八個(gè)七段數(shù)碼管上進(jìn)行顯示

2013-11-01 20:34:01

求助,這個(gè)序列信號(hào)發(fā)生器已經(jīng)用計(jì)數(shù)器和數(shù)據(jù)選擇器能設(shè)計(jì)出來(lái)了,但是檢測(cè)器百度不到怎么設(shè)計(jì)看不懂求指教

2018-01-16 12:57:14

小妹在做一個(gè)心電信號(hào)發(fā)生器 其中從ACCESS數(shù)據(jù)庫(kù)中需要讀一個(gè)WaveData.data 的長(zhǎng)二進(jìn)制數(shù)據(jù) 這是心電圖波形的數(shù)據(jù) 每個(gè)圖500個(gè)點(diǎn)每個(gè)點(diǎn)2字節(jié)。怎么才能讀出這個(gè)長(zhǎng)二進(jìn)制數(shù)據(jù)?用變體么?

2014-10-26 20:51:14

Labview種如何將一個(gè)數(shù)字轉(zhuǎn)換為5位二進(jìn)制,8位二進(jìn)制以及任意位的二進(jìn)制表示呢

2018-01-22 17:22:31

`各位大神,我想把一張圖片通過(guò)變成二進(jìn)制通過(guò)TCP傳輸,現(xiàn)在我把圖片轉(zhuǎn)換成二進(jìn)制文件,但文件只有1KB大小。我想讀取但是不知道二進(jìn)制的圖片數(shù)據(jù)類型。能否幫我畫(huà)一個(gè)簡(jiǎn)易的讀取二進(jìn)制圖片的程序,謝謝`

2017-12-29 09:26:42

應(yīng)用程序 : 示例代碼演示了如何丟棄函數(shù)的二進(jìn)制代碼, 然后填入 SRAM 的二進(jìn)制代碼, 然后調(diào)用它 。

BSP版本:M451系列BSP V3.01.001

硬件: 任何 M451 系列板塊

2023-08-30 07:35:31

c語(yǔ)言的二進(jìn)制是如何轉(zhuǎn)為十進(jìn)制的?其源碼是什么?

2021-07-15 12:04:43

我想把一個(gè)15000個(gè)點(diǎn)的一位數(shù)組存儲(chǔ)為二進(jìn)制文件,但是不知道是存儲(chǔ)的速率不夠還是其他什么原因,存儲(chǔ)后我再讀取只有5000個(gè)點(diǎn)。程序如圖所示。請(qǐng)高人指點(diǎn)啊,我不知道二進(jìn)制存儲(chǔ)的速率到底是多大,是不是存儲(chǔ)速率不夠還是怎么的

2014-03-03 09:31:32

想問(wèn)一下怎樣去二進(jìn)制讀取簇類型的數(shù)組

2019-03-28 09:41:11

`我現(xiàn)在將一個(gè)動(dòng)態(tài)二維數(shù)組存到二進(jìn)制文件中,這個(gè)二維數(shù)組的數(shù)值一秒變一次,每變一次就保存到二進(jìn)制文件中,但是最后我發(fā)現(xiàn)保存下來(lái)的數(shù)只是最后一秒的,就好像每次保存都是替換文件所有內(nèi)容,如何修改成不替換呢?`

2020-08-07 09:53:53

二進(jìn)制中表示為00001010=(23)+(21)), LED的1和3點(diǎn)亮,其他LED為熄滅。 選擇自動(dòng)方式時(shí),滑動(dòng)條自動(dòng)進(jìn)行加1操作,實(shí)現(xiàn)0到255的循環(huán)計(jì)數(shù);同時(shí)8個(gè)LED會(huì)實(shí)時(shí)顯示滑動(dòng)條數(shù)值所對(duì)應(yīng)二進(jìn)制數(shù)值。當(dāng)滑動(dòng)條大于255時(shí),自動(dòng)回0并重新由0開(kāi)始計(jì)數(shù)。

2018-12-07 22:20:10

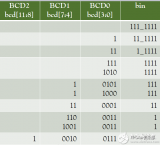

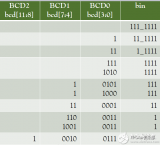

的作用。它的操作可以歸納如下:1.對(duì)于BCD移位寄存器中的每4位的BCD數(shù)字,檢測(cè)這個(gè)數(shù)是否大于4。如果是,就在這個(gè)數(shù)字上加上一個(gè)3。2.將整個(gè)BCD寄存器向左移動(dòng)一位,將輸入二進(jìn)制序列的最高有效位

2017-01-09 14:38:01

實(shí)現(xiàn)方式比較耗費(fèi)資源,下面夢(mèng)翼師兄會(huì)介紹一種算法,這種算法需要用到加法和移位來(lái)完成BCD轉(zhuǎn)二進(jìn)制數(shù)的功能,從而盡可能的節(jié)約邏輯資源。移位算法原理在介紹這種算法之前,夢(mèng)翼師兄先來(lái)解釋一個(gè)小小的

2019-12-03 21:48:59

我注意到在 BSP 2.0.0 中構(gòu)建了兩種不同的 TF-A 二進(jìn)制文件,一種安裝為 fsbl,另一種僅用于與 STM32CubeProgrammer(“serialboot”二進(jìn)制文件)通信。我

2023-01-17 08:48:41

在LABVIEW中使用二進(jìn)制讀寫(xiě)節(jié)點(diǎn)時(shí),遇到一個(gè)奇怪的問(wèn)題,當(dāng)我通過(guò)新建文件創(chuàng)建二進(jìn)制文件(見(jiàn)第一張圖),之后將數(shù)據(jù)寫(xiě)入到二進(jìn)制文件中(見(jiàn)第二張圖),最后讀取二進(jìn)制文件(見(jiàn)第三張圖)。現(xiàn)在問(wèn)題是當(dāng)我

2017-09-30 15:03:01

基于改進(jìn)的ADALINE神經(jīng)網(wǎng)絡(luò)的DTMF檢測(cè)算法基于改進(jìn)的ADALINE神經(jīng)網(wǎng)絡(luò)的DTMF解碼仿真結(jié)果分享一種DTMF信號(hào)檢測(cè)器工程的應(yīng)用方案

2021-06-03 07:03:11

十進(jìn)制和二進(jìn)制之間的轉(zhuǎn)換 既然一個(gè)數(shù)可以用二進(jìn)制和十進(jìn)制兩種不同形式來(lái)表示,那么兩著之間就必然有一定的轉(zhuǎn)換關(guān)系。 由十進(jìn)制數(shù)的一般表示式: 可以得到整數(shù)的一般表達(dá)式: 將等式兩邊分別除以2

2009-04-06 23:54:14

找出一種具有十個(gè)不同穩(wěn)定狀態(tài)的電子元件則是相當(dāng)困難的。在二進(jìn)制中,只有二個(gè)數(shù)0和1,這正好和電子元件的兩個(gè)不同穩(wěn)定狀態(tài)相對(duì)應(yīng)。例如,以1代表高電平,則0代表低電平,這樣,采用二進(jìn)制后,就可以利用二值

2019-12-10 10:55:42

labview如何實(shí)現(xiàn)分段讀取二進(jìn)制文件的內(nèi)容?可讀取二進(jìn)制文件內(nèi)容的任意一段數(shù)據(jù)

2019-11-01 15:42:34

1、實(shí)現(xiàn)一個(gè)二進(jìn)制轉(zhuǎn)十進(jìn)制的電路設(shè)計(jì)本文實(shí)現(xiàn)一個(gè)二進(jìn)制轉(zhuǎn)十進(jìn)制的電路,8位撥碼開(kāi)關(guān)(SW7-SW0)作為一組8位二進(jìn)制輸入信號(hào),程序?qū)?位二進(jìn)制輸入轉(zhuǎn)為3位十進(jìn)制表示,經(jīng)由數(shù)碼管顯示輸出。在數(shù)

2022-07-12 16:41:42

一個(gè)8位二進(jìn)制數(shù)經(jīng)過(guò)二進(jìn)制LDPC編碼器編碼后等到一個(gè)幾位二進(jìn)制的數(shù),怎么計(jì)算的?

2017-03-14 13:07:56

應(yīng)用程序 : 示例代碼演示了如何丟棄函數(shù)的二進(jìn)制代碼, 然后填入 SRAM 的二進(jìn)制代碼, 然后調(diào)用它 。

BSP版本:M451系列BSP V3.01.001

硬件: 任何 M451 系列板塊

2023-08-23 06:34:10

如何使用二進(jìn)制信號(hào)量。如何去判斷二進(jìn)制信號(hào)量 0和1.看來(lái)書(shū)寫(xiě)的是空的時(shí)候?yàn)?.滿的時(shí)候?yàn)?,但是如何去判斷0和1。

2020-06-15 03:19:50

我想制作一個(gè)以8個(gè)LED的形式實(shí)現(xiàn)二進(jìn)制計(jì)數(shù)器。該計(jì)數(shù)器通過(guò)USART發(fā)送一個(gè)8位二進(jìn)制數(shù),并讓8個(gè)LED顯示數(shù)字(如果位為0,則指示燈熄滅,當(dāng)位為1時(shí)指示燈亮)。這樣做的最佳方法是什么?

2018-10-08 14:07:42

如何去實(shí)現(xiàn)一個(gè)2位二進(jìn)制乘法器的設(shè)計(jì)呢?如何對(duì)2位二進(jìn)制乘法器進(jìn)行仿真呢?

2021-11-03 06:04:56

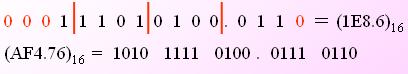

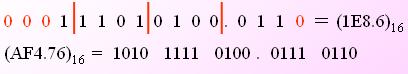

(11100101.11101011)2轉(zhuǎn)換成八進(jìn)制數(shù)。 (11100101.11101011)2=(345.353)8(3)二進(jìn)制轉(zhuǎn)換為十六進(jìn)制:采用的是“四位一并法”,整數(shù)部分從低位開(kāi)始,每四位二進(jìn)制數(shù)為一組

2019-12-11 17:49:02

請(qǐng)哪位大神告訴我上圖 子VI 的程序框圖,感激不盡。如果有其它用LabVIEW生成二進(jìn)制序列方法,并可用于仿真2ASK的,也可以告訴我~~

2015-05-08 07:24:55

IAR怎么輸出二進(jìn)制BIN文件?

2023-08-28 17:19:05

和逆向工具并且依賴我們的黑客直覺(jué)來(lái)掌控我們正在逆向的目標(biāo)程序。我們必須理解二進(jìn)制格式、內(nèi)存布局和給定處理器指令集的復(fù)雜性。我們因此成為微處理器上的程序的主人。一個(gè)逆向工程師對(duì)二進(jìn)制控制藝術(shù)很嫻熟。本書(shū)將為

2019-07-18 06:25:37

設(shè)定二進(jìn)制電平。此外,該解決方案可實(shí)現(xiàn)小于 ±3.0%(±1V 測(cè)量值步長(zhǎng))的電壓檢測(cè)誤差,同時(shí)提供大于 2kV RMS 的可靠隔離性。主要特色高精度電壓測(cè)量功能(誤差小于 ±3%)一種能夠處理 18V

2018-09-20 08:55:55

如何用multisim軟件將速率為Rb的二進(jìn)制碼元序列分為兩路,速率為Rb/2

2013-10-30 08:01:20

怎樣使用獨(dú)立按鍵實(shí)現(xiàn)二進(jìn)制加法計(jì)算的編程呢?怎樣通過(guò)觀察LED燈的亮滅來(lái)檢測(cè)延時(shí)函數(shù)是否正確?

2022-02-23 07:26:55

提取一個(gè)8位二進(jìn)制數(shù)的低3位和另一個(gè)8位二進(jìn)制數(shù)的高5位,然后組合成一個(gè)新的8位二進(jìn)制數(shù),用C語(yǔ)言怎么實(shí)現(xiàn)?

2019-01-17 06:35:14

改進(jìn)的二進(jìn)制搜索算法原理是什么?改進(jìn)的二進(jìn)制搜索算法有什么優(yōu)勢(shì)?

2021-05-20 07:12:57

分從后向前遍歷的方式遍歷(分解).直到不可分.即可 * 實(shí)現(xiàn)按序號(hào)所描述順序遍歷二進(jìn)制碼.如果,按此順序遍歷二進(jìn)制碼,我們可 * 以很方便地在序列中找到所要的二進(jìn)制碼與其對(duì)應(yīng)的格雷碼.本思想可以很

2011-04-22 09:00:58

這個(gè)bcd碼和二進(jìn)制有什么關(guān)系?

bcd 表示0011001是19(十進(jìn)制)

二進(jìn)制表示0011001是25(十進(jìn)制)

這個(gè)怎么確定是哪個(gè)???

2023-10-07 06:02:17

學(xué)習(xí)labview讀取二進(jìn)制文件時(shí)遇到難題,請(qǐng)各位大師指教,錯(cuò)誤如圖。

2012-09-06 19:01:58

M序列(二進(jìn)制偽隨機(jī)序列)電路圖

2013-04-29 17:03:48

目錄1. 集成四位二進(jìn)制計(jì)數(shù)器【74LVC161】(1) 邏輯符號(hào)(2) 功能表(3) 應(yīng)用① 構(gòu)成任意模數(shù)的計(jì)數(shù)器a. 反饋清零法b. 反饋置數(shù)法c. 位數(shù)拓展② 構(gòu)成分頻器③ 構(gòu)成序列信號(hào)發(fā)生器

2021-07-29 07:20:09

提出一種在二進(jìn)制環(huán)境下挖掘緩沖區(qū)溢出漏洞的方法。結(jié)合動(dòng)態(tài)與靜態(tài)挖掘技術(shù)對(duì)二進(jìn)制環(huán)境下的程序作進(jìn)一步的漏洞查找。靜態(tài)方法主要對(duì)二進(jìn)制程序中函數(shù)棧幀的特征和匯編語(yǔ)

2009-04-10 09:54:21 27

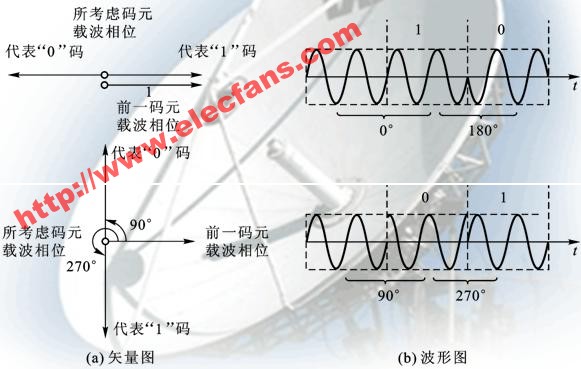

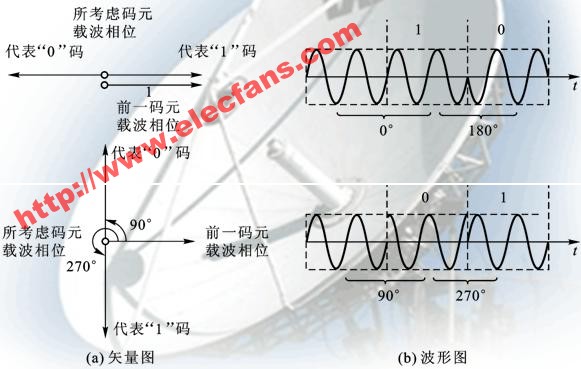

27 二進(jìn)制相對(duì)調(diào)相(二進(jìn)制差分調(diào)相2DPSK)的工作原理

2008-10-21 13:01:35 3057

3057

二進(jìn)制

二進(jìn)制與十進(jìn)制的區(qū)別在于數(shù)碼的個(gè)數(shù)和進(jìn)位規(guī)律有很大的區(qū)別,顧名思義,二進(jìn)制的計(jì)數(shù)規(guī)律為逢二進(jìn)一,是以2為基數(shù)的計(jì)數(shù)體制。10這個(gè)數(shù)在二進(jìn)

2009-04-06 23:48:01 7548

7548

十進(jìn)制和二進(jìn)制之間的轉(zhuǎn)換

既然一個(gè)數(shù)可以用二進(jìn)制和十進(jìn)制兩種不同形式來(lái)表示,那么兩著之間就必然有一定的轉(zhuǎn)換關(guān)系。 由十進(jìn)制數(shù)的一

2009-04-06 23:53:36 8086

8086

二進(jìn)制碼

數(shù)字系統(tǒng)中的信息可分為兩類,一類是數(shù)值,另一類是文字符號(hào)(包括控制符)。 代碼:采用一定位數(shù)的二進(jìn)制數(shù)碼來(lái)表示文字符號(hào)

2009-04-06 23:55:00 3954

3954

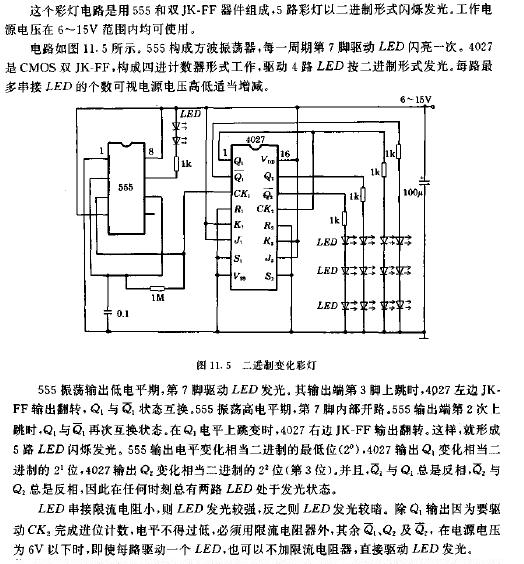

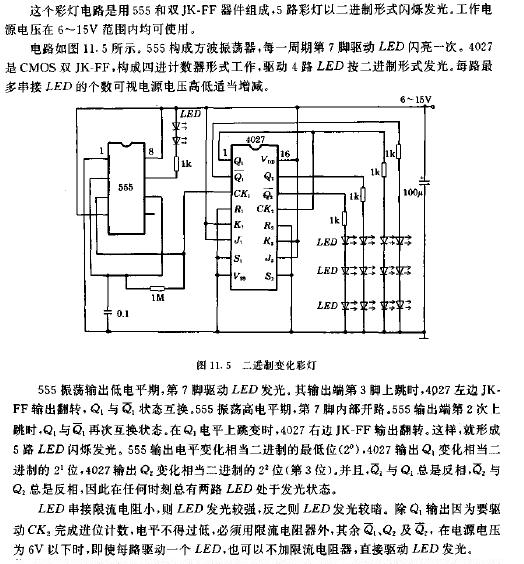

二進(jìn)制變化彩燈

2009-04-09 17:52:31 1273

1273

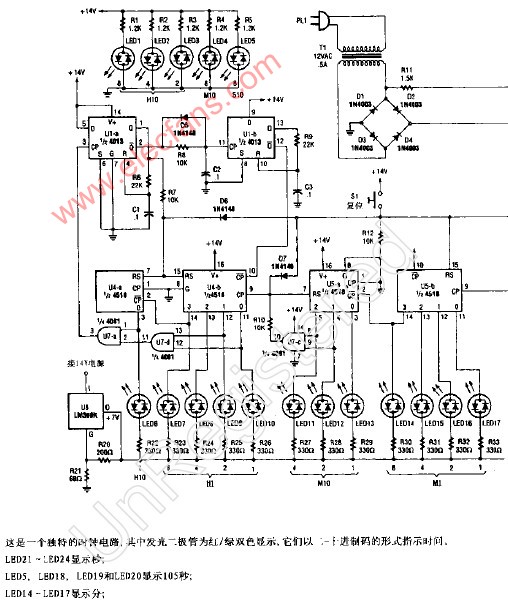

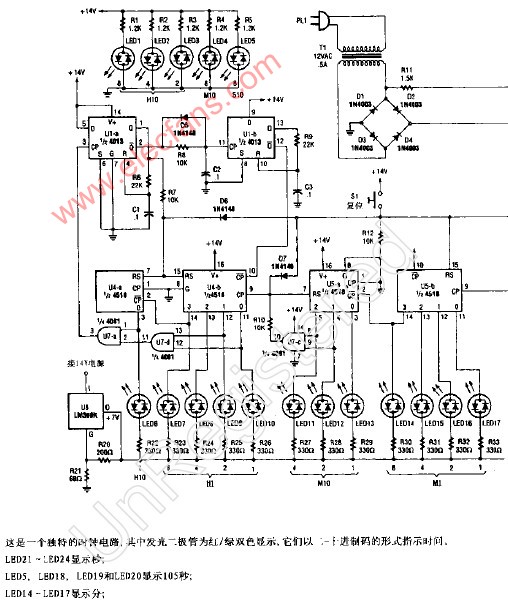

二進(jìn)制時(shí)鐘電路

2009-09-11 11:22:46 2992

2992

二進(jìn)制數(shù)與十六進(jìn)制數(shù)的相互轉(zhuǎn)換

二進(jìn)制數(shù)與十六進(jìn)制數(shù)的相互轉(zhuǎn)換,按照每4位二進(jìn)制數(shù)對(duì)應(yīng)于一位十六進(jìn)制數(shù)進(jìn)行轉(zhuǎn)換。

2009-09-24 11:28:58 9461

9461

同步二進(jìn)制計(jì)數(shù)器

1. 同步與異步二進(jìn)制加法計(jì)數(shù)器比較態(tài)序表和工作波形一樣電路結(jié)構(gòu)不同: 異步二進(jìn)制加法

2009-09-30 18:37:29 11186

11186

二進(jìn)制編碼和二進(jìn)制數(shù)據(jù)

二進(jìn)制編碼是計(jì)算機(jī)內(nèi)使用最多的碼制,它只使用兩個(gè)基本符號(hào)"0"和"1",并且通過(guò)由這兩個(gè)符號(hào)組成的

2009-10-13 16:22:51 4459

4459 二進(jìn)制數(shù)的運(yùn)算規(guī)則 二進(jìn)制數(shù)之間可以執(zhí)行算術(shù)運(yùn)算和邏輯運(yùn)算,其規(guī)則簡(jiǎn)單,容易實(shí)現(xiàn)。 (1) 加法運(yùn)算規(guī)則 0 + 0 = 0 例如:

2009-10-13 16:24:15 22294

22294 什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

計(jì)數(shù)器是數(shù)字系統(tǒng)中用得較多的基本邏輯器件。它不僅能記錄輸入時(shí)鐘脈沖的個(gè)數(shù),還可以實(shí)現(xiàn)

2010-03-08 13:16:34 30352

30352 二進(jìn)制電平,什么是二進(jìn)制電平

在二進(jìn)制數(shù)字通信系統(tǒng)中,每個(gè)碼元或每個(gè)符號(hào)只能是“1”和“0”兩個(gè)狀態(tài)之一。若將每個(gè)碼元可能取的狀態(tài)增

2010-03-17 16:51:58 2255

2255 本的二進(jìn)制加法/減法器,本的二進(jìn)制加法/減法器原理

兩個(gè)二進(jìn)制數(shù)字Ai,Bi和一個(gè)進(jìn)位輸入Ci相加,產(chǎn)生一個(gè)和輸出Si,以及一個(gè)進(jìn)位輸

2010-04-13 11:11:55 5132

5132 十進(jìn)制數(shù)的二進(jìn)制編碼

在人機(jī)交互過(guò)程中,為了既滿足系統(tǒng)中使用二進(jìn)制數(shù)的要求,又適應(yīng)人們使用十進(jìn)制數(shù)的習(xí)慣

2010-05-02 19:04:06 8947

8947 序列信號(hào)發(fā)生器

序列信號(hào)是指在同步脈沖作用下循環(huán)地產(chǎn)生一串周期性的二進(jìn)制信號(hào).能產(chǎn)

2010-09-18 08:37:14 7127

7127

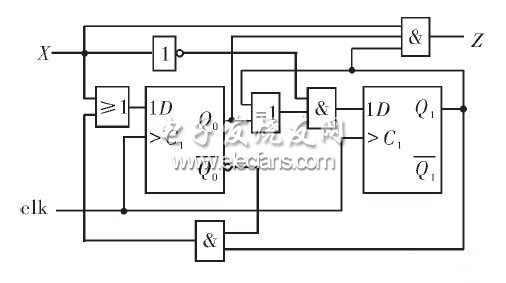

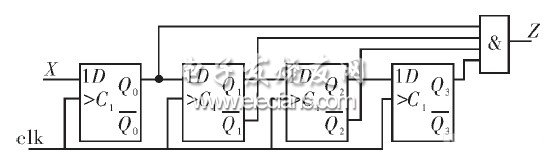

介紹了一種二進(jìn)制序列信號(hào)檢測(cè)器的3種設(shè)計(jì)方法,該電路可應(yīng)用于安全防盜、密碼認(rèn)證等加密場(chǎng)合,以及在海量數(shù)據(jù)中對(duì)敏感信息的自動(dòng)偵聽(tīng)。電路采用數(shù)字系統(tǒng)設(shè)計(jì)方法,步驟程序化,電

2011-10-19 15:19:37 41

41 二進(jìn)制加法程序【匯編版】二進(jìn)制加法程序【匯編版】二進(jìn)制加法程序【匯編版】二進(jìn)制加法程序【匯編版】

2015-12-29 11:02:06 0

0 二進(jìn)制加法程序【C語(yǔ)言版】二進(jìn)制加法程序【C語(yǔ)言版】二進(jìn)制加法程序【C語(yǔ)言版】二進(jìn)制加法程序【C語(yǔ)言版】

2015-12-29 11:03:51 0

0 SAR開(kāi)關(guān)時(shí)序的非二進(jìn)制結(jié)構(gòu)

2017-04-05 16:08:27 5

5 格雷碼,又叫循環(huán)二進(jìn)制碼或反射二進(jìn)制碼,格雷碼是我們?cè)诠こ讨谐?huì)遇到的一種編碼方式,它的基本的特點(diǎn)就是任意兩個(gè)相鄰的代碼只有一位二進(jìn)制數(shù)不同,這點(diǎn)在下面會(huì)詳細(xì)講解到。格雷碼的基本特點(diǎn)就是任意兩個(gè)相鄰的代碼只有一位二進(jìn)制數(shù)不同。

2018-03-02 15:48:53 16613

16613

CD4040組成加法計(jì)數(shù)器,手動(dòng)加1計(jì)數(shù)。

2.二進(jìn)制與十進(jìn)制數(shù)字對(duì)照顯示實(shí)驗(yàn) 本電路可以形象地顯示0~9的二進(jìn)制數(shù)。按動(dòng)加1按鈕AN2,計(jì)數(shù)器的輸入端CP得到一個(gè)負(fù)脈沖信號(hào),計(jì)數(shù)器進(jìn)行

2018-09-20 18:26:41 2326

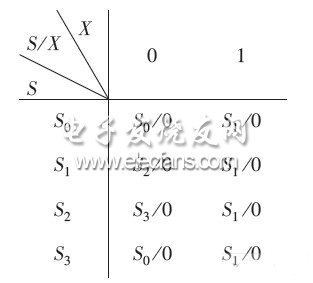

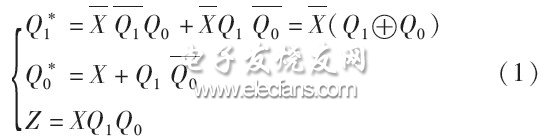

2326 信號(hào),當(dāng)序列檢測(cè)器連續(xù)收到一組串行二進(jìn)制碼后,如果這組碼與檢測(cè)器中預(yù)先設(shè)置的碼相同,則輸出為1,否則為0,由于這種檢測(cè)的關(guān)鍵在于正確碼的收到必須是連續(xù)的,這要求檢測(cè)器必須記住前一次的正確碼及正確序列,直到在連續(xù)的檢測(cè)中所收到的每一位碼都

2020-09-09 15:33:00 37

37 基于FPGA的二進(jìn)制相移鍵控設(shè)計(jì)方案

2021-05-28 09:36:50 11

11 本方案是一個(gè)基于FPGA的二進(jìn)制時(shí)鐘,使用GPS作為時(shí)間參考。

2022-05-13 17:41:31 1786

1786

將二進(jìn)制數(shù)視為元胞自動(dòng)機(jī)可能有助于數(shù)字二進(jìn)制計(jì)數(shù)器的設(shè)計(jì)和實(shí)現(xiàn)嗎?

2022-07-28 11:47:10 1181

1181

二進(jìn)制最佳接收原理 二進(jìn)制最佳接收機(jī)的實(shí)現(xiàn)形式有哪兩種? 二進(jìn)制最佳接收原理是計(jì)算機(jī)通信中的重要概念,它是指在二進(jìn)制通信中通過(guò)一定的方法,使接收機(jī)在信號(hào)傳輸過(guò)程中能夠準(zhǔn)確、可靠地接收到發(fā)送端傳輸

2023-11-27 16:19:07 429

429 計(jì)算機(jī)內(nèi)部一般也是8位的倍數(shù)(8位= 1字節(jié)),所以每個(gè)字節(jié)可以方便地用2個(gè)十六進(jìn)制數(shù)字表示。對(duì)于工程師來(lái)說(shuō),這比長(zhǎng)的二進(jìn)制數(shù)字序列更容易處理,但是計(jì)算機(jī)內(nèi)部仍然是以2為基數(shù)的二進(jìn)制數(shù)字系統(tǒng)。

2023-11-28 10:45:25 516

516

如何實(shí)現(xiàn)二進(jìn)制和BCD碼數(shù)據(jù)的相互轉(zhuǎn)變? 二進(jìn)制碼是將十進(jìn)制數(shù)字表示為二進(jìn)制數(shù)和十進(jìn)制數(shù)的一種表示方法。在計(jì)算機(jī)系統(tǒng)中,二進(jìn)制數(shù)是最基本的數(shù)制表示方法,而B(niǎo)CD碼則是用于將數(shù)字直接轉(zhuǎn)換為二進(jìn)制

2024-02-18 14:51:58 215

215

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論