1引言

本文依據測試結果進行研究,給出10 Hz~1 MHz TTL信號下競爭冒險的成因見解。

2 競爭冒險的測試

2.1 競爭冒險概念

在數字電路中,如果輸入端信號之間存在著時間延遲[1],那么輸出端有可能產生干擾脈沖 [1-2]。當干擾脈沖幅度達到開門電平,對后級電路、敏感電路將會造成危害。將時間延遲比作競爭,干擾脈沖比作冒險,即所謂的“競爭冒險”。競爭冒險的核心是干擾脈沖,研究競爭冒險實質是研究干擾脈沖。

2.2 測試電路

經過對多種邏輯電路的試驗和比較,能同時在脈沖信號上升沿、下降沿產生干擾脈沖,異或門表現突出。現以異或門74LS86芯片為例,設計出7 級異或門競爭冒險測試電路。

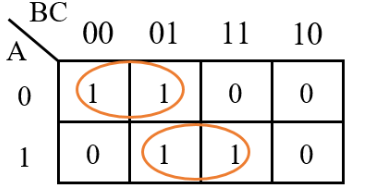

異或運算表達式:Z = AB+AB,其輸入相同(0 0,1 1),輸出為0;輸入不同(0 1,1 0),則輸出為1。若將A、H端接入TTL數字信號源, B~G端接1態,分析奇數門A7的輸入和輸出。信號源初始態假設為0,即H為0,Z6 為0,A7輸入為0 0,則Z7為0;假設為1,即H為1, Z6為1,A7輸入為1 1,則Z7仍為0。經分析:當A、 H接入信源,B~G都為1態時,A7 的輸入或為0 0或為1 1,而Z7都為0。由于H、Z 6是延遲信號(兩信號間存在時間延遲),所以, Z7示波器觀測時將會顯示出一根帶有干擾脈沖的橫亮線。

2.3 測試方法

競爭冒險的測試,主要是對時間延遲 t和干擾脈沖幅度Vp-p的測試 [1,3]。為對干擾脈沖全面認識,本文同時也對干擾脈沖寬度(簡稱干脈寬) tp、干擾脈沖1 0狀態位置(簡稱干脈態) Vp1/Vp0進行了測試。

⑴將A、H端接入100 kHz TTL信號,B~G端接1態。示波器探極Y1、Y2分別接入 H、Z6端,反復調節示波器捕捉測試對象,測出時間延遲 t,即上升沿t≈75ns,下降沿t≈90ns。

⑵保持⑴測試條件和方法,只將探極Y2改接到Z7,測出干擾脈沖幅度V p-p。即上升沿Vp-p≈2.9V,下降沿 Vp-p≈2.6V。

⑶整合H,Z6,Z 7為完整的上升沿、下降沿競爭冒險波形(見圖4) tp,Vp1/ Vp0參數標在圖中。

3 競爭冒險的產生條件

3.1 干擾脈沖產生過程

在上升沿:當先到的H由0→1過渡上升了Vp-p≈1.9V為1態,此時的Z 6也在上升(約上升0.6V)但仍為0態,H、 Z6的異或使Z7由0變1;當后到的 Z6也由0→1過渡上升了Vp-p ≈3.3V為1態,此時H、Z6都為1態,它們的異或使 Z7由1回到0,所以Z7 的橫亮線上瞬間產生出干擾脈沖。

時間延遲t≈75ns,干擾脈沖幅度 Vp-p≈2.9V,干脈寬tp ≈80ns,干脈態Vp1位置在H上升約1.9V處的垂線上,Vp0位置在Z6 上升約3.3V處的垂線上。根據干脈寬tp ,可知另一干脈態Vp0位置。

在下降沿:當先到的H,由1→0過渡下降了Vp-p≈3.8V為0態, 此時的Z6也在下降(約下降1.2V)但仍為1態, H、Z6的異或使Z7 由0變1;當后到的Z6也由1→0過渡下降了 Vp-p≈4.0V為0態,此時H、Z 6都為0態,它們的異或使Z7由1回到0,所以 Z7的橫亮線上瞬間也產生出干擾脈沖。時間延遲 t≈90ns,干擾脈沖幅度Vp-p≈2.6V,干脈寬 tp≈70ns,干脈態Vp1 位置在H下降約3.8V處的垂線上,Vp0 位置在Z6下降約4.0V處的垂線上。也根據干脈寬 tp,可知另一干脈態Vp0 位置。

在上升沿和下降沿,干擾脈沖幅度大小不等。由于線間電容、電感等噪聲的存在和影響,干擾脈沖是個非對稱波形,表現為上升時間長變化緩慢,下降時間短變化陡峭并且存在過沖現象。

3.2 競爭冒險產生條件

由圖4可以看出,競爭冒險的產生受到四個要素的制約,即時間延遲、過渡時間、邏輯關系和延遲信號相位。時間延遲 [1],即信號在傳輸中受路徑、器件等因素影響,輸入端信號間出現的時間差異[2];過渡時間,即脈沖信號狀態不會發生突變,必須經歷一段極短的過渡時間[2];邏輯關系,即邏輯函數式[4];延遲信號相位,即延遲信號狀態間的相位關系,涵蓋延遲信號同相位和延遲信號反相位兩個方面。延遲信號狀態變化相同的則是延遲信號同相位,反之則是反相位。H、Z6 是延遲信號同相位,在異或邏輯產生了干擾脈沖。若H 、Z6是延遲信號反相位,即便異或邏輯也產生不了干擾脈沖。

信號在傳輸中,時間延遲現象隨時存在,而干擾脈沖則時有時無,究其原由是邏輯關系和延遲信號相位要素在起關鍵作用。干擾脈沖是延遲信號在狀態改變的過渡期間產生的,所以,時間延遲和過渡時間要素是競爭冒險的產生原因 [2],邏輯關系和延遲信號相位要素是競爭冒險的產生機制。由原因和機制,構成競爭冒險的產生條件。當電路滿足產生條件時,則一定產生干擾脈沖。

4 競爭冒險的演變過程

4.1 不同路徑、頻率信號的競爭冒險測試

將圖1電路由7級擴大到11級(電路圖略),可通過更長路徑和不同頻率信號來探究各奇數門競爭冒險的產生以及演變情況,見表的測試參數。

表1記錄了11級異或門電路在10 Hz~1 MHz TTL信號時,各奇數門信號在上升沿(£)和下降沿(£)的時間延遲t、干擾脈沖幅度Vp-p ,以及干脈寬tp和干脈態V p1/Vp0的測試參數。對于1MHz以上信號的競爭冒險,擬作另文研究。表1中的陰影部分是“2 競爭冒險的測試”中的測試參數。

4.2 競爭冒險與信號頻率、傳輸路徑間的關系

各奇數門在10 Hz~1 MHz信號時的輸出幾乎相同,表明競爭冒險的產生與信號頻率無關。隨著奇數門的增加t也在增大,表明競爭冒險的產生與信號傳輸路徑有關,即與時間延遲有關。

4.3 競爭冒險各參數間的關系

記錄表中A1在上升沿的各參數全部為0,而下降沿除了t≈0其他參數出現了較小數值。A3的上升沿和下降沿,各參數都在迅速增大。A5以及A7 ~A11的上升沿和下降沿,有的參數趨于穩定,有的參數繼續增大。各參數的演變說明如下。

⑴競爭冒險的演變,經歷萌生期、發展期和成熟期。A1是萌生期,Vp-p≈0.06V,干擾脈沖雛形開始生成;A3是發展期,Vp-p≈0.7~0.9V小于開門電平;A5~A11是成熟期,Vp-p≈2.7~3.2V大于開門電平。表明萌生期、發展期是安全期,干擾脈沖不具危害,而成熟期是危險期,干擾脈沖存在極大危害性。

⑵關于t和Vp-p:在萌生期t≈0,Vp-p≠0;在發展期t、Vp-p都在迅速壯大;在成熟期t、Vp-p繼續增大。表明t大則Vp-p大,t、Vp-p之間存在一定的比例關系。

(3) 關于t和tp:除了萌生期t≈0外,在發展期和成熟期,t的上升沿/下降沿變化范圍45~100ns/65~115ns,tp的上升沿/下降沿變化范圍50~105ns /50~90ns,表明t與tp大致相等。

(4) 關于Vp1/Vp0:上升沿1.6V/3.0V~2.1V/3.3V,下降沿1.6V/1.6V~3.8V/4.1V,表明不同期的干擾脈沖幅度大小不等、狀態位置不同。

5 競爭冒險的抑制措施設置

揭秘競爭冒險的成因,旨在競爭冒險的研究和應用。由記錄表知道,A3的Vp-p小于開門電平,A5的Vp-p大于開門電平,所以,在發展期和成熟期之間設置競爭冒險抑制措施較為適宜。因此,競爭冒險抑制措施。比如封鎖脈沖、濾波電容、修改邏輯等方法都可抑制或消總有兩面性,競爭冒險也不例外,已有文獻報道,將競爭冒險用于集成電路設計取得了滿意效果[6]。

6 結語

競爭冒險的產生與信號頻率無關;時間延遲t大則干擾脈沖幅度Vp-p大,時間延遲t與干擾脈沖寬度tp大致相等,不同期的干擾脈沖幅度大小不等,狀態位置不同;時間延遲、過渡時間、邏輯關系和延遲信號相位,構成競爭冒險的產生條件。當電路滿足產生條件時,則一定產生干擾脈沖。競爭冒險的演變過程,經歷萌生期、發展期和成熟期。萌生期、發展期是安全期,干擾脈沖不具危害,而成熟期是危險期,干擾脈沖存在極大危害性。競爭冒險抑制措施,建議電路從第四級門開始設置。為對干擾脈沖的全面認識,本文同時也給出了不同時期干擾脈沖的寬度tp、狀態位置Vp1/Vp0以及變化范圍。

電子發燒友App

電子發燒友App

評論