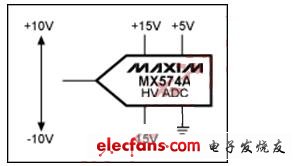

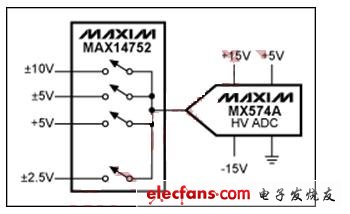

模/數轉換器(ADC)電路設計中,特別是當系統設計人員需要處理各種擺幅的電壓信號時,很容易產生的一個誤區是縮小輸入信號范圍,以適應ADC的滿量程范圍,這將大大降低信噪比(SNR)。綜合來看,低壓

2013-09-22 12:12:56 3874

3874

由于 SAR ADC 的功耗隨著每一代新器件的推出而不斷降低,放大器成了功耗敏感型應用的制約因素。那么我們如何才能進一步降低功耗?在尋找可能的解決方案之前,讓我們先考慮一下 ADC 功耗降低的原因。

2016-08-12 16:04:09 1285

1285

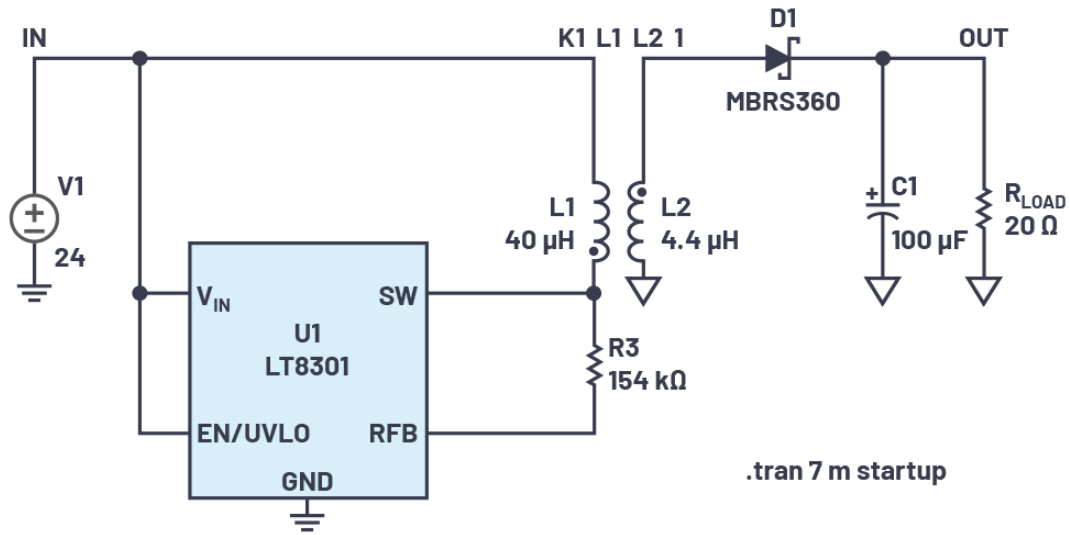

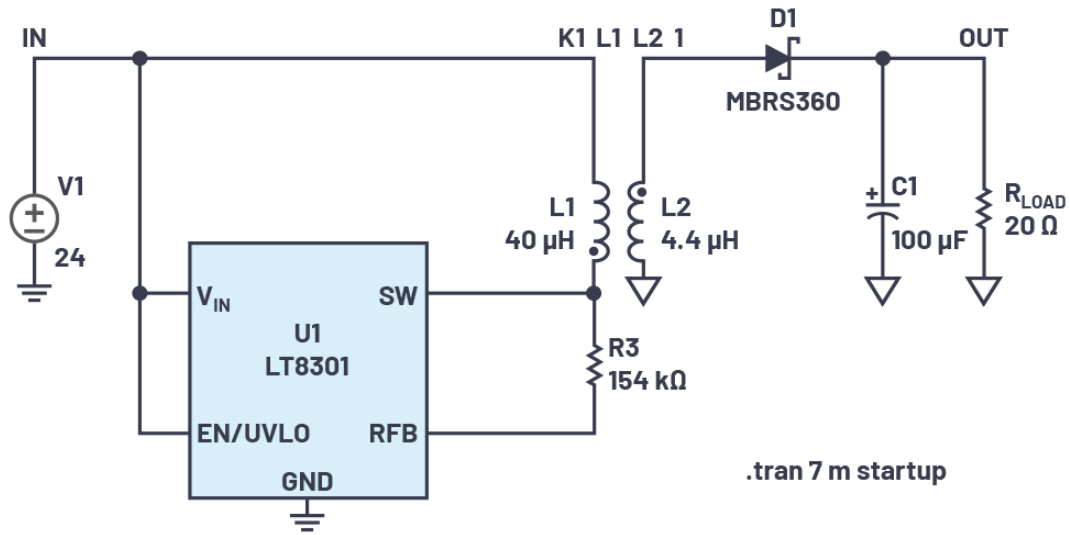

開關電源(DC-DC轉換器)真的會降低模數轉換器的性能嗎?會?不會?工程師一般認為開關電源會降低ADC的性能

2017-10-31 09:36:09 5730

5730 ? 什么是信噪比呢?信噪比即音源產生最大不失真聲音信號強度與同時發出的噪音強度之間的比率,通常以“SNR”或“S/N”表示,是衡量音箱、耳機等發音設備的一個重要參數。對于各類產品來說這是一個很關鍵

2021-12-23 14:05:02 6896

6896

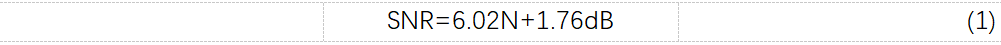

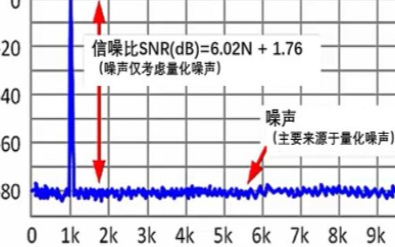

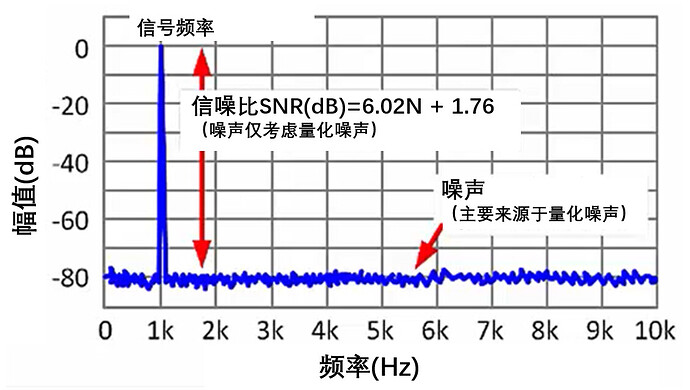

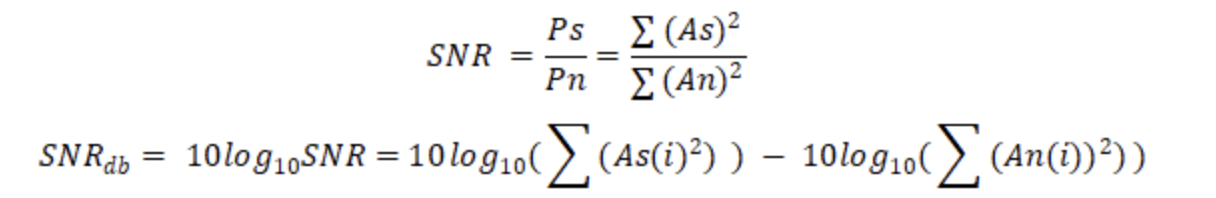

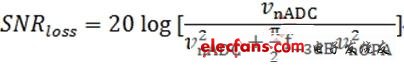

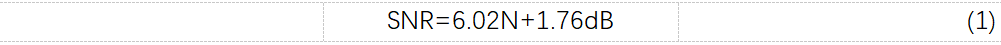

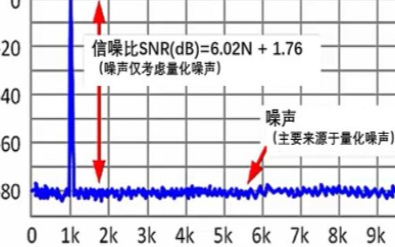

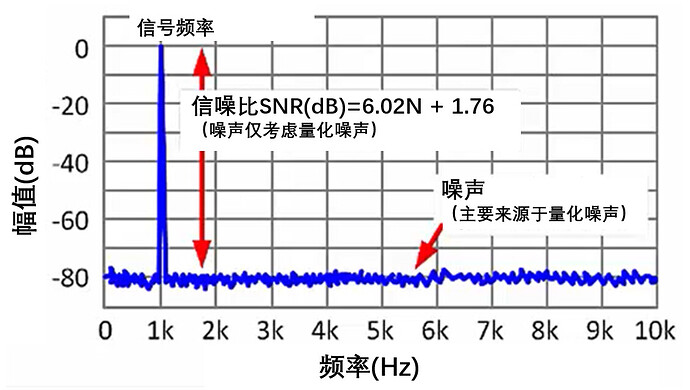

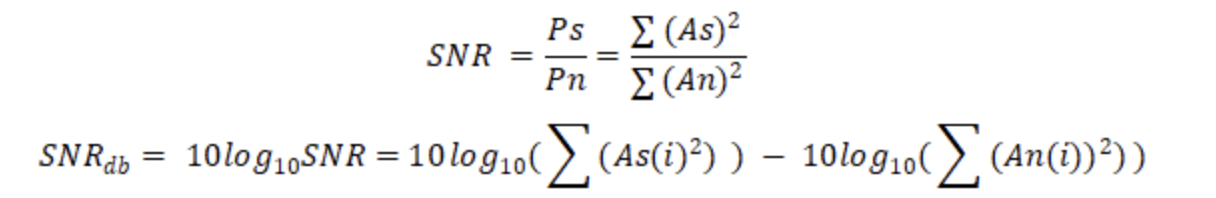

其中N是ADC的位數,比如對于一個10bit的ADC,N=10,當ADC采集一個滿量程的正弦波時,那么信噪比SNR=6.02*10+1.76=61.96dB,那么這個公式是怎么來的呢?

2022-09-07 14:07:44 7369

7369 做過數據采集或者模擬電路的同學很可能知道下面這個關于ADC信噪比的著名公式。

2023-04-18 12:06:13 8209

8209

做過數據采集或者模擬電路的同學很可能知道下面這個關于ADC信噪比的著名公式。

2023-06-28 09:09:28 373

373

▼關注公眾號:工程師看海▼ ??大家好,我是工程師看海,原創文章歡迎 點贊分享 ! 做過數據采集或者模擬電路的同學很可能知道下面這個關于ADC信噪比的著名公式: 其中N是ADC的位數,比如

2023-10-30 11:45:38 291

291

時鐘隔離是另一項重要任務。如果使用1 MHz采樣速率的20位高性能ADC,例如LTC2378-20,可以實現104 dB的信噪比(SNR)。

2021-09-03 14:23:14 4682

4682

ADC3564器件是一款低噪聲、超低功耗、14位、125 MSPS、高速ADC。該器件專為低功耗而設計,可提供 –156 dBFS/Hz 的噪聲頻譜密度以及出色的線性度和動態范圍。ADC3564提供

2022-09-29 14:31:41

實際分辨率受器件自身誤差和電路噪聲的影響很大。ADC信噪比要怎么分析?高速高分辨率ADC電路要怎么實現?

2021-04-14 06:16:30

192.2THz 的波長在 MpI-s 點的光功率下降了近 8dB,信噪比降低了 5 個值,而其它中心頻率的波幾乎沒有大的變化,這主要因為放大器具有自動增益均衡,當 16 路信號中的某些信號失去

2018-03-12 09:57:05

請問一下LABVIEW有測試信噪比的函數嗎?

2013-05-29 09:16:36

正如前面所討論的,在回歸中定義了損失函數或目標函數,其目的是找到使損失最小化的系數。本節將介紹如何在 TensorFlow 中定義損失函數,并根據問題選擇合適的損失函數。聲明一個損失函數需要將系數

2020-07-28 14:38:42

Δ-Σ轉換器信噪比如何不同?Δ-Σ 轉換器信噪比是如何計算的?

2021-04-08 06:10:01

請問現在純后級大功率功放的輸出信噪比最高可以達到什么兩級?

2016-11-29 21:40:00

的。對于某個給定的 ADC,在零標度測量的動態范圍 (DR) 之所以通常比在全標度或接近全標度測量的信噪比 (SNR) 高出幾個 dB,原因即在于此。在 ADC 的 SNR 有可能超過 140dB

2019-07-25 07:15:15

【作者】:蔡夢;張科峰;鄒雪城;吳蘭春;【來源】:《華中科技大學學報(自然科學版)》2010年03期【摘要】:為了解決傳統信噪比估計算法在多徑信道下性能顯著降低且復雜度較高的問題,提出一種基于空子

2010-04-23 11:51:46

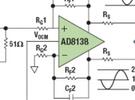

作者: Xavier Ramus 由于 SAR ADC 的功耗隨著每一代新器件的推出而不斷降低,放大器成了功耗敏感型應用的制約因素。那么我們如何才能進一步降低功耗?在尋找可能的解決方案之前,讓我們

2018-09-21 15:16:44

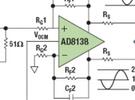

[td][/td] 如圖所示,如何設計AD8221交流耦合電路能:

1、降低噪聲,提高信噪比(SNR);

2、提高儀表運放輸入阻抗;

3、提高共模抑制比(CMRR)。

2023-11-17 09:47:43

影響ADC信噪比因素有哪些?如何設計高速高分辨率ADC電路?基于AD6644AST一65的高速高分辨率ADC電路設計實例

2021-04-23 06:01:56

首先,在設計ADC采樣時會考慮到,標稱是16位的ADC,扣除一些誤差實際有效的位數為14位,確定好參數。后面在調試時如何驗證該電路設計出來確實有14位的精度,舉個栗子:我用恒壓源1.0V做被采樣電壓

2019-01-09 12:07:15

請教一下。對于450M帶寬40兆,要保持良好的信噪比,應該選擇什么樣的AD。

雖然ADC手冊給出了全通帶寬,但是手冊中比如說采樣率120M的一款AD,

全通帶寬900M,但是最多給輸入220M的測試

2023-12-06 08:19:53

開關電源會降低ADC的性能嗎?

2019-05-27 11:20:59

問題。圖3:設計不佳的ADC和/或布局布線、接地、去耦不當的接地輸入端直方圖 提高ADC分辨率并降低噪聲?折合到輸入端噪聲的影響可以通過數字均值方法降低。假設一個16位ADC具有15位無噪聲 分辨率

2019-02-26 07:48:19

,NTP8835的信噪比性能可以be降低至90 dB,PWM開關頻率從384kHz擴展至768kHz。如bluesky6test.測試前根據電路參數設置,采樣頻率和電壓電流分別有兩種設置。這樣隨著時間的變化,測量

2022-01-06 09:26:34

求助LabVIEW濾波器信噪比的算法?

2014-05-14 10:49:05

,此時LNA的輸出端的信噪比仍然是比輸入端的信噪比要小的。綜合上述兩種情況呢,我得出以下結論,不僅LNA如此,整個射頻接收機可能都表現出相同的性狀,信噪比是降低的。但是如果接收機的輸出端的信噪比比輸入端的信噪比還要低,這樣貌似有點失去了當初做接收機的意義了?煩請各位牛人指點一二,不勝感激。

2023-04-25 11:08:56

請教幾個常見的濾波器電路圖;還想了解一下如何降低基準輸出噪聲;我查了一些資料曉得獲得 ADC 的最佳 SNR 性能并不僅僅是給 ADC 輸入提供低噪聲信號的問題。提供一個低噪聲基準電壓是同等

2021-03-05 07:35:24

電源 (SMPS)是一種經濟實惠且高效的電源解決方案。此類解決方案不會使 12 位 ADS540x 系列的模數轉換器 (ADC)出現性能降級,且不會浪費過多功率。測試報告顯示了兩個電源之間的信噪比

2022-09-26 07:30:54

回路損失是由于電纜結構及相關連接部件的阻抗變化引起的信號衰減,這些變化致使信號反射回信源,在低頻時,回路損失的影響較小,但在頻率高于50MHZ時,就會產生很大的影響,對于高清視頻系統,頻率會達到

2019-06-11 09:55:15

為什么經過ADC采樣后,我用matlab仿真后,底噪在-100左右,而ADC芯片資料上都在-120左右,請問如何降低ADC的底噪?analogchina-admin

2018-08-09 08:40:04

為什么經過ADC采樣后,我用matlab仿真后,底噪在-100左右,而ADC芯片資料上都在-120左右,請問如何降低ADC的底噪?

2023-12-12 06:56:44

如圖所示,如何設計AD8221交流耦合電路能:1、降低噪聲,提高信噪比(SNR);2、提高儀表運放輸入阻抗;3、提高共模抑制比(CMRR)。

2018-08-06 06:55:10

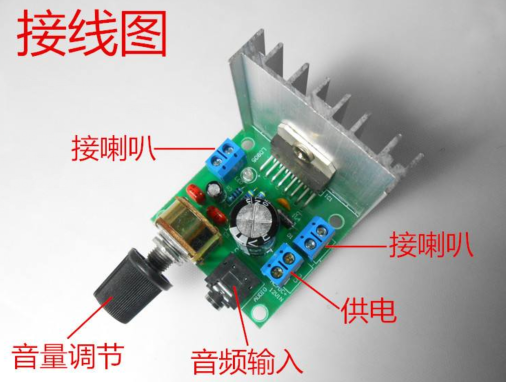

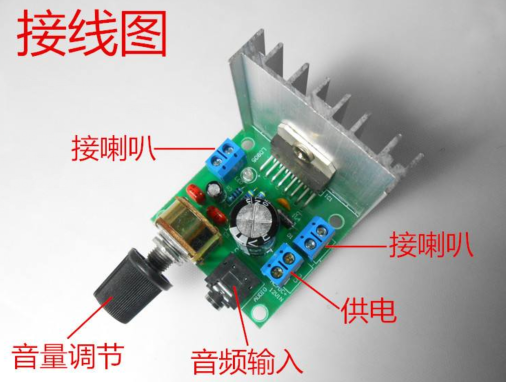

`各位大佬好,請問哪位大佬可以賜教,如何測量放大電路的信噪比,使用什么設備,什么方法?電路如圖所示。`

2018-09-11 09:27:11

本文首先從理論**析了影響ADC信噪比的因素;然后從電路設計和器件選擇兩方面出發,設計了高速高分辨率ADC電路。

2021-04-12 07:11:31

電源 (SMPS)是一種經濟實惠且高效的電源解決方案。此類解決方案不會使 12 位 ADS540x 系列的模數轉換器 (ADC)出現性能降級,且不會浪費過多功率。測試報告顯示了兩個電源之間的信噪比

2018-09-29 09:51:05

介紹了LEO 衛星擴頻通信中的抑制強窄帶干擾所帶來的信噪比損失,提出在在抗干擾處理后用全數字AGC 來穩定電平。在AGC 保護下,接收機的信噪比損失在1dB 范圍內。

2009-09-17 10:40:28 16

16 本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。

2009-11-27 11:24:07 15

15 電子管放大器信噪比的提高:聲頻放大器由于元器件的質量和外部影響,會出現噪聲(noise),降低信噪比。聲頻放大器的噪聲可分:① 規則噪聲,如交流聲;② 連續的不規則噪聲,如

2009-11-29 17:00:39 57

57 LTD2284是一款32位的超高精度的Δ-Σ型ADC。輸入端采用MUX+PGA配置,可兼容兩路差分或三路單端信號,4階Δ-Σ調制器配合數字濾波器使信噪比達到130dB,最大采樣率達到4kSPS,可配

2023-12-13 16:21:28

高速ADC供電指南

為使高速模數轉換器發揮最高性能,必須為其提供干凈的直流電源。高噪聲電源會導致信噪比(SNR)下降和/或ADC輸出中出現不良的雜散成分。本文將介紹有關ADC

2011-01-01 12:18:09 94

94 摘要:首先從理論上分析了影響ADC信噪比的因素,然后以此為依據,從電路設計和器件選擇兩方出發,采用模/數轉換器AD6644AST-65進行高速高分辨率ADC電路設計,并給

2006-03-13 14:15:10 3019

3019

“信噪比”是電子技術中經常用到的一個詞組,知道它的確切含義有一定意義。為此,這里將

2006-04-16 23:41:43 2987

2987 什么是音箱信噪比

2009-12-28 10:50:02 1998

1998 網絡攝像機的信噪比 &

2010-01-07 09:55:04 1478

1478 數字語音室的信噪比/通道串音衰減 數字語音室的信噪比 信噪比,又稱為訊噪比,信號的有用成份與雜音

2010-01-07 11:35:05 592

592 什么是聲卡/信噪比?

聲卡 (Sound Card):顧名思義,就是發聲的卡片,它象人喉嚨中的聲帶一樣,有了它就能發出聲音,就能交流

2010-02-05 11:01:15 1731

1731 什么是路間串擾/幅頻特性/隨機信噪比

路間串擾 路間串擾:多路信號在同一設備中,由于空間的輻射與電源的波動

2010-03-26 11:49:40 1163

1163 影碟機的信噪比 信噪比又稱為訊噪比,英文全稱是(the Signal to Noise ratio),通常以S/N表示。無論對于任何

2010-01-04 14:46:10 1071

1071 家庭影院套裝的信噪比 信噪比是指音響系統對音源的重放聲與整個系統產生的新的噪聲的比值,其噪

2010-01-04 15:52:29 854

854 車載功放的信噪比 信噪比是指功放輸出的信號電平(有用信號)與各種噪聲電平(無用信號)之比,也就是回

2010-01-04 11:05:44 2748

2748 工程師一般認為開關電源會降低ADC的性能,因此通常愿意選用低壓差(LDO)線性穩

2010-10-13 11:43:56 836

836 模擬轉換器性能不只依賴分辨率規格 大量的模數轉換器(ADC)使人們難以選擇最適合某種特定應用的ADC器件。工程師們選擇ADC時,通常只注重位數、信噪比(SNR)、諧波性能,但是其它規格

2012-01-09 17:40:03 93

93 在QPSK調制方式下,分別研究推導了基于輔助數據的極大似然比信噪比估計算法研究、基于矩的信噪比估計算法研究以及基于高階累積量的信噪比估計算法。通過仿真比較了信噪比估計算

2013-04-27 16:35:14 26

26 信噪比與噪聲的詳細解析。

2016-05-17 11:09:40 12

12 電子專業單片機相關知識學習教材資料——什么是信噪比

2016-08-22 17:24:26 0

0 信噪比說明

2017-01-04 13:47:47 0

0 一種低信噪比損失SVD濾波部分頻帶干擾抑制算法_劉松

2017-01-07 16:52:06 1

1 EE Times 高信噪比的好處

2017-01-26 11:36:55 11

11 SNRboost 是一種噪聲成型技術,該技術能夠改變量化噪聲的頻譜。集成 SNRboost 的 ADC 能夠把在一定帶寬內的量化噪聲推出帶外,從而提高 ADC 的 SNR. 本文詳細介紹了SNRboost ADC 的工作原理,以及SNRboost ADC 引入問題的分析及解決辦法。

2017-05-31 15:09:31 13

13 ADC位數是根據傳輸方式和噪聲來計算的。如,64QAM/7/8碼率在視頻解碼正常的最低信噪比為28dB(某種衰落信道下);OFDM在輕微削波時的峰均比假設為11dB,所以ADC的最大信噪比至少

2017-12-04 15:50:04 48672

48672

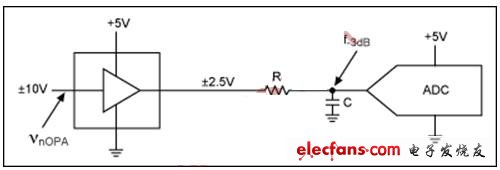

如果信號源具有低頻分量,可以設計濾波器,使放大器能夠容許較大的輸入噪聲(較高的輸入噪聲通常與較低的功耗和成本有關)。如果ADC限制了系統的帶寬,放大器需要具有足夠低的輸入參考噪聲,以便把SNR損失控制在可接受的范圍內。

2018-03-09 14:16:08 5089

5089

本文開始介紹了電壓損失的概念,其次詳細的闡述了電纜電壓損失的計算方法。最后詳細介紹了電纜電壓損失表。

2018-04-03 11:03:44 30771

30771 時鐘分配芯片提供了一個真實的時鐘解決方案,以滿足對高速ADC的嚴格要求。這份報告強調了與時鐘源相關的限制性試劑影響ADC的信噪比性能。顯示了與CDC7005同步的ADS5500ADC的性能,并與理想的基線性能進行比較。

2018-05-18 11:07:29 4

4 在使用模數轉換器(ADC)進行設計時,人們很容易錯誤地認為,縮小輸入信號以滿足 ADC 的滿量程范圍,會造成信噪比 (SNR)的明顯降低。需要處理寬電壓擺幅的系統設計人員對此更是尤為關注。此外

2020-11-19 15:05:00 18

18 在此我們簡要總結一下ADC的各種指標如何理解,以及從硬件到軟件都有哪些可以采用的手段來提高ADC的轉換精度。1.ADC指標除了分辨率,速度,輸入范圍這些基本指標外,衡量一個ADC好壞通常會用到以下這些指標:失調誤差,增益誤差,微分非線性,積分非線性,信噪比,信納比,有效位數,總諧波失真

2020-12-24 13:55:34 3123

3123 MT-200:降低ADC時鐘接口抖動

2021-03-21 01:18:30 7

7 LTC2369-18:18位、1.6Msps、偽差分單極SAR ADC,信噪比為96.5dB數據表

2021-05-17 14:55:20 11

11 LTC2364-16:16位、250ksps、偽差分單極SAR ADC,信噪比為94.7dB數據表

2021-05-24 17:01:08 1

1 一般來說,我們可以提高ADC采樣位數來提高ADC的信噪比,但是往往意味著ADC的成本可能也會更高。有沒有不提高位數,同樣優化信噪比的方法呢?有的,那就是過采樣。

2022-03-07 08:56:00 6081

6081

OSNR(光信噪比)的原理介紹.pdf

2022-03-08 11:40:10 3

3 最先進的每秒 112 吉比特 (Gbps) 長距離 (LR) SerDes PHY 的設計要求將模數轉換器 (ADC) 的位數降至最低,以實現整個系統占用最小的面積和消耗最小的功率。為此,利用

2022-07-28 08:03:10 1084

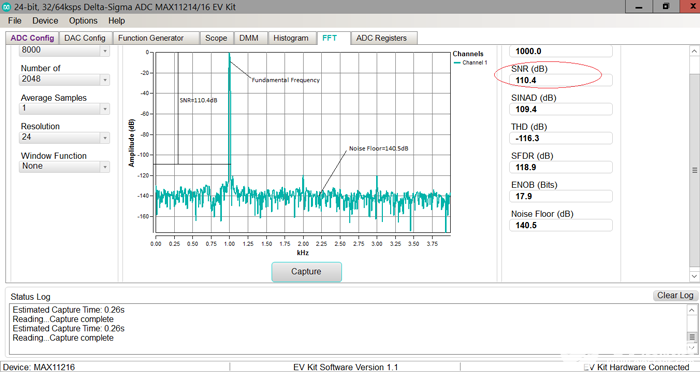

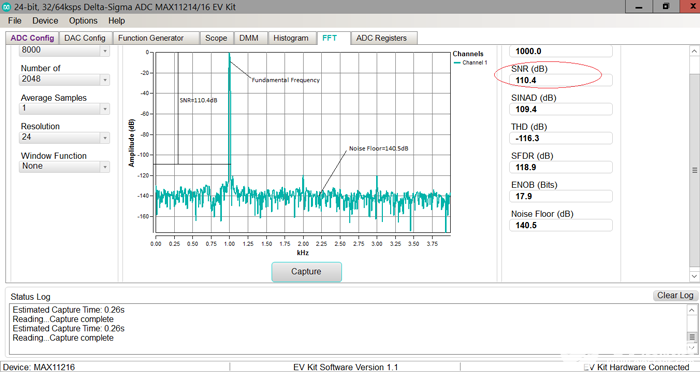

1084 模數轉換器(ADC)的動態性能由有效位數(ENOB)決定。在本應用筆記中,我們研究了ENOB與ADC的其他動態特性的關系,如信噪比(SNR)、信噪比和失真比(SINAD)以及總諧波失真(THD)。我們還將MAX11216 24位高性能Δ-Σ型ADC的理論計算ENOB與實驗室測量值進行了比較。

2022-12-21 15:32:54 12375

12375

對標AD7606的高精度8通道同步ADC CM2248,信噪比達92dB,可以滿足電池分容化成、ATE和電力線監控及電源逆變的性能要求

2022-12-30 14:19:32 1181

1181 使用模數轉換器(ADC)進行設計時,一個典型的誤解是,縮小輸入信號以驅動ADC的滿量程范圍會顯著降低信噪比(SNR)。對于使用寬電壓擺幅的系統設計人員來說,這一點尤其值得關注。使問題更加復雜

2023-02-28 14:20:16 552

552

一般來說,我們可以提高ADC采樣位數來提高ADC的信噪比,但是往往意味著ADC的成本可能也會更高。有沒有不提高位數,同樣優化信噪比的方法呢?有的,那就是過采樣。

2023-06-02 10:44:13 788

788

信噪比是探測器中信號功率與噪聲功率的比值。光學測量中通常將信號比(SNR,S/N比)作為一個特性參數。

2023-06-11 11:46:46 773

773

CDMA系統中的功率控制是一項重要的優化技術,通過對發射功率進行動態調整,使各用戶達到相對均衡的接收信噪比。合理的功率控制可以提高系統容量、降低干擾和提升系統性能。

2023-06-20 16:17:23 1036

1036 調試Serdes的時候經常會查看信號信噪比SNR這個指標,那這個信噪比是怎么計算的呢?

2023-09-08 14:43:47 1776

1776

入轉換后的數字信號中,導致信噪比降低,降低系統的可靠性。那么,ADC諧波產生的原因是什么呢? ADC中諧波的來源 1.非線性量化誤差 ADC將模擬信號進行量化,即將連續變化的模擬信號離散成一個一個的數字代碼。量化過程中,ADC的特性曲線通常是

2023-09-12 10:51:07 1345

1345 使用軟件如何去除一些內部噪聲,降低對ADC結果的影響? 標題:使用軟件去除內部噪聲,降低對ADC結果的影響 引言: 在數字信號處理中,噪聲是一個普遍存在的問題。當我們使用模擬到數字轉換器(ADC

2023-11-09 15:38:37 304

304 信噪比是用于衡量信號質量的一個重要指標。它表示信號與噪聲的相對強度或功率之間的比值。信噪比越高,表示信號相對于噪聲更強,質量更好。

2024-02-21 17:06:32 175

175

電子發燒友App

電子發燒友App

評論