當運算放大器的輸入電壓超過額定輸入電壓范圍,或者在極端情況下,超過放大器的電源電壓時,放大器可能發生故障甚至受損。本文討論過壓狀況的一些常見原因和影響,為無保護的放大器增加過壓保護是如何的麻煩,以及集成過壓保護的新型放大器如何能為設計工程師提供緊湊、魯棒、透明、高性價比的解決方案。

所有電子器件的可耐受電壓都有一個上限,超過上限就會產生影響,輕則導致工作暫時中斷或系統閂鎖,重則造成永久性損害。特定器件能夠耐受的過壓量取決于多個因素,包括是否安裝或意外接觸器件、過壓事件的幅度和持續時間、器件的魯棒性等。

精密放大器常常是傳感器測量信號鏈中的第一個器件,因而最容易受到過壓故障的影響。選擇精密放大器時,系統設計師必須了解放大器的 共模輸入范圍 。在數據手冊中,共模輸入范圍可能是用輸入電壓范圍 (IVR), 測試條件下的 共模抑制比 (CMRR),或以上二者來規定。.

過壓狀況的實際原因

放大器需要兩種保護:一是過壓保護 用以防止電源時序控制、休眠模式切換和電壓尖峰引起的故障;二是 ESD 靜電放電)保護,用以防止靜電放電 (甚至搬運過程中也可能出現靜電放電),引起的故障。 安裝后, 器件可能會受系統電源時序控制,導致重復性過壓應力。系統設計師必須想方設法使故障電流避開敏感的器件,或者限制故障電流,使其不致于損壞器件。

在有多個電源電壓的復雜分布式電源架構 (DPA)系統中, 電源時序控制可以使系統電路各部分的電源在不同的時間開啟和關閉。時序控制不當可能會導致某個器件的某個引腳發生過壓或閂鎖狀況。

隨著人們越來越關注能源效率,許多系統要求實現復雜的休眠 和待機 模式。這意味著,在系統的某些部分已關斷的同時,其它部分仍然可能處于上電和活動狀態。與電源時序控制一樣,這些情況可能會導致無法預測的過壓事件,但主要是在輸入引腳上。

許多類型的傳感器會產生意想不到的、與它們要測量的物理現象無關的輸出尖峰,這類過壓狀況一般僅影響輸入引腳。

靜電放電是一種廣為人知的過壓事件,常常發生在安裝器件之前。它造成的損害非常廣泛,以至于業界主要規范,如JESD22-A114D, determine how to test and specify the semiconductor’s 等,不得不明確如何測試和規定半導體耐受各類ESD事件的能力。幾乎所有半導體產品都包含某種形式的集成保護器件。應用筆記AN-397“標準線性集成電路的電誘發損壞:最常見起因和防止再發生的相關處理,”是一篇很好的參考文獻,詳細討論了這一問題。出現高能脈沖時,ESD單元應進入低阻抗狀態。這不會限制輸入電流,但能提供到供電軌的低阻抗路徑。

一個簡單的案例研究:電源時序控制

隨著混合信號電路變得無處不在,單一PCB上的多電源需求也變得非常普遍。關于新設計需要考慮的一些微妙問題,特別是需要許多不相關的電源時,請參閱應用筆記AN-932 “電源時序控制,”.

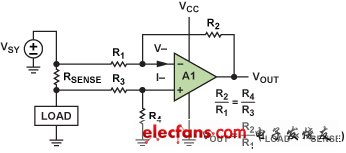

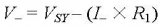

精密放大器可能會成為這種狀況的受害者。圖1顯示了一個配置成差分放大器的運算放大器。放大器通過RSENSE 檢測電流,并提供與相應壓降成比例的輸出。必須采取措施,確保由R3和R4構成的分壓器將輸入偏置在額定IVR范圍內的某處。如果放大器的電源電壓不是從VSY, 獲得,并且VCC在VSY,之后出現,則A1反相輸入端的電壓為:

V– = VSY – (I– × R1) (1)

其中I–由無電源時A1的輸入阻抗決定。如果放大器不包含過壓處理設計,則最有可能的電流路徑是通過ESD二極管、箝位二極管或寄生二極管流向電源或地。如果此電壓超出IVR范圍,或者電流超過數據手冊規定的額定最大值,器件可能會受損。

ADA4091 和 ADA4096, 等過壓保護放大器所用的ESD結構不是二極管,而是DIAC 器件(雙向“交流二極管”),這使得此類放大器即使沒有電源也能承受過壓狀況。

?

圖1. 差分放大器高端電流傳感器。如果VSY 先于VCC,上電,放大器的輸入電壓或電流可能會超過數據手冊規定的最大值

運算放大器中的故障狀況

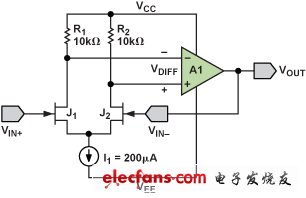

圖2顯示了一個N溝道JFET輸入級 (J1, J2, R1, and R2), 后接一個第二增益級和輸出緩沖器(A1)。當開環放大器在其額定IVR范圍內時,差分輸入信號 (VIN+ – VIN–)與VDIFF.180度異相。連接為單位增益緩沖器時(如圖所示),如果VIN+的共模電壓超過放大器的IVRJ1’的柵極-漏極進入未夾斷狀態并傳導整個200 μA級電流。只要J1’的柵極-漏極電壓仍然反向偏置VIN+的進一步增加就不會導致 VDIFF變化 (VOUT仍然處于正供電軌). 然而,一旦J1’的柵極-漏極變為正偏,VIN+的進一步增加就會提高A1反相輸入端的電壓,導致輸入信號與 VDIFF之間發生不需要的反相.

?

圖2. N溝道JFET輸入運算放大器結構示意圖

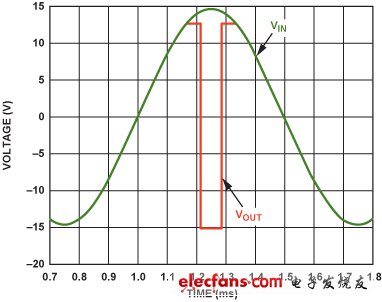

圖3顯示了A1輸出端反相的一個示例。與雙極性輸入放大器不同,JFET放大器的輸入未箝位,因而易發生反相。CMOS放大器的柵極與漏極電隔離,一般不會發生反相。如果確實會發生反相,運算放大器制造商一般會在數據手冊中說明。下列條件下可能發生反相:放大器輸入端不是CMOS,最大差分輸入為VSY, 數據手冊未聲明不會發生反相。雖然反相本身不是破壞性的,但它能導致正反饋,進而使伺服環路不穩定.

?

圖3. 當VIN超過額定IVR時,輸入反相導致放大器輸出負值

系統設計師還必須關注放大器輸入超出電源范圍時會發生什么。這種故障狀況通常發生在電源時序控制導致一個源信號先于放大器電源激活時,或者在開啟、關閉或工作中電源出現尖峰時。對于大多數放大器,這種狀況是破壞性的,尤其是如果過壓大于二極管壓降。

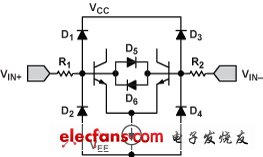

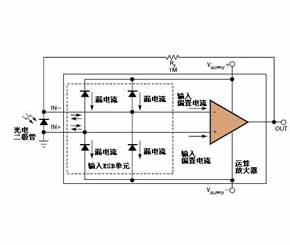

圖4顯示了一個帶ESD保護二極管和箝位二極管的典型雙極性輸入級。在緩沖器配置中,當VIN+ 超過任一電源軌時,ESD和箝位二極管就會正偏。這些二極管的源極阻抗非常低,源極支持多少電流,二極管就能傳導多少電流。精密放大器AD8622提供少許差分保護,輸入端串聯500 Ω電阻,施加差分電壓時,該電阻可限制輸入電流,但它只能在輸入電流不超過額定最大值時提供保護。如果最大輸入電流為5 mA,則允許的最大差分電壓為5 V。注意,這些電阻并不與ESD二極管串聯,因而無法限制流向電源軌的電流(例如在過壓期間)。

?

圖4. 帶ESD和差分保護二極管的雙極性輸入級

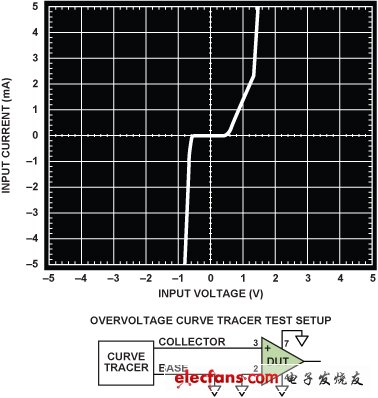

圖5顯示一個無保護雙極性運算放大器在同時施加差分輸入和過壓情況下的輸入電流與電壓的關系。一旦施加的電壓超過二極管壓降,電流就可能損害、降低運算放大器的性能,甚至破壞運算放大器。

?

圖5. 差分輸入電壓超過二極管壓降時的運算放大器輸入電流

外部輸入過壓保護

從半導體運算放大器問世之初,IC設計師就不得不權衡芯片架構與應對其脆弱性所需的外部電路之間的關系。故障保護一直是最棘手的問題例如,, 請參閱“運算放大器輸出反相和輸入過壓保護” 和MT-069, “儀表放大器輸入過壓保護”).

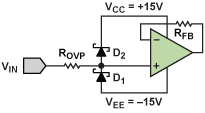

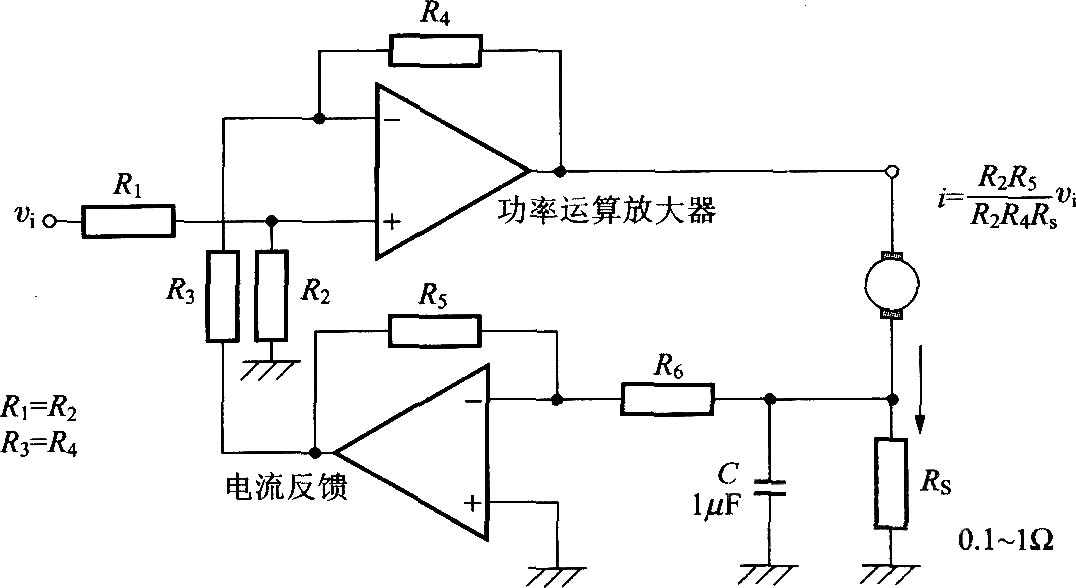

系統設計師之所以需要精密運算放大器,是因為它有兩個重要特性:低失調電壓(VOS)和高共模抑制比(CMRR),這兩個特性能夠簡化校準并使動態誤差最小。為在存在電氣過應力(EOS)的情況下保持這些特性,雙極性運算放大器經常內置箝位二極管,并將小限流電阻與其輸入端串聯,但這些措施無法應對輸入電壓超過供電軌時引起的故障狀況。為了增加保護,系統設計師可以采用圖6所示的電路。

?

圖6. 利用限流電阻和兩個肖特基二極管提供外部保護的精密運算放大器。RFB與ROVP相等,從而平衡輸入偏置電流引起的失調

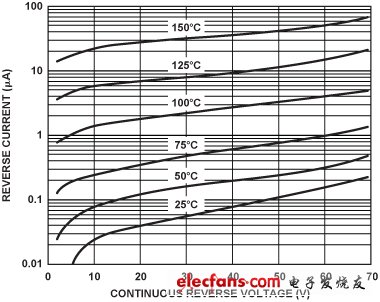

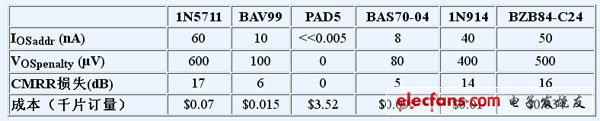

如果VIN處的信號源先行上電,ROVP將限制流入運算放大器的電流。肖特基二極管的正向電壓比典型的小信號二極管低200 mV,因此所有過壓電流都會通過外部二極管D1和D2.分流。然而,這些二極管可能會降低運算放大器的性能。例如,可以利用1N5711的反向漏電流曲線(見圖7)來確定特定過壓保護電阻造成的CMRR損失。1N5711在0 V時的反向漏電流為0 nA,在30 V時為60 nA。對于0 V共模電壓, D1 和 D2 引起的額外IOS取決于其漏電流的匹配程度。當V被拉至+15 V時,D1將反向偏置30 V,D2將偏置0 V。因此,額外的60 nA電流流入ROVP.當輸入被拉至–15 V時,D1和D2 的電氣位置交換,60 nA電流流出OVP. 在任意共模電壓下,保護二極管引起的額外 IOS等于:

IOSaddr = ID1 – ID2 (2)

?

圖7. 1N5711反向電流與連續反向電壓之間的關系

由公式2可計算出極端共模電壓下的VOS損失:

VOSpenalty = IOSaddr × ROVP (3)

使用1N5711在30 V時的漏電流60 nA以及5 kΩ保護電阻,兩個極端共模電壓下的VOS將增加300 μV,導致整個輸入電壓范圍內的額外 ?VOS 為600 μV。根據數據手冊,一個具有110 dB CMRR的運算放大器將損失17 dB CMRR。插入反饋電阻來均衡源阻抗只能在共模電壓為0 V時有幫助,但無法防止整個共模范圍內產生額外的IOS 表1顯示了保護精密放大器常用的一些二極管的計算結果。對于CMRR損失計算,假設使用5 kΩ保護電阻。所有成本都是來自www.mouser.com的最新美元報價(2011)。

表1. 常用保護二極管及其對110 dB CMRR精密運算放大器的影響

?

圖6所示的方法可能還有一個缺點,那就是保護二極管會將過壓電流分流到電源中。例如,如果正電源無法吸收大量電流,過壓電流就可能迫使正電源電壓提高。

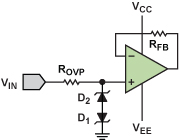

防止這一現象的一種方法是在正輸入與地之間使用背靠背齊納二極管,如圖8所示。超過D1或 D2的齊納電壓時,二極管將過壓電流分流到地,從而保護電源。這種配置能夠防止過壓期間的電荷泵效應,但齊納二極管的漏電流和電容高于小信號二極管。此外,齊納二極管的漏電流曲線具有軟拐點(soft-knee)特征。在放大器的共模范圍內,這會帶來額外的CMRR損失,如前所述。例如,BZB84-C24是一個背靠背齊納二極管對,工作電壓范圍為22.8 V至25.6 V,反向電流額定值為50 nA(最大值,16.8 V時),但制造商并未說明接近齊納電壓時的漏電流是多少。此外,為實現更陡的擊穿特性,齊納二極管一般采用比小信號二極管摻雜更重的擴散工藝制造,這就導致寄生電容相對較高,因而失真(特別是在幅度較高時)和失穩的可能性更高。

?

圖8. 利用限流電阻和兩個齊納二極管提供外部保護的精密運算放大器

早期集成過壓保護

上面討論了放大器的一些常用外部保護方法的缺點。如果放大器本身的設計能夠耐受較大的輸入過壓,那么其中的一些缺點是可以避免的。圖9顯示了差分輸入對采用的常見集成保護方案。

?

圖9. 帶阻性過壓保護的差分輸入對(未顯示ESD保護)

在該電路中,兩個放大器輸入端均有輸入保護電阻。雖然一般情況下只有一個輸入端需要過壓保護,但使各輸入端的寄生電容和漏電流均衡可以降低失真和失調電流。此外,二極管不必處理ESD事件,因而可以相對較小。

增加電阻,無論是外置還是內置,均會增加放大器的和方根(RSS)熱噪聲(公式4):

?

(4)

如果使用1 kΩ電阻來保護噪聲為4 nV/√Hz的運算放大器,總電壓噪聲將提高√2倍。集成保護電阻并不能改變過壓保護會提高等效輸入電壓噪聲的事實,但將R1和R2 與運算放大器集成在一起可確保數據手冊的噪聲規格包括保護電路。

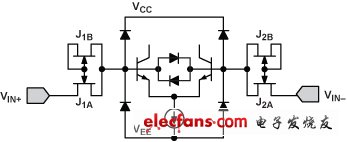

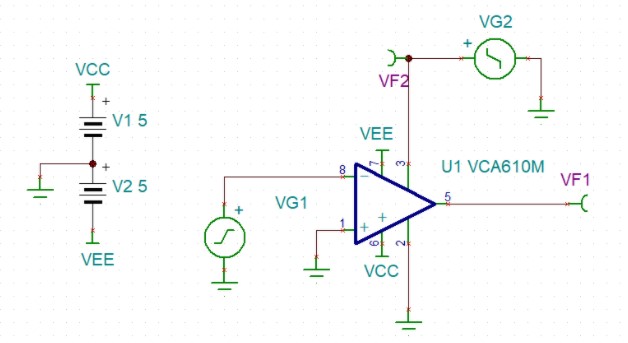

為了避免權衡噪聲與過壓,需要這樣一種保護電路:當放大器輸入在額定范圍內時,它提供低電阻;當放大器輸入超過供電軌時,它提供高電阻。這種特性將能按需改善過壓保護,降低正常工作時的總噪聲貢獻。圖10顯示了一種具有該特性的電路方案.

?

圖10. 帶主動過壓保護的輸入差分對

Jxy全部是P溝道JFET,它們是耗盡型器件,因此溝道的摻雜類型與源極和漏極相同。當放大器輸入電平介于兩個供電軌之間時,J1A和J2A是簡單的電阻,阻值等于RDSON 因為輸入偏置電流足夠小,溝道與柵極之間的任何電位差都不會使溝道關閉。如果VIN+ 超出負電源一個二極管壓降,電流就會流過J1A,導致漏極關閉。這種轉換實際上是 J1A離開三極工作區,進入線性工作區。如果VIN+超出正電源一個二極管壓降,J1A將充當橫向PNP。VIN+至柵極將用作正偏射極-基極結,另一個結用作基極-集電極,其高阻值避免輸入管過壓。

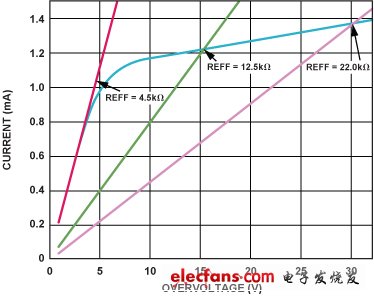

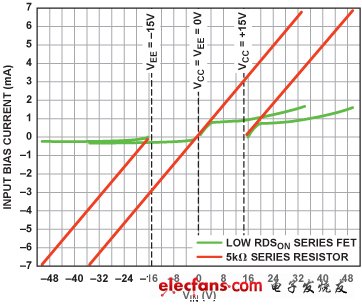

圖11中的電流-電壓曲線顯示了FET保護運算放大器在受到過壓掃描時的輸入阻抗變化。保護FET的RDSON為4.5 kΩ;當放大器的正輸入被拉至供電軌以上時,保護FET的電阻迅速提高到22 kΩ(30 V時),從而將輸入電流限制為1.5 mA。

?

圖11. FET保護運算放大器在受到直流過壓掃描時的有效輸入阻抗

集成的優勢

ADA4091和ADA4096等放大器證明,實現魯棒的輸入過壓保護對運算放大器的精度影響非常小(如圖10所示)。ADA4096能夠提供與電源電平無關的32 V過壓保護,從而無需雖然廉價但會大幅降低放大器精度的外部器件,或者雖然精密但成本高于放大器本身的外部器件。

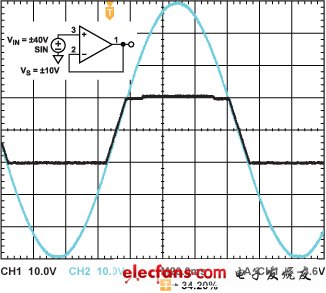

圖12顯示了2 mm × 2 mm LFCSP封裝的ADA4096-2和幾個常用于外部輸入保護的分立器件。ADA4096-2的集成保護使PCB尺寸大幅縮小,其影響已包括在運算放大器的技術規格中。即使未施加電源,它也能保護放大器(見圖13)。此外,ADA4091和ADA4096具有軌到軌輸入和輸出特性(RRIO),在整個過壓保護范圍內都不會發生反相(見圖14)。這些優勢使得系統設計師可以少擔心電源時序控制和閂鎖問題。

?

圖12. 2 mm × 2 mm LFCSP封裝ADA4096-2占用的面積少于兩個常用于外部過壓保護的器件

?

圖13. 有電源和無電源兩種情況下ADA4096-2輸入過壓保護的限流

?

圖14. ADA4096-2采用±10 V電源,輸入被拉至供電軌以上和以下30 V

結論

總而言之,集成過壓保護具有許多優勢:

提高模擬信號鏈的魯棒性和精度

縮短產品上市時間(TTM)、設計時間,降低測試要求

降低BOM(物料清單)成本

核準器件清單所需的器件更少

PCB尺寸更小、密度更高

故障率更低

電子發燒友App

電子發燒友App

評論