本文首先會(huì)對(duì)這個(gè)問(wèn)題進(jìn)行一般性地分析,在此基礎(chǔ)上我們將以德州儀器公司 10G SERDES 器件 TLK10002 為例,提出一個(gè)新的解決方案,即采用雙時(shí)鐘模式提供 SERDES系統(tǒng)時(shí)鐘,并且探討

2013-09-26 14:34:31 3258

3258

對(duì)于fifo來(lái)說(shuō),H的設(shè)置至關(guān)重要。既要保證功能性,不溢出丟數(shù),也要保證性能流水。深度設(shè)置過(guò)小會(huì)影響功能,過(guò)大又浪費(fèi)資源。因此,總結(jié)下fifo設(shè)計(jì)中深度H的計(jì)算。

2022-08-29 11:19:03 1073

1073 SERDES是英文SERializer(串行器)/DESerializer(解串器)的簡(jiǎn)稱。

2024-01-04 09:04:02 495

495

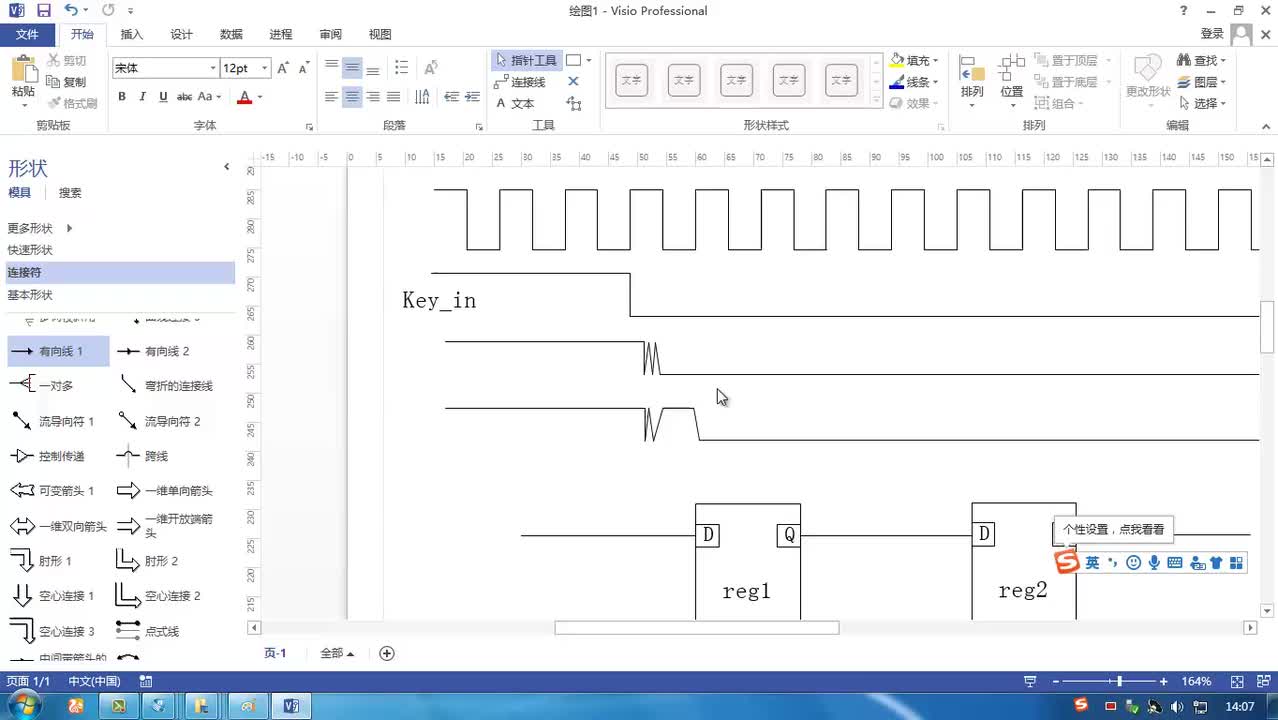

在很久之前便陸續(xù)談過(guò)亞穩(wěn)態(tài),FIFO,復(fù)位的設(shè)計(jì)。本次亦安做一個(gè)簡(jiǎn)單的總結(jié),從宏觀上給大家展示跨時(shí)鐘域的解決方案。

2024-01-08 09:42:26 323

323

。FIFO計(jì)數(shù)器是只讀的。我想知道它怎么能從SUNC出來(lái)。有沒(méi)有辦法知道馬培德在PIC結(jié)構(gòu)中的位置?AD中斷在我的代碼中是高優(yōu)先級(jí)的,唯一的其他中斷是低優(yōu)先級(jí)的UART。到目前為止,這個(gè)解決方案似乎可以解決我

2019-09-03 10:06:01

7174-10002

2023-03-28 14:49:47

本文以TLK3132為例,詳細(xì)介紹了SERDES工作原理和器件特點(diǎn),并以WI系統(tǒng)中的CPRI應(yīng)用需求為例,提供TLK3132的設(shè)計(jì)方法等。

2021-05-25 06:40:19

的ASSP 或ASIC 器件。在過(guò)去幾年中已經(jīng)看到有內(nèi)置SERDES 的FPGA 器件系列,但多見(jiàn)于高端FPGA芯片中,而且價(jià)格昂貴。 本方案是以CME最新的低功耗系列FPGA的HR03為平臺(tái),實(shí)現(xiàn)8

2019-05-29 17:52:03

用戶在產(chǎn)品選型和方案設(shè)計(jì)之初,對(duì)于硬件接口資源分配不熟悉,不遵守芯片規(guī)范使用導(dǎo)致項(xiàng)目出現(xiàn)問(wèn)題,造成了嚴(yán)重?fù)p失。本期我們就此系列平臺(tái)的SerDes資源分配做一篇文章。LS系列產(chǎn)品的資源不可為不豐富,其中最讓人頭暈的當(dāng)屬于SerDes協(xié)議。百度百科這樣解釋,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

FPGA發(fā)展到今天,SerDes(Serializer-Deserializer)基本上是標(biāo)配了。從PCI到PCI Express, 從ATA到SATA,從并行ADC接口到JESD204, 從RIO

2021-07-28 07:02:12

TLK10002 10-Gbps, Dual-Channel, Multi-Rate Transceiver datasheet (Rev. B)

2022-11-04 17:22:44

EVAL MODULE FOR TLK10002

2023-03-30 11:43:46

我們將兩片 TLK 3101之間用光收發(fā)模塊通過(guò)光纖互聯(lián),TLK 3101和光收發(fā)模塊之間的接口匹配不存在問(wèn)題,光功率都在正常的范圍之內(nèi) ,但在實(shí)驗(yàn)室測(cè)試中經(jīng)常出現(xiàn)TLK 3101幀同步丟失

2019-02-28 07:04:13

TLK2501 - Interface, Serializer, Deserializer (SerDes) Evaluation Board

2023-03-29 22:54:00

是同軸銅纜、控制阻抗背板或光纖鏈路。然后將其重構(gòu)為其原始并行格式。與并行解決方案相比,它可以節(jié)省大量的功耗和成本,并且可以面向未來(lái)提供可擴(kuò)展性,以提高數(shù)據(jù)速率。TLK2711-SP 可執(zhí)行并行至串行

2021-03-24 16:27:52

TLK3132工作原理是什么?TLK3132在CPRI接口中有哪些應(yīng)用?

2021-05-25 06:53:11

TLK7-EVM是一款由廣州創(chuàng)龍基于Xilinx Kintex-7系列FPGA自主研發(fā)的核心板+底板方式的開(kāi)發(fā)板,可快速評(píng)估FPGA性能。核心板尺寸僅80mm*58mm,底板采用沉金無(wú)鉛工藝的6層板

2021-12-28 08:15:14

CSS單行、多行文本溢出顯示省略號(hào)(……)解決方案

2020-05-20 17:06:47

F28035 的FIFO怎樣判斷是否溢出?怎樣清除?急

2020-05-08 06:11:11

我正在嘗試在流模式下使用 INT2 引腳進(jìn)行 FIFO 溢出,因?yàn)槲液鼙浚粚?INT2 連接到我的 MCU。INT1 是 NC。試圖避免使用新板。數(shù)據(jù)表似乎自相矛盾,但我想我遺漏了什么。我已經(jīng)嘗試

2022-12-15 06:19:05

很多人卡在這里吧if (tmp[0] & BIT_FIFO_OVERFLOW) {mpu_reset_fifo();return -2;問(wèn)題的本質(zhì)就是,讀取數(shù)據(jù)速度不夠快導(dǎo)致FIFO溢出

2019-04-15 01:05:57

抄了原子哥的驅(qū)動(dòng)代碼,放在了c8t6最小系統(tǒng)板上去跑,一切正常,自檢原本通過(guò)不了,一頓操作后可以通過(guò)了,加速度角速度讀取也OK,唯獨(dú)讀取FIFO中的數(shù)據(jù)讀不出來(lái)具體為mpu_dmp_get_data

2022-02-10 06:12:34

可能是出現(xiàn)FIFO溢出問(wèn)題解析,不斷進(jìn)行循環(huán)讀fiffo就可以得到正常數(shù)據(jù)。形如這樣:注意:printf(“pitch:%froll:%fyaw:%f\r\n”,pitch,roll,yaw);語(yǔ)句不要放在while里面!

2022-02-10 08:03:14

隨著SerDes芯片集成度,復(fù)雜度,傳輸速率的不斷提高,傳統(tǒng)的自動(dòng)化測(cè)試系統(tǒng)已經(jīng)無(wú)法滿足SerDes測(cè)試速率需求。為解決該測(cè)試難題,通過(guò)Nautilus UDI方案的導(dǎo)入,成功得實(shí)現(xiàn)了32 Gbps

2021-05-10 06:58:55

我想使用STM32F407的CAN通訊來(lái)接收六維力傳感器的力信息,但是這個(gè)信息長(zhǎng)度有31個(gè)字節(jié),當(dāng)STM32發(fā)送請(qǐng)求力信息的命令時(shí),傳感器采集卡一次性就發(fā)出4幀的數(shù)據(jù)幀,使接收FIFO溢出。想利用

2024-03-12 07:55:27

mpu6050移植的網(wǎng)上調(diào)試成功的程序,但有問(wèn)題,單步調(diào)試好像FIFO溢出,論壇上有說(shuō)I2C速率不夠的,用的模擬I2C,這個(gè)怎么辦啊?

2016-04-18 14:47:11

描述這款經(jīng)過(guò)驗(yàn)證的參考設(shè)計(jì)是一個(gè)完整的四通道 SDI 聚合與解聚解決方案。使用一個(gè) TLK10022 將四個(gè)同步 HD-SDI 源聚合到一條 5.94 Gbps 串行鏈路中。串行數(shù)據(jù)經(jīng)由銅纜或光纜

2022-09-20 06:46:43

什么是SerDes?

2021-06-24 07:52:02

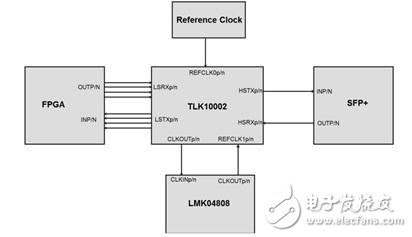

包含用于訪問(wèn)高速信號(hào)(高達(dá) 10Gbps)的 SFP+ 光學(xué)模塊倉(cāng)的雙通道 XAUI 至 SFI 參考設(shè)計(jì)支持靈活的計(jì)時(shí)方案,包括從高速側(cè)恢復(fù)的外部抖動(dòng)消除時(shí)鐘采用 TLK10232 器件,該器件是唯一

2018-08-02 08:26:56

基于Blackfin的解決方案 針對(duì)ADSP-BF706 BLACKFIN+處理器的EVWSS軟件架構(gòu)基于SigmaDSP的解決方案

2021-01-21 06:25:57

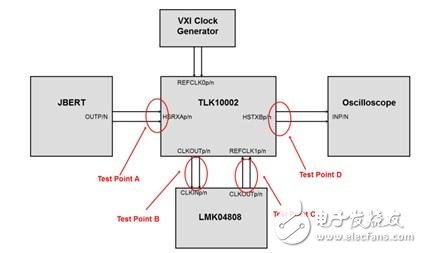

遵循信號(hào)走線限制,這些接口的抖動(dòng)余地仍然是非常小的。固定頻率振蕩器可用于很多通用的SERDES標(biāo)準(zhǔn);但是,這些解決方案價(jià)格昂貴。此外,這種做法缺乏靈活性,并且使調(diào)試、測(cè)試和生產(chǎn)變得困難。另一種解決方案

2019-05-21 05:00:13

業(yè)內(nèi)首個(gè)signoff驅(qū)動(dòng)的PrimeECO解決方案發(fā)布

2020-11-23 14:28:15

使用NVRAM的簡(jiǎn)單解決方案

2021-01-13 06:56:35

數(shù)據(jù)進(jìn)入FPGA的速率高于傳出的速率,持續(xù)的傳輸會(huì)造成數(shù)據(jù)的溢出,斷續(xù)的傳輸可能會(huì)造成數(shù)據(jù)不連續(xù)。使用基于LabVIEW FPGA的DMA FIFO作為主控計(jì)算機(jī)和FPGA之間的緩存,若DMAFIFO深度設(shè)置的合適,FIFO不會(huì)溢出和讀空,那么就能實(shí)現(xiàn)數(shù)據(jù)輸出FPGA是連續(xù)的。

2019-10-12 09:05:54

本方案是以CME最新的低功耗系列FPGA的HR03為平臺(tái),實(shí)現(xiàn)8/10b的SerDes接口,包括SERDES收發(fā)單元,通過(guò)完全數(shù)字化的方法實(shí)現(xiàn)SERDES的CDR(Clock Data

2019-10-21 07:09:44

2048正好是我設(shè)定的FIFO深度,所以問(wèn)題應(yīng)該是FIFO溢出了,我是這樣理解的:PALIN_mReadFromFIFO()這個(gè)函數(shù)雖然讀出了fifo中的數(shù)據(jù),但是并沒(méi)有釋放fifo的空間,導(dǎo)致只能正確

2014-05-28 19:57:05

SerDes的基本結(jié)構(gòu)是由哪些部分組成的?怎樣去更好地使用SerDes?

2021-09-22 06:25:17

SerDes是怎么工作的?SerDes有傳輸時(shí)鐘信號(hào)嗎?

2021-10-18 08:53:42

為 EMI 敏感和高速 SERDES 系統(tǒng)供電

2019-05-21 14:34:36

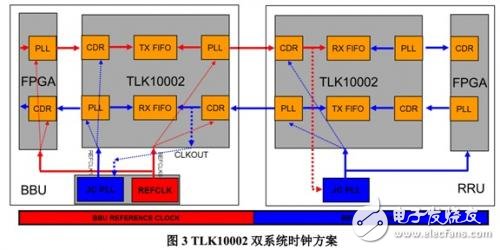

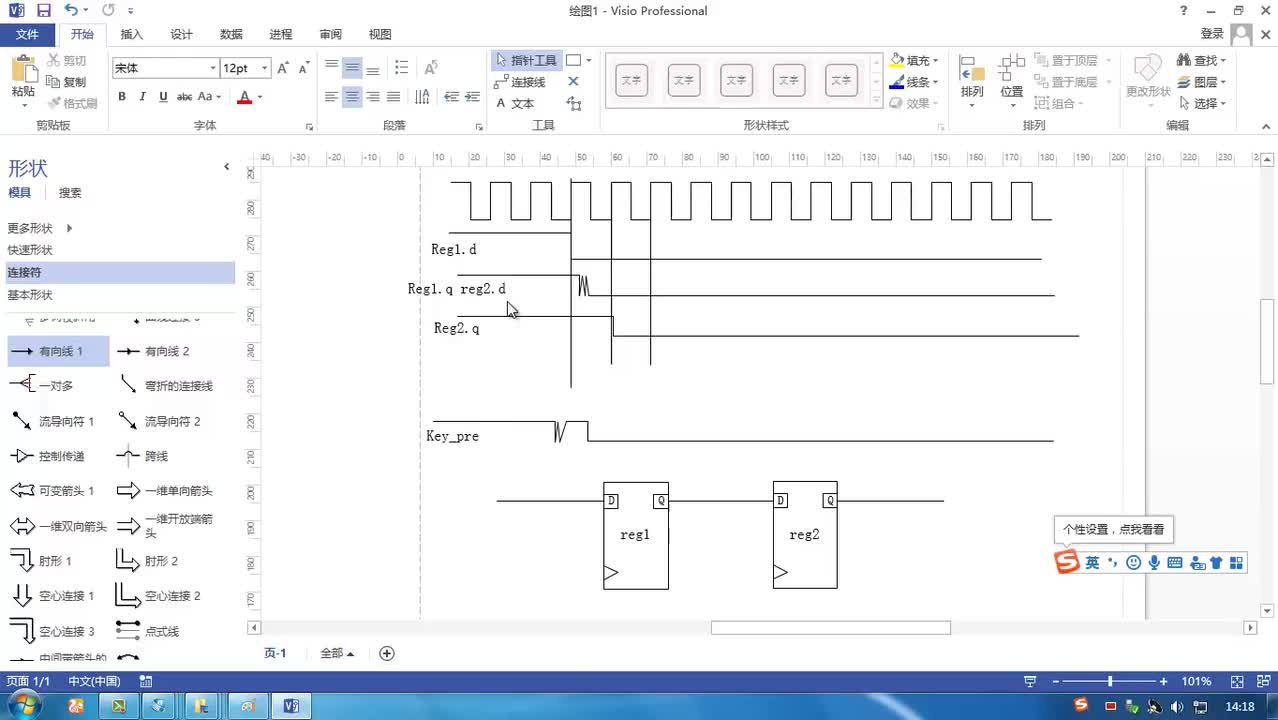

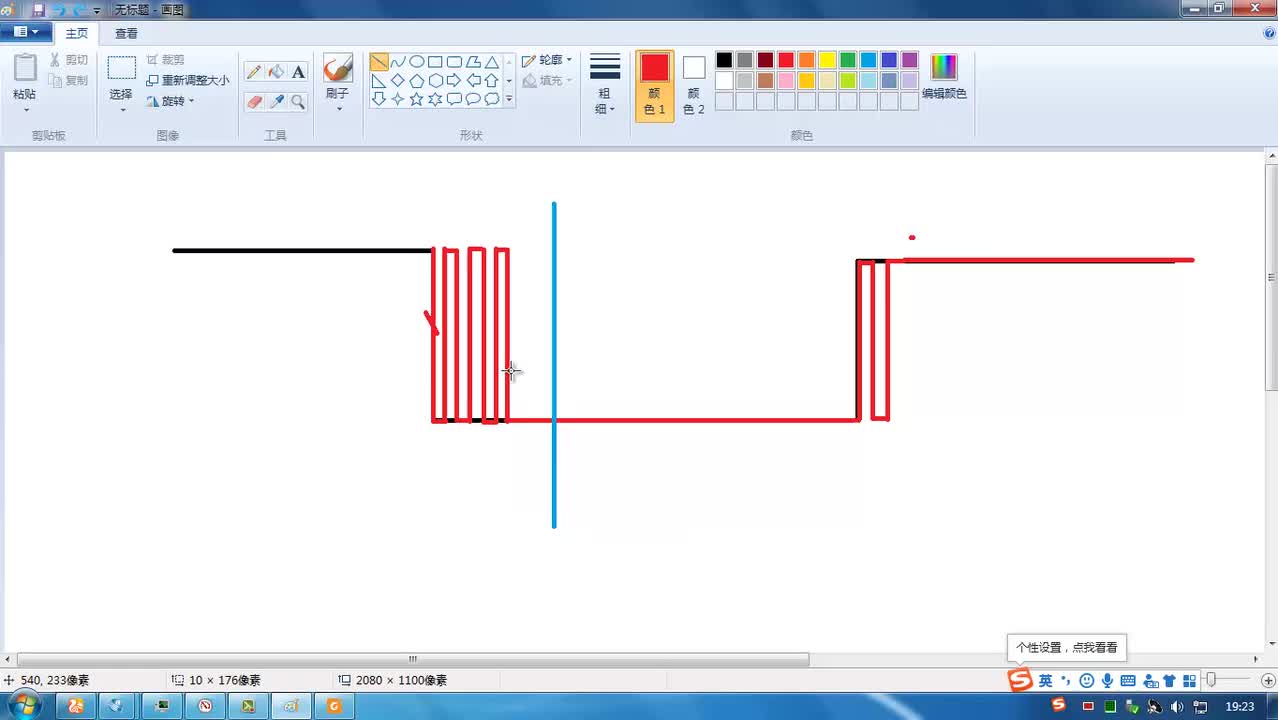

漂移及漂移形成的原因是什么?光纖漂移引起的SERDES FIFO溢出問(wèn)題分析BBU SERDES 雙系時(shí)鐘方案及具體實(shí)現(xiàn)

2021-04-19 08:35:11

6678中的srio的serdes和以太網(wǎng)的serdes是共用還是各自有自己的serdes?

2018-08-02 06:11:31

您好!我想請(qǐng)問(wèn)一下,TLK2711的數(shù)字地可不可以接普通的數(shù)字地,如果不可以,會(huì)有什么問(wèn)題出現(xiàn)?謝謝!

2019-05-20 14:09:42

用戶在產(chǎn)品選型和方案設(shè)計(jì)之初,對(duì)于硬件接口資源分配不熟悉,不遵守芯片規(guī)范使用導(dǎo)致項(xiàng)目出現(xiàn)問(wèn)題,造成了嚴(yán)重?fù)p失。本期我們就此系列平臺(tái)的SerDes資源分配做一篇文章。LS系列產(chǎn)品的資源不可為不豐富,其中

2020-10-28 17:15:14

用戶在產(chǎn)品選型和方案設(shè)計(jì)之初,對(duì)于硬件接口資源分配不熟悉,不遵守芯片規(guī)范使用導(dǎo)致項(xiàng)目出現(xiàn)問(wèn)題,造成了嚴(yán)重?fù)p失。本期我們就此系列平臺(tái)的SerDes資源分配做一篇文章。?LS系列產(chǎn)品的資源不可為不豐富,其中

2020-11-01 20:21:02

串行化為更高速度的數(shù)據(jù)流。隨后您既可通過(guò)高性能線纜傳輸該數(shù)據(jù)流,也可通過(guò)光模塊由光纖傳輸。在另一端,您可通過(guò)解串串行化數(shù)據(jù)重新構(gòu)建最初較慢速度的串行鏈路。要簡(jiǎn)化這一過(guò)程,您可使用TLK10002雙通道

2018-09-13 10:02:04

The TLK2711A is a member of the WizardLink transceiver family of multigigabit transceivers

2010-09-09 20:31:46 43

43 The TLK1201A/TLK1201AI gigabit ethernet transceiver provides for ultrahigh-speed, full-duplex

2010-09-09 20:42:18 12

12 The TLK2201A and TLK2201AI gigabit ethernet transceivers provide for ultrahigh-speed full-duplex

2010-09-09 20:47:36 23

23 The TLK2201B and TLK2201BI gigabit ethernet transceivers provide for ultrahigh-speed full-duplex

2010-09-09 20:52:22 20

20 什么是fifo (First Input First Output,先入先出隊(duì)列)這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。1.什么是FIFO

2007-12-20 13:51:59 11835

11835 高速串行接口設(shè)計(jì)的高效時(shí)鐘解決方案

數(shù)字系統(tǒng)的設(shè)計(jì)師們面臨著許多新的挑戰(zhàn),例如使用采用了串行器/解串器(SERDES)技術(shù)的高速串行接口來(lái)取代傳統(tǒng)的并行總線架

2010-04-09 13:24:59 968

968

溢出,溢出的檢測(cè)方法有哪些? 在定點(diǎn)小數(shù)機(jī)器中,數(shù)的表示范圍為|x|<1. 在運(yùn)算過(guò)程中如出現(xiàn)大于1的現(xiàn)象,稱為“溢出”。在定點(diǎn)機(jī)中,正常情況下溢出

2010-04-13 11:02:03 11007

11007 德州儀器 (TI) 宣布推出業(yè)界首款 6 千兆位每秒 (Gbps) 的雙通道串行器-解串器 IC (SerDes),其可為無(wú)線應(yīng)用提供 高達(dá)470 兆位每秒 (Mbps) 至6.25 Gbps 的連續(xù)數(shù)據(jù)速率。該TLK6002支持從原有

2010-06-03 08:34:52 1434

1434 SERDES在數(shù)字系統(tǒng)中高效時(shí)鐘設(shè)計(jì)方案,無(wú)論是在一個(gè)FPGA、SoC還是ASSP中,為任何基于SERDES的協(xié)議選擇一個(gè)參考時(shí)鐘源都是非常具有挑戰(zhàn)性的。

2012-02-16 11:23:43 5383

5383

本文以TLK3132為例,詳細(xì)介紹了SERDES工作原理和器件特點(diǎn),并以WI系統(tǒng)中的CPRI應(yīng)用需求為例,提供TLK3132的設(shè)計(jì)方法等。

2012-05-07 16:01:58 6293

6293

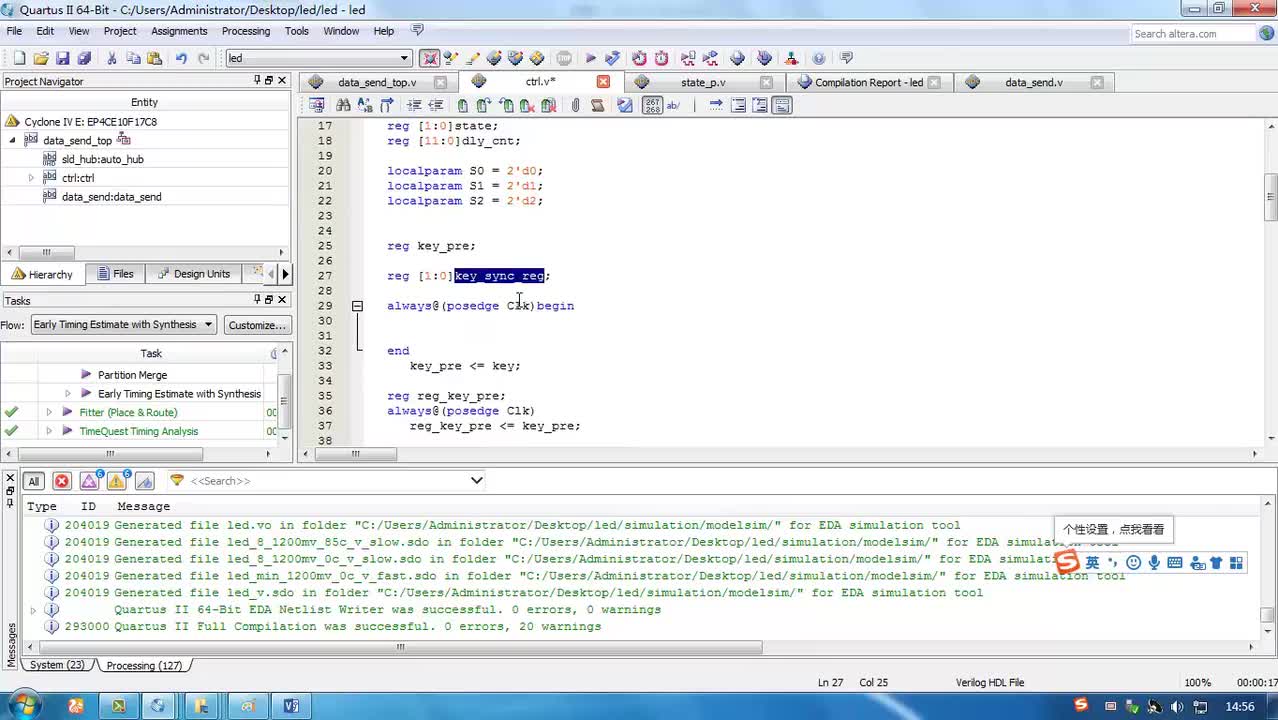

以TI公司的TLK10002為例,研究了多速率環(huán)境下的PRU設(shè)備自適應(yīng)接入問(wèn)題,給出了RRU設(shè)備速率自適應(yīng)的流程圖和方法。采用本方案的RRU設(shè)備,能夠自動(dòng)進(jìn)行通信速率調(diào)整,極大地降低了網(wǎng)絡(luò)

2012-11-09 17:29:01 37

37 針對(duì)實(shí)時(shí)型相機(jī)對(duì)系統(tǒng)小型化、通用化及數(shù)據(jù)高速率可靠傳輸?shù)男枨螅闹性谘芯扛咚俅衅?解串器(SerDes)器件TLK2711工作原理的基礎(chǔ)上,提出了高速串行全雙工通信協(xié)議總體設(shè)計(jì)方

2013-06-25 15:59:43 100

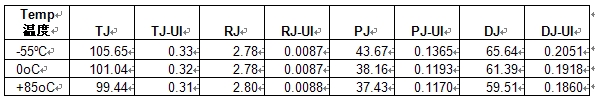

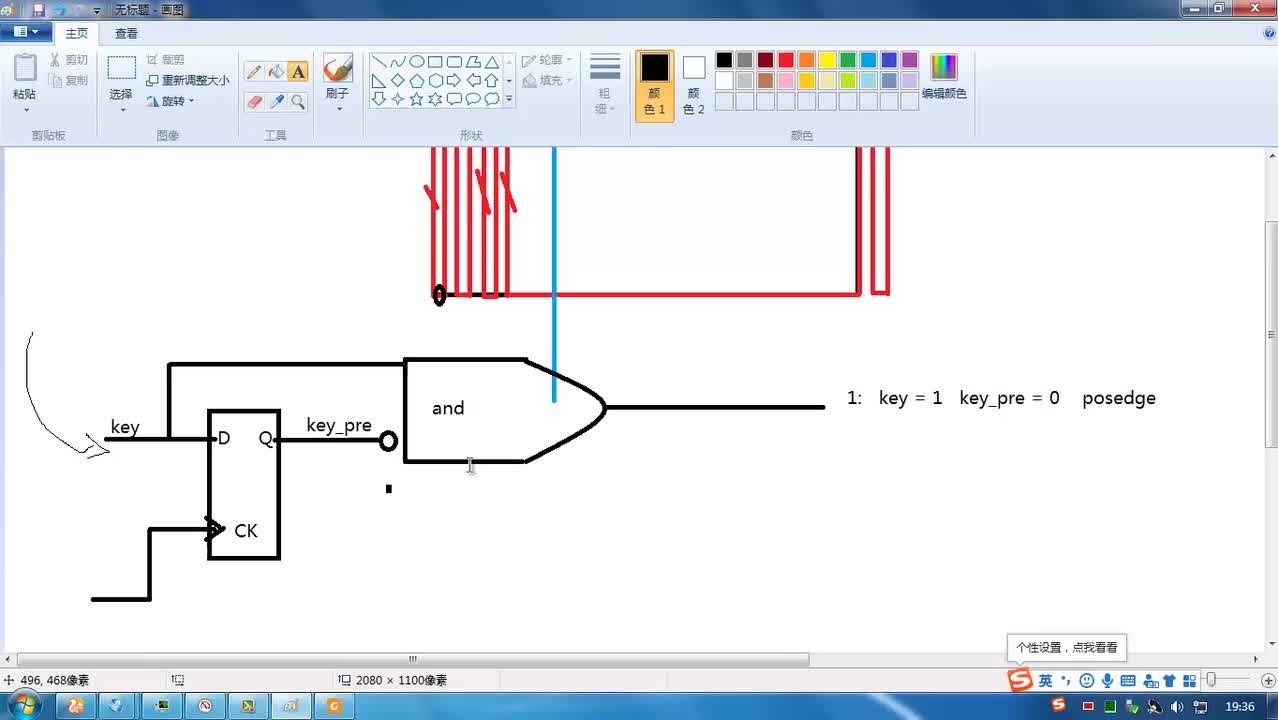

100 深度不夠的情況下有可能會(huì)造成 FIFO 的溢出。本文首先會(huì)對(duì)這個(gè)問(wèn)題進(jìn)行一般性地分析, 在此基礎(chǔ)上我們將以德州儀器公司 10GSERDES 器件 TLK10002 為例,提出一個(gè)新的解決方案,即采用雙時(shí)鐘模式提供 SERDES

系統(tǒng)時(shí)鐘,并且探討了這種模式的具體實(shí)現(xiàn)方式。 同時(shí),為了驗(yàn)

2016-12-21 16:19:33 0

0 TLK2521數(shù)據(jù)手冊(cè)

2017-01-03 11:41:35 0

0 MPU-6000(6050)為全球首例整合性6軸運(yùn)動(dòng)處理組件,相較于多組件方案,免除了組合陀螺儀與加速器時(shí)間軸之差的問(wèn)題,減少了大量的封裝空間。為什么FIFO數(shù)據(jù)會(huì)溢出?MPU6050的DMP在工作的時(shí)候。

2017-11-29 14:38:54 16613

16613 TI 提供的 TLK6002, TLK10002 等多種速率的通用 Serdes 芯片,在不同的領(lǐng)域得到了廣泛的應(yīng)用。特別在光纖拉遠(yuǎn)的應(yīng)用中,由于 TLK6002, TLK10002 獨(dú)特的配置靈活性和優(yōu)良的適配寬容度,已成為業(yè)界的主流配置。

2018-05-08 16:04:33 7

7 隨著SerDes芯片集成度、復(fù)雜度、傳輸速率的不斷提高,傳統(tǒng)的自動(dòng)化測(cè)試系統(tǒng)已經(jīng)無(wú)法滿足SerDes測(cè)試速率需求。但通過(guò)Nautilus UDI方案的導(dǎo)入,成功實(shí)現(xiàn)了32 Gbps SerDes

2018-06-10 10:51:17 4433

4433

電子發(fā)燒友網(wǎng)為你提供TI(ti)TLK1211相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TLK1211的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TLK1211真值表,TLK1211管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發(fā)燒友網(wǎng)為你提供TI(ti)TLK10002相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TLK10002的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TLK10002真值表,TLK10002管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發(fā)燒友網(wǎng)為你提供TI(ti)TLK1221相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TLK1221的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TLK1221真值表,TLK1221管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發(fā)燒友網(wǎng)為你提供TI(ti)TLK100相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TLK100的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TLK100真值表,TLK100管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:10:12

電子發(fā)燒友網(wǎng)為你提供TI(ti)TLK106L相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TLK106L的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TLK106L真值表,TLK106L管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:10:12

電子發(fā)燒友網(wǎng)為你提供TI(ti)TLK105L相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TLK105L的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TLK105L真值表,TLK105L管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:10:12

本方案是以CME最新的低功耗系列FPGA的HR03為平臺(tái),實(shí)現(xiàn)8/10b的SerDes接口,包括SERDES收發(fā)單元,通過(guò)完全數(shù)字化的方法實(shí)現(xiàn)SERDES的CDR(Clock Data

2019-05-24 15:33:25 4072

4072

SERDES的優(yōu)勢(shì) 引腳數(shù)量和通道優(yōu)勢(shì) SERDES最明顯的優(yōu)勢(shì)是具備更少的引腳數(shù)量和線纜/通道數(shù)量。對(duì)于早期的SERDES,這意味著數(shù)據(jù)可以通過(guò)同軸電纜或光纖發(fā)送。 對(duì)于現(xiàn)代的SERDES來(lái)說(shuō)

2021-07-23 11:59:46 3794

3794 電子發(fā)燒友網(wǎng)為你提供ST(ST)STTH10002TV1相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有STTH10002TV1的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,STTH10002TV1真值表,STTH10002TV1管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-02-17 18:33:43

電子發(fā)燒友網(wǎng)為你提供ST(ST)STTH10002TV2相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有STTH10002TV2的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,STTH10002TV2真值表,STTH10002TV2管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-02-17 19:15:19

異步FIFO主要由五部分組成:寫(xiě)控制端、讀控制端、FIFO Memory和兩個(gè)時(shí)鐘同步端

2023-05-26 16:17:20 911

911

首先我們要了解什么是SerDes,SerDes的應(yīng)用場(chǎng)景又是什么呢?SerDes又有哪些常見(jiàn)的種類?

2023-06-06 17:03:55 4706

4706

FIFO,可以直接在自己的設(shè)計(jì)中配置和使用它,該設(shè)計(jì)是完全可綜合的。 為什么要自己設(shè)計(jì)FIFO 那么,為什么呢?網(wǎng)上有很多關(guān)于 FIFO 的 Verilog/VHDL 代碼的資源,過(guò)去,我自己也使用過(guò)其中的一些。但令人沮喪的是,它們中的大多數(shù)都存在問(wèn)題,尤其是在上溢出和下溢出

2023-06-14 09:02:19 461

461 TLK10002SMAEVMTLK10002SMAEVM制造商TLK10002SMAEVM供應(yīng)商TLK10002SMAEVM怎么訂貨TLK10002SMAEVM價(jià)格黃云艷13632767652優(yōu)勢(shì)

2021-12-22 14:33:14 327

327

LogiCORE IP AXI4-Stream FIFO內(nèi)核允許以內(nèi)存映射方式訪問(wèn)一個(gè)AXI4-Stream接口。該內(nèi)核可用于與AXI4-Stream IP接口,類似于LogiCORE IP AXI以太網(wǎng)內(nèi)核,而無(wú)需使用完整的DMA解決方案。

2023-09-25 10:55:33 497

497

FPGA發(fā)展到今天,SerDes(Serializer-Deserializer)基本上是器件的標(biāo)配了。從PCI發(fā)展到PCI-E,從ATA發(fā)展到SATA,從并行ADC接口到JESD204,從RIO

2023-10-16 14:50:37 558

558

同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO各在什么情況下應(yīng)用? 1. 同步FIFO和異步FIFO的區(qū)別 同步FIFO和異步FIFO在處理時(shí)序有明顯的區(qū)別。同步FIFO相對(duì)來(lái)說(shuō)是較為

2023-10-18 15:23:58 789

789 請(qǐng)問(wèn)異步FIFO的溢出操作時(shí)怎么樣判斷的? 異步FIFO是數(shù)據(jù)傳輸?shù)囊环N常用方式,在一些儲(chǔ)存器和計(jì)算機(jī)系統(tǒng)中,常常會(huì)用到異步FIFO。作為一種FIFO,異步FIFO經(jīng)常面臨兩種情況:溢出

2023-10-18 15:28:41 299

299 盡管設(shè)計(jì)和驗(yàn)證很復(fù)雜,SERDES 已成為 SoC 模塊不可或缺的一部分。隨著 SERDES IP 模塊現(xiàn)已推出,它有助于緩解任何成本、風(fēng)險(xiǎn)和上市時(shí)間問(wèn)題。

2023-10-23 14:44:59 449

449

計(jì)算原理,介紹其風(fēng)險(xiǎn)及可能帶來(lái)的后果,并提供一些應(yīng)對(duì)策略和措施,旨在幫助程序員理解溢出問(wèn)題并提供有效的解決方案。 一、溢出計(jì)算原理 1.1 數(shù)據(jù)類型與范圍 C語(yǔ)言中的整型數(shù)據(jù)類型包括char、short、int、long等,它們?cè)趦?nèi)存中占有

2023-11-30 11:45:30 664

664 內(nèi)存溢出與內(nèi)存泄漏:定義、區(qū)別與解決方案? 內(nèi)存溢出和內(nèi)存泄漏是計(jì)算機(jī)科學(xué)中常見(jiàn)的問(wèn)題,在開(kāi)發(fā)和調(diào)試過(guò)程中經(jīng)常會(huì)遇到。本文將詳細(xì)介紹內(nèi)存溢出和內(nèi)存泄漏的定義、區(qū)別以及解決方案。 一、內(nèi)存溢出的定義

2023-12-19 14:10:12 884

884

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論