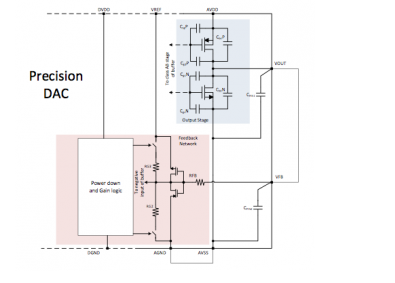

靜態技術規格中,我們探討了靜態技術規格以及它們對DC的偏移、增益和線性等特性的影響。這些特性在平衡雙電阻 (R-2R) 和電阻串數模轉換器 (DAC) 的各種拓撲結構間是基本一致的。

2015-12-09 15:16:32 3332

3332

在使用數模轉換器 (DAC) 進行設計時,您肯定希望輸出能夠從一個值向另一個值單調轉換,但實際電路并不總是以這種方式工作的。在某些特定代碼范圍內出現過沖與下沖(即干擾脈沖)也很平常。這些脈沖

2018-04-10 09:04:54 9009

9009

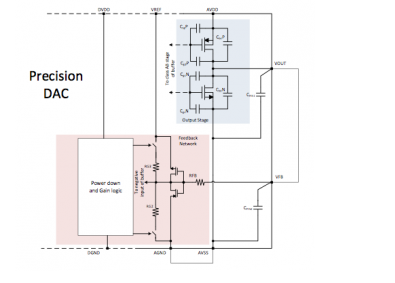

該篇將分析對象限定為一個DAC,其中的輸出緩沖器在正常模式下被加電:零量程或中量程。文章將分析一下DAC輸出在高阻抗模式中被加電的情況。同時提出一個針對加電毛刺脈沖的數學模型,隨后給出一個盡可能

2020-10-23 15:11:12 4445

4445

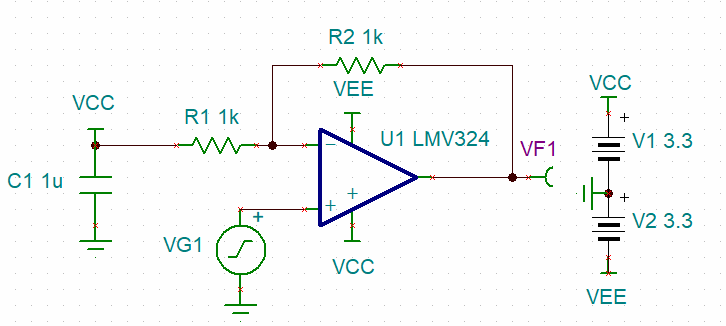

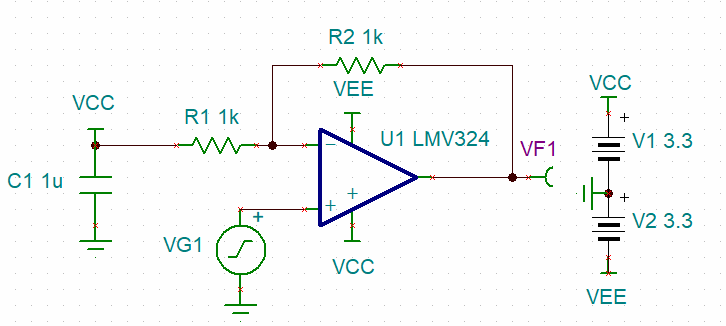

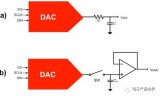

絕大多數的DAC都是單極性的,只有極少數的DAC是雙極性輸出,使用單極性DAC要想輸出雙極性信號,那么只需要將輸出的單極性信號通過電平的平移使其變為雙極性信號,此時就需要用到運放。使用運放搭建的減法電路應用就可以,下面來看一下例子。

2022-11-02 16:38:30 4245

4245

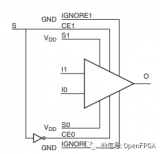

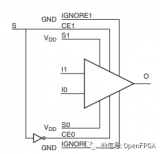

大部分開發者使用 BUFGCTRL 或 BUFGMUX進行時鐘切換,它們在時鐘切換上可以提供無毛刺輸出。

2023-08-16 09:05:15 790

790

DAC輸出多路模擬電壓量時搭配信號多路復用器使用時,尤其在不同的通道間進行切換時,在其輸出端會產生微小電壓毛刺或反沖。該反沖與多路復用器的開啟和關斷時間、導通電阻以及負載電容成函數關系。具有低導通電

2020-08-19 15:56:31

16位、八通道、超低毛刺、電壓輸出DAC,具有2.5V、2ppm/°C內部基準

2023-03-24 15:06:36

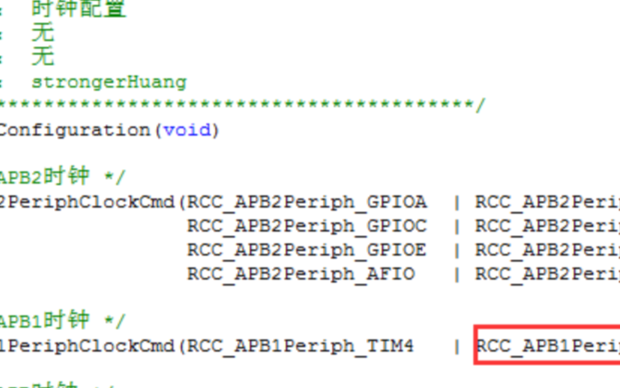

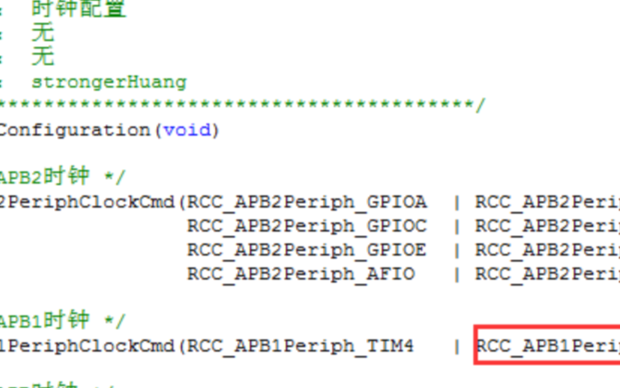

1.1案例 DAC輸出1.1.1 簡介DAC(數模轉換器)是一個將數字信號轉換為模擬輸出信號的外設,AT32F437擁有2個DAC,兩個DAC相互獨立,可以獨立進行數模轉換,也可以雙DAC同時觸發

2022-03-28 20:12:31

參考:野火教程 第38章 DAC—輸出正弦波文章目錄PWM 介紹DAC 介紹PWM 介紹PWM是一種對模擬信號電平進行數字編碼的方法。通過高分辨率計數器的使用,方波的占空比被調制用來對一個具體

2021-08-06 09:18:45

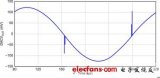

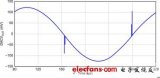

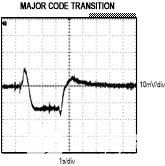

的是 000H。圖2 中的黃色曲線顯示的就是這種情況 ;在 MSB 切換并將 DAC 輸出拉回 800H 之前,輸出朝 0 V 變化。圖 2. 中間電平毛刺數字 SFDR無雜散動態范圍 (SFDR

2018-10-29 16:51:40

乘法 DAC 是波形發生應用的理想構建模塊。因為乘法數模轉換器 (DAC) 的 R-2R 架構非常適合低噪聲、低毛刺、快速建立的應用。從固定參考輸入電壓產生波形時,必須考慮一些重要的交流規格,包括建立時間、中間電平毛刺和數字 SFDR。今天我們就來分析下這些與波形發生相關的重要 DAC 規格。

2019-07-18 08:17:48

我使用AD5781的評估板,輸出10Hz 100mV的正弦波,我讀入AD7768-1的數據再通過AD5781輸出,我AD7768-1采集的數據中沒有毛刺,但我AD5781輸出的數據經過運放

2023-12-07 06:04:30

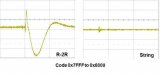

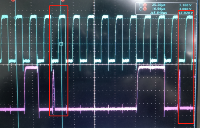

在測試AD9117時,用FPGA給DAC一個正弦波的數字信號,在輸出端發現有脈沖毛刺出現,在示波器上有毛刺的余暉。在頻譜上會有底噪抖動,我認為是毛刺造成,請問是否知道關于這個毛刺生成的有關原因

2019-01-17 08:19:07

在測試AD9117時,用FPGA給DAC一個正弦波的數字信號,在輸出端發現有脈沖毛刺出現,在示波器上有毛刺的余暉。在頻譜上會有底噪抖動,我認為是毛刺造成,請問是否知道關于這個毛刺生成的有關原因

2023-12-13 06:19:05

無毛刺 。 可 ADuM3200 的輸出 卻總是 存在 10nS 到20nS 的毛刺。 急求 AD 公司 技術專家 給予 解答 ,萬分感謝 。。急。。

2018-08-17 06:59:53

冒險出現在變量發生變化的時刻,如果待信號穩定之后加入取樣脈沖,那么就只有在取樣脈沖作用期間輸出的信號才能有效。這樣可以避免產生的毛刺影響輸出波形。一般說來,冒險出現在信號發生電平轉換的時刻,也就是說在

2023-11-02 17:22:20

電平轉換也需要一定的上升或下降時間。由于存在這些因素的影響,多個信號的電平值發生變化時,在信號變化的瞬間,組合邏輯的輸出并非同時,而是有先有后,因此往往會出現一些不正確的信號,例如一些很小的脈沖尖峰信號

2015-07-08 10:38:02

所需的慣性角速率測量信息;增加數字預濾器,以濾除陀螺脈沖輸出信號中的尖峰或毛刺干擾,可以進一步提高解調精度;為滿足實時性要求,該方法采用FPGA來實現;實驗表明,相對整周期采樣解調,此方法提高了解調精度

2018-08-30 09:21:12

的瞬間,組合邏輯的輸出常常產生一些小的尖峰,即毛刺信號,這是由FPGA內部結構特性決定的。毛刺現象在FPGA的設計中是不可避免的,有時任何一點毛刺就可以導致系統出錯,尤其是對尖峰脈沖或脈沖邊沿敏感

2012-09-06 14:37:54

MCU的DAC輸出經過DAC0832直接用MCU生成DAC豈不是更好?用DAC芯片DAC0832有哪些考慮?(生成正負反相的兩組波形?)用MCU的兩個PWM口也是直接可以做到的啊!DAC0832價格也挺貴

2022-01-19 11:48:22

STM32的DAC上電時輸出一個幅值100mV,脈寬5ms的脈沖,影響后面電路的工作,怎么去掉這個脈沖呢?

2023-10-28 06:08:55

需要一定的過渡時間。由于存在這兩方面因素,多路信號的電平值發生變化時,在信號變化的瞬間,組合邏輯的輸出有先后順序,并不是同時變化,往往會出現一些不正確的尖峰信號,這些尖峰信號稱為"毛刺

2012-02-10 09:50:36

stm32的DAC輸出一、DAC原理二、DAC初始化三、輸出正弦波四、輸出音頻一、DAC原理DAC 為數字/模擬轉換模塊,故名思議,它的作用就是把輸入的數字編碼,轉換成對 應的模擬電壓輸出,它的功能

2021-08-16 08:53:01

我是參考16位DAC的代碼配置的,會不會是我的輸出程序錯了呢?

2022-11-04 11:25:10

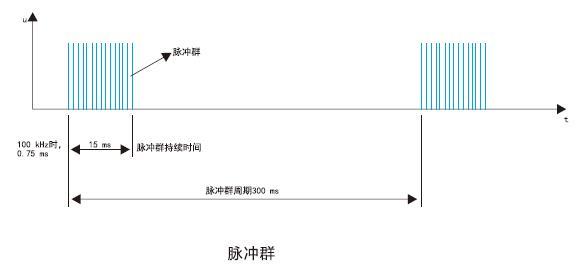

其實,對于共模干擾的困擾都是來自于實際操作中。而共模干擾往往對系統損傷最大,打比方如大功率電機、斷路器或開關,短路,雷擊感應等,這些類型大都是外來的共模信號,其脈寬在數百us到s之間,周期最長也是

2020-11-03 08:36:34

使用dac的dma模式輸出一定數目的脈沖波形,dac使用定時器觸發,dma環形緩沖,在dma中斷中判斷已經輸出的波形數目,達到設定數目時停止dac,使用示波器觀察波形數量與設定的不一致,請問是什么原因造成的?

2023-08-07 08:47:39

使用dac的dma模式輸出一定數目的脈沖波形,dac使用定時器觸發,dma環形緩沖,在dma中斷中判斷已經輸出的波形數目,達到設定數目時停止dac,使用示波器觀察波形數量與設定的不一致,請問是什么原因造成的?

2024-03-18 07:16:56

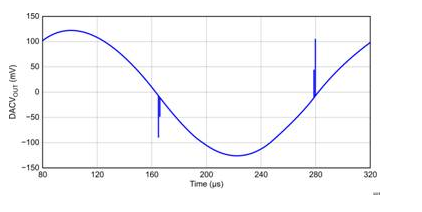

,但是將程序下載到電路板上發現輸出端的信號為:

這個圖是通過示波器直接測芯片DAC0輸出端的波形,而且該輸出端未接任何東西,2.5v電壓正常,但是會出現周期性的毛刺,毛刺大致值為180mV左右

2024-01-12 07:44:18

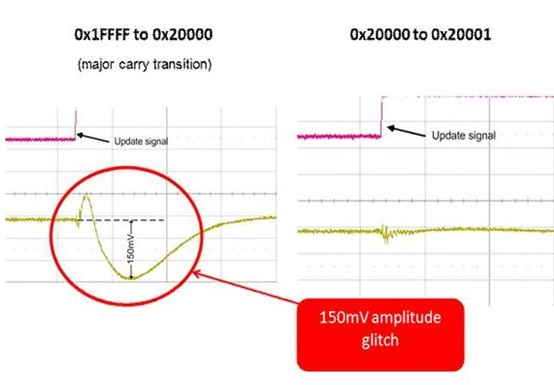

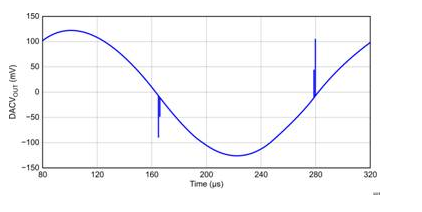

的辦法是繞過去。昨天,在我減速通過一條討厭的減速帶時,突然想到了我的那個精密型16 位R-2R DAC。它在中間刻度時存在短時脈沖波形干擾問題(請參見圖1)。我想,在選擇使用具有較大短時脈沖波形干擾特性

2019-06-20 06:23:38

如何解決電路中短時脈沖波形失真的所謂“毛刺”現象?并提出相應的解決辦法。

2021-04-08 06:25:08

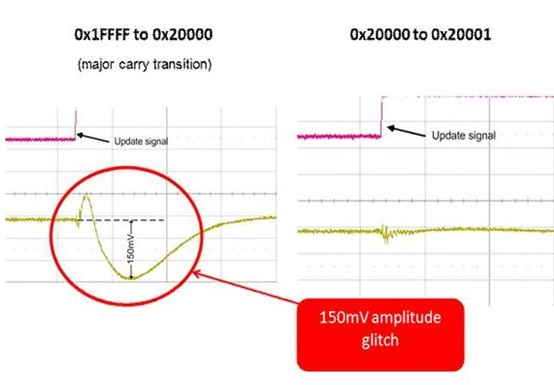

011 的 3 個 MSB。DAC 輸出進入主要進位轉換后,會導致所有 R-2R 開關短時間接地。短期開關電荷注入之后,DAC 恢復,同時輸出開始趨穩。通過比較主要進位轉換與非主要進位轉換的輸出干擾

2018-09-14 15:29:05

在使用數模轉換器 (DAC) 進行設計時,您肯定希望輸出能夠從一個值向另一個值單調轉換,但實際電路并不總是以這種方式工作的。在某些特定代碼范圍內出現過沖與下沖(即干擾脈沖)也很平常。這些脈沖會以

2022-11-22 06:14:59

在上一篇 DAC 基礎知識博文中,我們對高精度數模轉換器 (DAC) 中的輸出干擾源進行了探討。若您希望在增加代碼的過程中獲得線性轉換,那么這些輸出脈沖可能會擾亂系統運行。讓我們快速回顧一下我在上

2022-11-22 06:20:07

作者:Tony Calabria德州儀器在上一篇 DAC 基礎知識博文中,我們對高精度數模轉換器 (DAC) 中的輸出干擾源進行了探討。若您希望在增加代碼的過程中獲得線性轉換,那么這些輸出脈沖

2018-09-14 14:53:24

與ESD損壞相似。 3.閃電。 4.測試程序開關引起的瞬態/毛刺/短時脈沖波形干擾。 5.測試設計欠佳,例如,在器件尚未加電或已超過其操作上限的情況下給器件發送測試信號。再比如在對器件供電之前

2013-03-18 14:38:44

問題。

競爭冒險:在組合電路中,當邏輯門有兩個互補輸入信號同時向相反狀態變化時,輸出端可能產生過渡干擾脈沖的現象,稱為競爭冒險。

那么 FPGA 產生競爭冒險的原因是什么呢?

信號在

2023-05-30 17:15:28

描述DAC R-2R 架構在噪音和精確度方面展現出了很高的性能,但代價是干擾區域較大。該設計專注于減少 DAC R-2R 架構中特定于代碼的轉換所引起的主要攜帶干擾。該設計可縮小此干擾區域,從而

2018-11-07 16:40:50

求大神,dac如何用光耦隔離? 我現在在弄的板子有輸出dac,有輸出pwm,但是dac總是干擾pwm ,如何能將dac或者pwm隔離開呢?使用的芯片是stm32芯片

2019-01-26 18:08:30

DAC6551-Q1 汽車類 12 位、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 12 Number of DAC channels (#) 1

2022-12-06 09:49:25

DAC8551-Q1 汽車類 16 位、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 16 Number of DAC channels (#) 1

2022-12-06 09:49:28

具有 2.5V、4ppm/°C 基準的 14 位、雙路、低功耗、超低毛刺脈沖、緩沖電壓輸出 DAC Resolution (Bits) 14 Number of DAC

2022-12-06 09:49:54

具有 2.5V、4ppm/°C 基準的 12 位、雙路、低功耗、超低毛刺脈沖、緩沖電壓輸出 DAC Resolution (Bits) 12 Number of DAC

2022-12-06 09:49:55

具有 2.5V、4ppm/°C 基準的 14 位、雙路、低功耗、超低毛刺脈沖、緩沖電壓輸出 DAC Resolution (Bits) 14 Number of DAC

2022-12-06 09:49:55

具有 2.5V、4ppm/°C 基準的 16 位、雙路、低功耗、超低毛刺脈沖、緩沖電壓輸出 DAC Resolution (Bits) 16 Number of DAC

2022-12-06 09:49:56

具有 2.5V、4ppm/°C 基準的 12 位、雙路、低功耗、超低毛刺脈沖、緩沖電壓輸出 DAC Resolution (Bits) 12 Number of DAC

2022-12-06 09:49:56

8 位、8 通道、超低毛刺脈沖、電壓輸出、2 線接口 DAC Resolution (Bits) 8 Number of DAC channels (#) 8

2022-12-06 09:50:00

10 位、8 通道、超低毛刺脈沖、電壓輸出、2 線接口 DAC Resolution (Bits) 10 Number of DAC channels (#) 8

2022-12-06 09:50:01

具有 2.5V 內部參考的 12 位、8 通道、超低毛刺脈沖、電壓輸出、2 線接口 DAC Resolution (Bits) 12 Number of DAC channels

2022-12-06 09:50:01

12 位、8 通道、超低毛刺脈沖、電壓輸出、2 線接口 DAC Resolution (Bits) 12 Number of DAC channels (#) 8

2022-12-06 09:50:02

具有 2.5V、2ppm/℃ 內部參考的 14 位、八通道、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 14 Number of DAC channels

2022-12-06 09:50:10

具有 2.5V、2ppm/℃ 內部參考的 12 位、八通道、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 12 Number of DAC channels

2022-12-06 09:50:11

具有 2.5V、2ppm/°C 內部基準的 16 位、八通道、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 16 Number of DAC channels

2022-12-06 09:50:11

具有 2.5V、2ppm/°C 內部基準電壓和復位功能的 12 位、四通道、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 12 Number of DAC

2022-12-06 09:50:17

具有 2.5V、2ppm/C 內部基準的 16 位、四通道、超低毛刺脈沖、電壓輸出 DAC Resolution (Bits) 16 Number of DAC channels

2022-12-06 09:50:22

16 位超低毛刺脈沖電壓輸出 DAC Resolution (Bits) 16 Number of DAC channels (#) 1 Interface type

2022-12-06 09:50:38

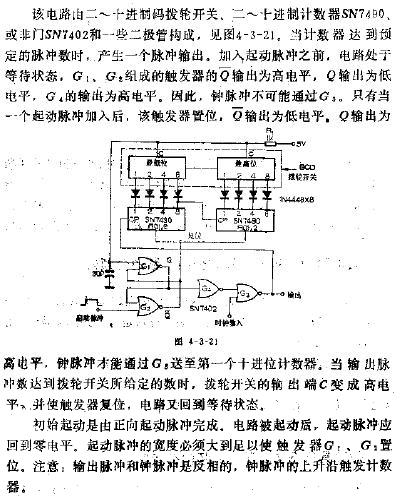

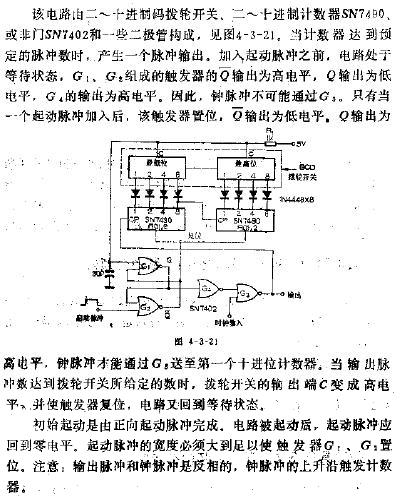

按預定脈沖數輸出脈沖的電路

2009-04-11 10:15:40 559

559

脈沖修復儀輸出波形真的是脈沖嗎?

要了解脈沖修復儀輸出的是什么波形,我們可以直截了當的對市面上所有的脈沖修復儀(器)的輸出做一個測試。

2009-11-17 10:08:53 2664

2664 分析機械式增量型編碼器的毛刺產生機理,結合編碼器有效旋轉波形和幾種毛刺波形的特點,提出一種新的去毛刺算法,在編碼器的相位超前輸出端的下降沿,判斷一次相位滯后端的輸

2011-09-07 14:59:54 80

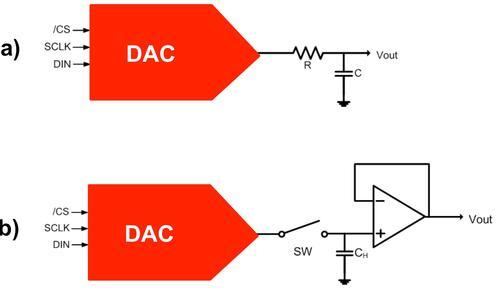

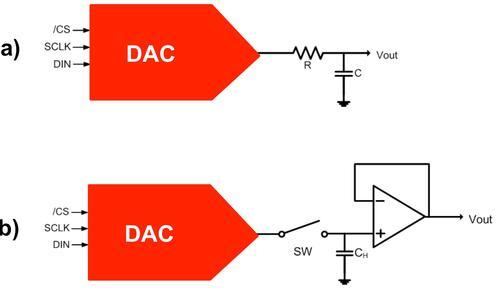

80 最簡單的DAC去干擾方法是在DAC 放大器輸出端 (VOUT) 使用一個 R/C 濾波器。這種濾波器可以降低干擾的振幅,但增加了建立時間。

2012-01-04 14:35:42 3934

3934

高重頻脈沖對脈沖多普勒雷達的干擾效應,下來看看

2016-12-26 17:18:36 5

5 機載脈沖多普勒(PD)雷達的抗干擾措施,下來看看

2016-12-26 17:20:23 15

15 脈沖多普勒雷達干擾技術研究,有需要的下來看看,

2016-12-24 23:21:48 22

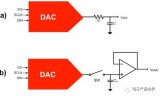

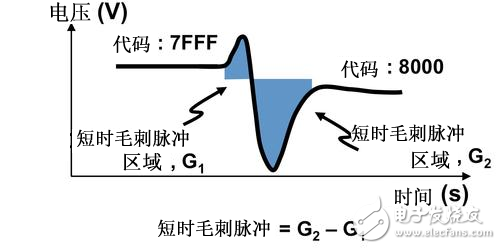

22 出現過沖與下沖(即干擾脈沖)也很平常。這些脈沖會以這兩種形式中的一種出現,如圖 1 所示。 圖 1:DAC 干擾行為 圖 1a 是一種可產生兩個代碼轉換誤差區的干擾,在 R-2R 高精度 DAC 中很常見。圖 1b 是單波瓣干擾脈沖,在電阻串 DAC 拓撲中較常見。干擾脈沖可通過能量測量

2017-04-18 05:28:13 345

345

在上一篇 DAC 基礎知識文中,我們對高精度數模轉換器 (DAC) 中的輸出干擾源進行了探討。若您希望在增加代碼的過程中獲得線性轉換,那么這些輸出脈沖可能會擾亂系統運行。讓我們快速回顧一下我在上篇博文中介紹的干擾脈沖情況:

2018-07-10 14:04:00 4445

4445

(DAC) 驅動電機驅動器,以控制電機旋轉。如果毛刺脈沖幅度高于電機驅動器的靈敏度閾值,當系統加電/斷電時,電機會在沒有任何方向控制的情況下旋轉。 圖1.經簡化的輸出級和加電毛刺脈沖 之前已經分析了高精度DAC經緩沖輸出

2017-11-14 14:20:15 1

1 干擾方面的表現卻有著顯著的不同。 我們可以在DAC以工作采樣率運行時觀察到其動態不是線性。造成動態非線性的原因很多,但是影響最大的是短時毛刺脈沖干擾、轉換率/穩定時間和采樣抖動。 用戶可以在DAC以穩定采樣率在其輸出范圍內運行時觀察短時毛刺脈沖干擾

2017-11-29 14:59:02 1340

1340

針對欺騙干擾信號常在時域、頻域和空域與真實信號重疊,導致識別欺騙干擾難度較大的問題,本文假定真實發射機與欺騙干擾機射頻前端器件除數模轉換器(DAC)外均工作于理想狀態,提出了一種基于DAC建模的欺騙

2017-12-26 19:02:00 0

0 最簡單的 DAC 去干擾方法是在 DAC 放大器輸出端 (VOUT) 使用一個 R/C 濾波器(圖 2 底部)。這種濾波器可以降低干擾的振幅,但增加了建立時間。

2018-03-13 16:29:00 2606

2606

STM32_DAC輸出電壓

2020-04-08 10:05:44 9599

9599

DAC101S101-Q1 – 10 位微功耗、RRO 數模轉換器DAC7551-Q1 – 汽車類 12 位超低毛刺脈沖電壓輸出數模轉換器DAC7551-Q1 器件是一款單通道電壓輸出數模轉換器(DAC),它具有優異的線性和單調性,并且采用一種專有架構 可以最大限度減小毛刺脈沖能量。

2020-03-15 20:12:00 934

934

的辦法是繞過去。昨天,在我減速通過一條討厭的減速帶時,突然想到了我的那個精密型16 位R-2R DAC。它在中間刻度時存在短時脈沖波形干擾問題(請參見圖1)。我想,在選擇使用具有較大短時脈沖波形干擾特性的DAC 時,可以在DAC 輸出端

2020-07-31 18:52:00 1

1 電子發燒友網為你提供DAC的短時毛刺脈沖干擾資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-13 08:44:06 11

11 電壓輸出DAC

2021-04-17 09:10:35 9

9 LTC1591/LTC1597:帶4象限電阻器的14位并行低毛刺乘法DAC數據表

2021-04-18 20:58:22 0

0 LTC1599:帶4象限電阻器的16位字節寬、低毛刺乘法DAC數據表

2021-05-20 09:38:24 2

2 測試線纜在課本中通常被認為是理想導體,但現實中如果忽略線纜的影響,往往會得到錯誤的測試結果。比如變頻器輸出電壓上的毛刺信號,可能就是線纜帶來的。 工程師在變頻器電機測試中偶然會發現電壓的PWM波形

2021-10-28 16:14:44 2012

2012 輸出脈沖可能會擾亂系統運行。讓我們快速回顧一下我在上篇博文中介紹的干擾脈沖情況:

DAC 輸出干擾的“能量”由脈沖(以綠色顯示)的寬度和高度定義。可根據系統要求對干擾的形狀進行很好的控制

2021-11-10 09:43:00 1326

1326

出現過沖與下沖(即干擾脈沖)也很平常。這些脈沖會以這兩種形式中的一種出現,如圖 1 所示。

圖?1:DAC 干擾行為

圖 1a 是一種可產生兩個代碼轉換誤差區的干擾,在?R-2R 高精度

2021-11-10 09:43:08 259

259

DAC輸出特定波形我所做的任務是用stm32F4的DAC輸出一段特定頻率和形狀的波。下面我將其分為幾個步驟。初始化配置DAC配置DMA寫入波形形狀初始化配置DAC首先查找到能夠作為DAC的串口

2021-11-22 19:06:02 27

27 原理:通過MCU控制開關K1通斷,產生尖脈沖疊加到電源上,電位器對脈沖幅度、波形進行調節。通過按鍵(S1/2/3)選擇輸出不同頻率,及占空比可調,使干擾測試更加靈活。這里的MCU用CPLD代替

2022-01-07 14:11:07 2

2 當DAC輸出模擬值發生變化時,在DAC輸出端觀察到動態現象,表現為毛刺,如圖1所示。該毛刺能量定義為電壓曲線下的面積與示波器上捕獲的時間圖的關系。該毛刺能量的單位是nV × s。

2022-12-15 11:53:04 1858

1858

在電源電壓超過±5V的R-2R DAC設計中,DAC的主要進位轉換期間可能會出現較大的電壓毛刺(高達1.5V)。這些毛刺會傳播到輸出緩沖放大器,并出現在輸出端。控制頂部 (VREF+) 和底部 (VREF-) 單刀雙擲開關(S0 至 SN)的電平轉換器的回轉會導致毛刺(圖 1)。

2023-02-24 17:10:06 1767

1767

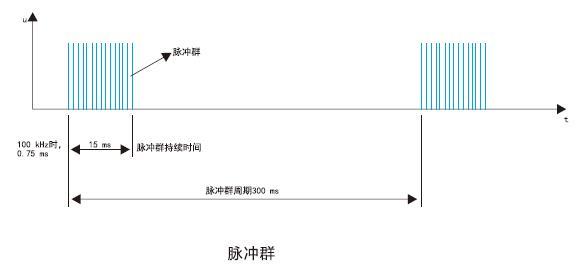

當電快速脈沖群測試時,有一個端口,如L.N和PE,PE和地球是兩個概念,電快速脈沖群干擾具有共模性質。

2023-11-21 14:13:05 578

578

什么是毛刺?毛刺的大小和方向 如何測量毛刺的尺寸?如何檢查已去除的毛刺? 毛刺是指由于加工工藝或其他原因產生的金屬表面上的不平整區域或小尖刺。毛刺通常形成于金屬的切削或沖壓過程中,可能會影響產品

2023-12-07 14:24:36 1284

1284 如何最小化毛刺尺寸?如何控制毛刺方向? 為了得到高質量的產品或工藝品,我們通常需要把毛刺的尺寸最小化,并控制其方向。毛刺會影響制品的外觀質量、功能性能以及使用壽命。本文將介紹毛刺的形成原因、影響因素

2023-12-07 14:24:39 213

213 沖裁加工時總是會產生毛刺,很難消除掉,因此,經常在加工后進行壓毛刺來消除毛刺。鑒于分型面的問題,最近使用去毛刺的方式有增加的趨勢.

2023-12-12 14:17:08 239

239

脈沖干擾的產生 脈沖干擾的解決方法? 脈沖干擾的產生 脈沖干擾是指在電路或系統中,因突然的電流或電壓變化而引起的暫時性干擾。這種干擾一般會導致電子設備的誤操作、數據丟失、系統崩潰等問題,嚴重的甚至

2024-01-05 14:31:34 1284

1284 在I2C的波形中,經常會發現有這樣的脈沖毛刺,會被認為是干擾或者器件不正常。

2024-03-02 09:33:54 405

405

電子發燒友App

電子發燒友App

評論