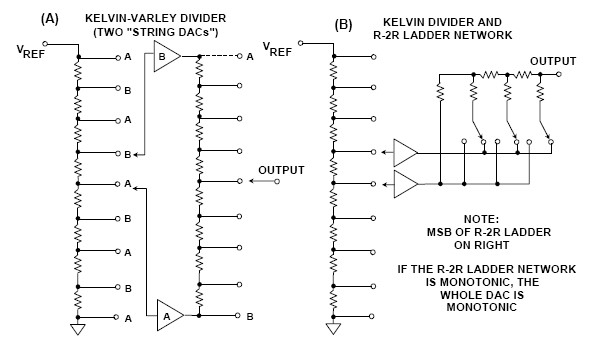

當(dāng)我們需要設(shè)計(jì)一個(gè)具有特定性能的DAC時(shí),很可能沒有任何一種架構(gòu)是理想的。這種情況下,可以將兩個(gè)或更多DAC組合成一個(gè)更高分辨率的DAC,以獲得所需的性能。這些DAC可以是同一類型,也可以是不同類型,各DAC的分辨率無(wú)需相同。

2022-08-01 09:27:00 1739

1739

較長(zhǎng)。轉(zhuǎn)換精度精度是指輸入端加有最大數(shù)值量時(shí),DAC 的實(shí)際輸出值和理論計(jì)算值之差,它主要包括非線性誤差、比例系統(tǒng)誤差、失調(diào)誤差。線性度理想的 D/A 轉(zhuǎn)換器是線性的,實(shí)際上是有誤差的。線性度是指數(shù)字量化

2021-03-29 06:06:30

作者:Kevin Duke德州儀器在上篇“追求完美”一文中,我介紹了理想 DAC 概念并概括了其重要性能規(guī)范。現(xiàn)在我們將深入探討實(shí)際器件與理想 DAC 傳輸函數(shù)的差異,以及如何量化這些差異。DAC

2018-09-18 14:18:36

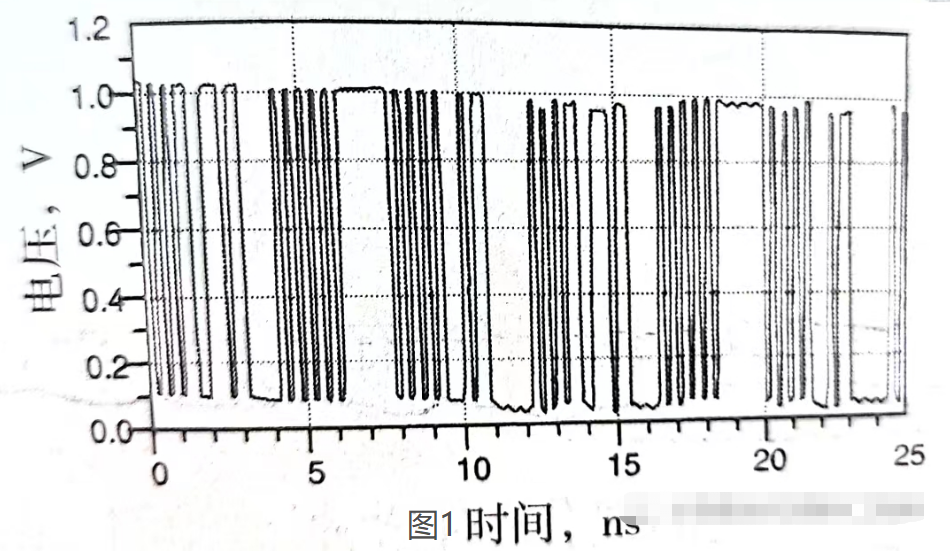

我現(xiàn)在用fpga掛4個(gè)DAC,其中三個(gè)DAC與fpga之間的布線(指的是數(shù)據(jù)傳輸線)長(zhǎng)度為100,另一個(gè)DAC與FPGA之間的布線長(zhǎng)度為400,問題:fpga同時(shí)給4路DAC發(fā)送數(shù)據(jù),在4路DAC的輸出端數(shù)據(jù)是同步輸出的嗎?

2017-04-21 08:57:04

設(shè)置 */ dac_output_voltage_set(voltage); delay_ms(300);}}-- void dac_init(void)函數(shù)代碼描述/*** @Briefdac

2022-03-28 20:12:31

這里介紹了有關(guān)《模擬線路》的 DAC 基礎(chǔ)知識(shí)系列博客文章。雖然我所認(rèn)識(shí)的大多數(shù) IC 設(shè)計(jì)人員都不敢想產(chǎn)品說明書的這種方法,但產(chǎn)品說明書的用途通常就是說明器件與理想模型的差異。例如,如果半導(dǎo)體

2022-11-23 07:49:08

理想電壓源的特點(diǎn)有哪些?理想電壓源與理想電流源有何區(qū)別?

2021-10-14 07:10:37

與理想輸出跨距之差。實(shí)際跨距為輸入設(shè)置為全1時(shí)與輸入設(shè)置為全0時(shí)的輸出之差。所有數(shù)據(jù)轉(zhuǎn)換器的滿幅增益誤差都與選擇用于測(cè)量增益誤差的基準(zhǔn)有關(guān)。 增益誤差A(yù)DC或DAC的增益誤差表示實(shí)際傳遞函數(shù)的斜率

2019-02-25 13:52:58

設(shè)置為全0時(shí)的輸出之差。所有數(shù)據(jù)轉(zhuǎn)換器的滿幅增益誤差都與選擇用于測(cè)量增益誤差的基準(zhǔn)有關(guān)。

增益誤差

ADC或DAC的增益誤差表示實(shí)際傳遞函數(shù)的斜率與理想傳遞函數(shù)的斜率的匹配程度。增益誤差通常

2023-12-18 07:08:34

時(shí)與輸入設(shè)置為全0時(shí)的輸出之差。所有數(shù)據(jù)轉(zhuǎn)換器的滿幅增益誤差都與選擇用于測(cè)量增益誤差的基準(zhǔn)有關(guān)。 增益誤差 ADC或DAC的增益誤差表示實(shí)際傳遞函數(shù)的斜率與理想傳遞函數(shù)的斜率的匹配程度。增益誤差通常表示為

2018-10-17 09:44:40

代碼,4位轉(zhuǎn)換器 雙極性代碼(4位轉(zhuǎn)換器) 最低有效位(LSB)的大小 實(shí)際應(yīng)用對(duì)數(shù)據(jù)轉(zhuǎn)換器分辨率的要求 理想3位DAC和ADC的傳遞函數(shù) 數(shù)據(jù)轉(zhuǎn)換器的主要誤差(直流參數(shù)) 數(shù)據(jù)轉(zhuǎn)換器的主要誤差

2018-10-26 09:34:36

DAC1對(duì)應(yīng)的DMA及通道是DMA2的通道3,其中BufferSize的大小根據(jù)每次需要傳輸的數(shù)據(jù)數(shù)量來定,一般是輸出波形一個(gè)周期的采樣點(diǎn)數(shù),該點(diǎn)數(shù)越大波形越平滑。DMA的模式配置為循環(huán)模式,當(dāng)DMA傳輸

2023-04-24 16:55:02

請(qǐng)問各位,EFT共模干擾能否量化?能否通過什么表示出來,經(jīng)過濾波電路后抑制了多少,能夠量化出來?

2014-06-19 13:27:43

一、int8的輸出和fp32模型輸出差異比較大

解決方案:

檢查前后處理是否有問題,int8網(wǎng)絡(luò)輸入輸出一般需要做scale處理,看看是否遺漏?

通過量化可視化工具分析int8的輸出和fp32

2023-09-19 06:09:33

向量指令。

編譯器可以從dspfns.h頭文件向量化常規(guī)的C和C++操作,如+和一些ITU內(nèi)部函數(shù)。

作為編譯器矢量化的替代方案,RVCT還支持將霓虹燈內(nèi)部函數(shù)作為矢量化編譯器和編寫匯編器代碼之間的SIMD代碼生成的中間步驟。

有關(guān)詳細(xì)信息,請(qǐng)參閱《RVCT編譯器參考指南》中的附錄E使用霓虹燈支持

2023-08-12 06:22:28

STM32F103的DAC功能任務(wù)一任務(wù)2總結(jié)任務(wù)一輸出一個(gè)周期2khz的正弦波(循環(huán))。此波形驅(qū)動(dòng)作用至蜂鳴器或喇叭,會(huì)呈現(xiàn)一個(gè)“滴…”的單音1.新建2.生成基本音色3.導(dǎo)出任務(wù)2將一段

2021-08-09 06:23:21

有人可以協(xié)助并闡明如何為 DAC 配置 GPDMA 以將回調(diào)函數(shù) HAL_DAC_ConvCpltCallbackCh1(DAC_HandleTypeDef* hdac

2023-02-09 09:46:29

本文目的是以串口通信來簡(jiǎn)要分析STM32使用標(biāo)準(zhǔn)庫(kù)函數(shù)和HAL庫(kù)函數(shù)編程的差異。目錄(一)開發(fā)方式1.配置寄存器2.庫(kù)函數(shù)3.HAL庫(kù)(二)庫(kù)函數(shù)與HAL庫(kù)對(duì)比1.串口通信實(shí)驗(yàn)2.庫(kù)函數(shù)與HAL庫(kù)

2021-08-11 07:40:36

:控制器對(duì)TLC5620的單個(gè)DAC設(shè)置包括兩個(gè)主要操作1.將數(shù)字量化值以及控制位發(fā)送到TLC5620中對(duì)應(yīng)的寄存器中2.控制DAC將寄存器中接收到的數(shù)據(jù)值更新到DAC輸出上 對(duì)于數(shù)據(jù)的傳輸,有連續(xù)傳輸

2019-01-29 03:12:43

大家好波DAC組件對(duì)我來說非常有趣。有可能使這個(gè)組件有點(diǎn)莫名其妙嗎?(如Add、Mulk、FM、AM、RM—這是音頻合成的理想選擇)卡米爾 以上來自于百度翻譯 以下為原文Hi all Wave

2019-05-15 10:26:15

最近需要寫個(gè)c6748用spi傳輸16位的數(shù)據(jù),根據(jù)創(chuàng)龍?zhí)峁┑腟PI_DAC_AD5724V2例程里的SpiTransfer函數(shù)修改了自己的函數(shù)。因?yàn)樵?b class="flag-6" style="color: red">函數(shù)是傳輸8位,我想改成一個(gè)帶變量的可以傳輸

2019-09-06 13:33:29

理想電流源其輸出電流總能保持定值或一定的時(shí)間函數(shù),其值與它的兩端電壓u 無(wú)關(guān)的元件叫理想電流源。電路符號(hào)理想電流源的電壓、電流關(guān)系1、電流源的輸出電流由電源本身決定,與外電路無(wú)關(guān);與它兩端電壓方向、大小無(wú)關(guān)。2、電流源兩端的電壓由電源及外電路共同決定。...

2021-12-31 07:06:54

在使用浩辰CAD制圖軟件進(jìn)行繪圖的過程中,經(jīng)常需要進(jìn)行CAD矢量化操作,可能有些小伙伴不是很清楚什么是CAD矢量化,接下來給大家詳細(xì)介紹一下吧!CAD矢量化是什么意思?矢量化的意思就是將那些原本用色

2020-03-06 17:02:29

我現(xiàn)在所看的程序是6670的bcp_lte_ul程序。

但是我想確定一下,在BCP中除了rms變量之外,還有別的變量也是和數(shù)據(jù)的量化有關(guān)的么?

或者有沒有什么變量可以像FFTC一樣通過移位來實(shí)現(xiàn)數(shù)據(jù)的定點(diǎn)量化?

2018-06-21 06:09:05

輸入9個(gè),一個(gè)符號(hào)位,為什么量化后要乘以2^8,還有為什么要量化,未量化是小數(shù),量化后成整數(shù),這樣濾波后的幅值是不是要變大256倍。謝謝

2014-02-25 10:30:15

可以使用已有的量化表(比如 TensorRT 量化后得到的量化表)作為輸入 來完成BModel模型的量化嗎?

2023-09-19 06:04:43

Arduino IDE開發(fā)的優(yōu)點(diǎn)是什么?安裝Arduino IDE及程序目的是什么?基于標(biāo)準(zhǔn)庫(kù)函數(shù)與基于HAL庫(kù)函數(shù)的stm32編程方式有何差異?

2021-12-06 07:17:54

以實(shí)例程序(串口通信),分析基于標(biāo)準(zhǔn)庫(kù)函數(shù)與基于HAL庫(kù)函數(shù)的stm32編程方式的差異一、基于標(biāo)準(zhǔn)庫(kù)函數(shù)的stm32編程方式二、基于HAL庫(kù)函數(shù)的stm32編程方式差異三、stdunio IDE試玩

2022-02-22 06:33:13

大家好,我知道通過DMA傳輸數(shù)據(jù)的概念。但我仍然困惑,如何將一個(gè)8位數(shù)據(jù)傳送到DAC,例如:1。我對(duì)我的ADC實(shí)際數(shù)據(jù)進(jìn)行了一些計(jì)算(例如過采樣),并將其保存成變量x。ADC數(shù)據(jù)=ADCJSTART

2019-10-15 07:52:59

有這些應(yīng)用,但在模數(shù)轉(zhuǎn)換系統(tǒng)中我們需要噪聲來提高電路性能。這種信號(hào)處理技術(shù),稱為抖動(dòng),故意將具有適當(dāng) PDF(概率密度函數(shù))和 PSD(功率譜密度)的噪聲信號(hào)添加到 ADC(模數(shù)轉(zhuǎn)換器)輸入(采樣和量化

2022-12-22 15:17:41

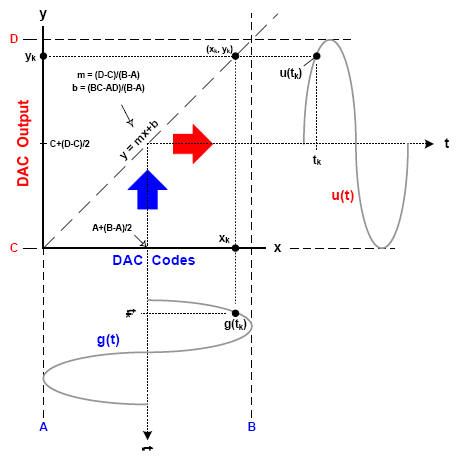

的DAC,可以在預(yù)定義范圍內(nèi)精確設(shè)置輸出電流,而無(wú)需任何額外的外部元器件。DAC轉(zhuǎn)換函數(shù)理論和內(nèi)部誤差理想數(shù)模轉(zhuǎn)換器產(chǎn)生的模擬輸出電壓或電流與輸入數(shù)字碼嚴(yán)格成比例,而與電源和基準(zhǔn)電壓變化等干擾性外部

2021-12-30 08:00:00

嗨我使用帶有ML523板的virtex 5 xc5vlx110t。我使用VHDL編碼,其輸出數(shù)據(jù)類型是std_logic。我想連接DAC傳輸模擬信號(hào)。我可以使用任何DAC嗎?或者只能使用特定的DAC嗎?我有MAX5216評(píng)估套件+,我不知道如何連接ML523和這個(gè)DAC。謝謝

2020-07-08 06:08:29

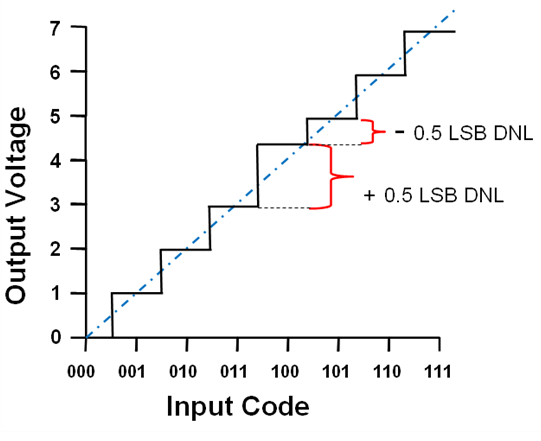

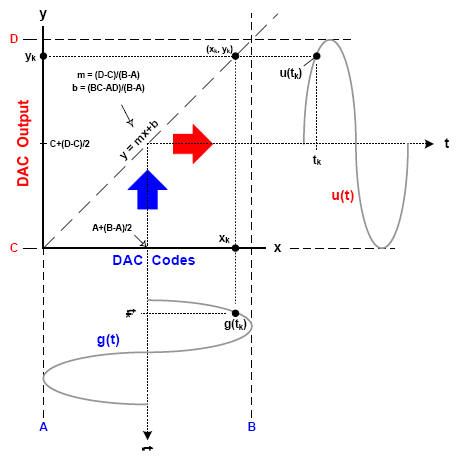

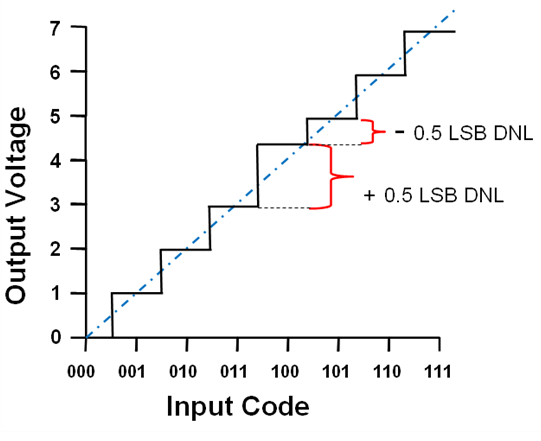

現(xiàn)在我們將深入探討實(shí)際器件與理想 DAC 傳輸函數(shù)的差異,以及如何量化這些差異。DAC 規(guī)范分為兩個(gè)基本類別:靜態(tài)與動(dòng)態(tài)。靜態(tài)規(guī)范是在穩(wěn)定輸出狀態(tài)下、在 DAC 輸出端觀察到的行為,而動(dòng)態(tài)規(guī)范則是

2022-11-23 07:46:26

在GUI中如何實(shí)現(xiàn)均勻量化和非均勻量化,可以達(dá)到等距輸入?yún)?shù)得到相應(yīng)變化,謝謝幫助,最好給個(gè)程序

2016-05-26 18:23:23

我使用PIC32 MZ2048 ECH,我想通過PacketSender(UDP/IP)傳輸我正在接收的數(shù)據(jù)。我想通過SPI發(fā)送一個(gè)正弦信號(hào)到DAC8911。為此,我已經(jīng)配置了MICI,SCLK

2020-04-13 09:39:11

目前需要做一款電源需要使用到DAC模塊但是我現(xiàn)在在想是使用MSP430F2616這款單片機(jī)的內(nèi)置DAC模塊還是使用外置的DAC芯片來控制,我之所以這么想是因?yàn)樾枰紤]內(nèi)置DAC模塊和外置DAC模塊

2015-11-20 21:43:44

標(biāo)量化(余弦信號(hào)數(shù)據(jù)的標(biāo)量化)

2009-10-11 09:04:22

量化算法具有什么特點(diǎn)?模型量化會(huì)帶來哪些好處?

2021-09-28 06:32:07

和 LTC2662,是一種新類別的DAC,可以在預(yù)定義范圍內(nèi)精確設(shè)置輸出電流,而無(wú)需任何額外的外部元器件。DAC轉(zhuǎn)換函數(shù)理論和內(nèi)部誤差 理想數(shù)模轉(zhuǎn)換器產(chǎn)生的模擬輸出電壓或電流與輸入數(shù)字碼嚴(yán)格成比例,而與電源和基準(zhǔn)

2021-06-19 10:45:02

stm32下標(biāo)準(zhǔn)庫(kù)函數(shù)與HAL庫(kù)函數(shù)編程方式的差異標(biāo)準(zhǔn)庫(kù)函數(shù)HAL庫(kù)函數(shù)標(biāo)準(zhǔn)庫(kù)函數(shù)與HAL庫(kù)函數(shù)代碼對(duì)比總結(jié)標(biāo)準(zhǔn)庫(kù)函數(shù)由于寄存器開發(fā)難度很大,因此ST公司就專門編寫了芯片的庫(kù)函數(shù)(固件庫(kù)),將一些

2022-02-14 06:03:50

你好。我用PIC16F1788來設(shè)計(jì),并使用DAC函數(shù)。我的問題是有多少DAC在那里!在數(shù)據(jù)表表1.0設(shè)備總覽中表明它只有一個(gè)8位DAC。但是在其他地方,例如PIN分配表-表1(28引腳)顯示了其他3×5位DAC,它也在第3頁(yè)的“FAMILY TYPE”表中顯示。誰(shuí)能確認(rèn)/澄清?感謝羅伯特

2020-05-15 07:24:04

目錄參考資料本文內(nèi)容:用 STM32F103 的 DAC 功能完成以下波形輸出,用示波器觀察波形,并用蜂鳴器或手機(jī)耳機(jī)收聽輸出聲音效果、感受歌曲的音質(zhì)差異。1)輸出一個(gè)周期 2khz 的正弦波(循環(huán)

2021-08-09 07:18:20

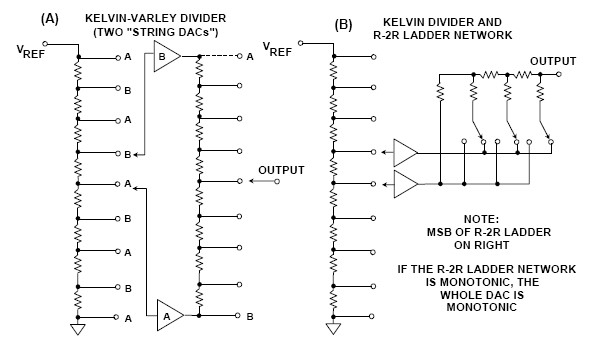

。最簡(jiǎn)單的電阻串 DAC 只是一系列相同尺寸的電阻器和每個(gè)電阻器之間的接點(diǎn)。適當(dāng)?shù)慕狱c(diǎn)可根據(jù)應(yīng)用于 DAC 的數(shù)字代碼切換至輸出緩沖器。這種有限開關(guān)活動(dòng)可產(chǎn)生極低的干擾能量。在理想情況下,每個(gè)電阻器

2022-11-23 07:01:05

`100G以太網(wǎng)憑借著更高傳輸速率、更高密度、更低設(shè)備功耗的趨勢(shì)成為了市場(chǎng)的寵兒,而100G光模塊、100G AOC和100G DAC更是其中的重要組成部分。現(xiàn)在市場(chǎng)上出現(xiàn)了各種各樣的100G光模塊

2018-02-06 14:33:51

`由【鶴壁煤矸石發(fā)熱量檢測(cè)儀】提供的大卡機(jī):***磚坯熱量化驗(yàn)設(shè)備,爐渣熱量化驗(yàn)儀,測(cè)試煤熱值的儀器,檢測(cè)煤炭發(fā)熱量的設(shè)備,磚廠熱值化驗(yàn)設(shè)備,磚廠熱值檢測(cè)儀器,煤矸石熱量化驗(yàn)設(shè)備,煤矸石熱卡機(jī),煤炭大卡檢測(cè)機(jī),煤炭熱卡儀`

2019-04-24 08:49:04

請(qǐng)問,要搭一個(gè)傳輸鏈路,鏈路中的ADC和DAC的參數(shù),比如:采樣率和分辨率一定要一樣嗎?

中頻模擬信號(hào),先模數(shù)轉(zhuǎn)換數(shù)字化進(jìn)行傳輸,之后需要數(shù)模轉(zhuǎn)換,前后的ADC和DAC采樣率和位數(shù)是否要完全相等?完全符合指標(biāo)的器件不太好找。

2023-12-12 06:21:04

個(gè)數(shù)值。對(duì)于一個(gè)理想ADC來說,傳遞函數(shù)是一個(gè)步寬等于分辨率的階梯。然而,在具有較高分辨率的系統(tǒng)中(≥16位),傳輸函數(shù)的響應(yīng)將相對(duì)于理想響應(yīng)有一個(gè)較大的偏離。這是因?yàn)锳DC以及驅(qū)動(dòng)器電路導(dǎo)致的噪聲會(huì)

2023-12-20 06:55:22

值。對(duì)于一個(gè)理想ADC來說,傳遞函數(shù)是一個(gè)步寬等于分辨率的階梯。然而,在具有較高分辨率的系統(tǒng)中(≥16位),傳輸函數(shù)的響應(yīng)將相對(duì)于理想響應(yīng)有一個(gè)較大的偏離。這是因?yàn)锳DC以及驅(qū)動(dòng)器電路導(dǎo)致的噪聲會(huì)降低

2018-10-01 13:20:15

本文描述了兩種時(shí)下最流行的方法來改善實(shí)際ADC應(yīng)用中的量化噪聲性能:過采樣和高頻抖動(dòng)。

2021-04-20 06:55:55

量化的功能有哪些?量化的算法是什么?怎樣用Verilog語(yǔ)言實(shí)現(xiàn)H.264的量化?如何運(yùn)用Modelsim對(duì)H.264進(jìn)行仿真?

2021-04-28 06:12:51

乘法 DAC 是波形發(fā)生應(yīng)用的理想構(gòu)建模塊。因?yàn)槌朔〝?shù)模轉(zhuǎn)換器 (DAC) 的 R-2R 架構(gòu)非常適合低噪聲、低毛刺、快速建立的應(yīng)用。從固定參考輸入電壓產(chǎn)生波形時(shí),必須考慮一些重要的交流規(guī)格,包括建立時(shí)間、中間電平毛刺和數(shù)字 SFDR。今天我們就來分析下這些與波形發(fā)生相關(guān)的重要 DAC 規(guī)格。

2019-07-18 08:17:48

提出一個(gè)新的自適應(yīng)動(dòng)態(tài)信任關(guān)系量化模型。該模型在建立基于歷史函數(shù)的直接信任計(jì)算方法和基于路徑函數(shù)的反饋信任聚合模型的基礎(chǔ)上,引入自信因子和反饋因子來自動(dòng)建立和

2009-04-09 08:40:00 12

12 ADC和DAC的靜態(tài)傳輸函數(shù)和DC誤差:對(duì)于DAC和ADC這兩者來說,最重要的是記住輸入或輸出都是數(shù)字信號(hào),所以,信號(hào)是被量化的。也就是說,N比特字代表2的N次方個(gè)可能狀態(tài)之一,因此

2009-09-28 14:25:20 12

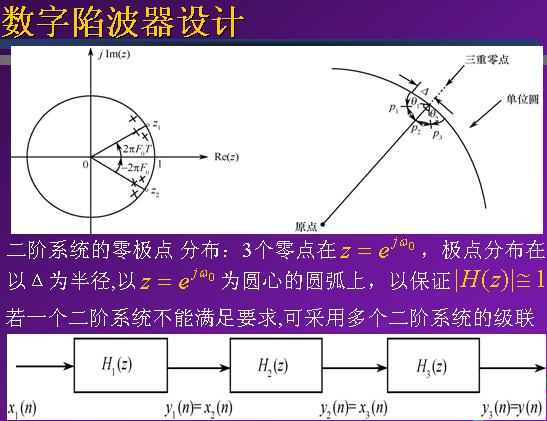

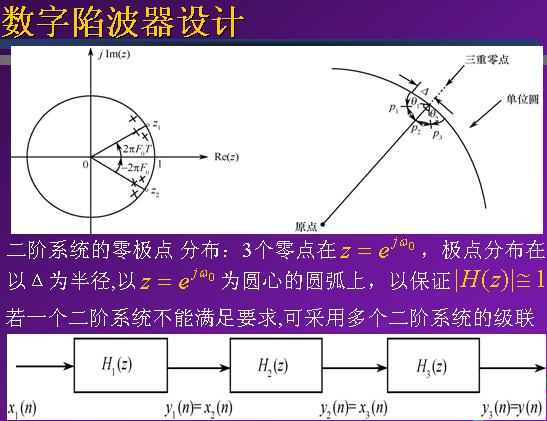

12 二階數(shù)字陷波器的設(shè)計(jì)方法及數(shù)字傳輸函數(shù)

下面講解設(shè)計(jì)一個(gè)二階數(shù)字陷波器(求數(shù)字傳輸函數(shù)),其模擬陷波頻率為60Hz,3dB帶寬為6Hz,

2008-08-01 17:24:28 10529

10529

什么是理想傳輸時(shí)間(ITT)

理想傳輸時(shí)間(ITT: Ideal Transmission Time)理想傳輸時(shí)間(ITT)是一個(gè)當(dāng)ATM可用比特率(ABR)CLP=0時(shí)的信元傳輸時(shí)間,

2008-11-27 08:46:43 765

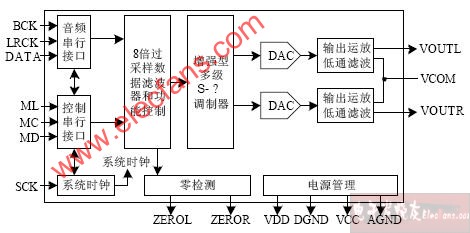

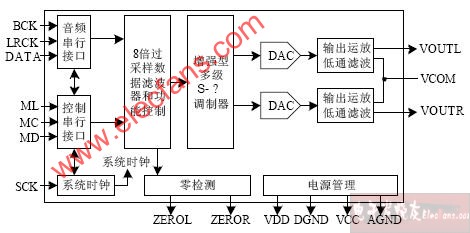

765 音頻DAC的工作原理

高分辨率音頻DAC 大都采用多級(jí)幅度量化高階Σ - Δ調(diào)制器結(jié)構(gòu)。這樣,在實(shí)際應(yīng)用中可以提高音頻動(dòng)態(tài)范圍,減小

2009-03-06 11:33:56 9249

9249

有源濾波器按傳輸函數(shù)的極、零點(diǎn)分類

全極點(diǎn)型濾波器

以上介紹的巴特沃斯、切比雪夫、貝塞爾等三種濾波器,它們的共同

2010-05-19 11:43:27 1542

1542 二階有源濾波器的傳輸函數(shù)

在有源濾波器的設(shè)計(jì)中,高階濾波器的傳輸函數(shù)都可以分解成一階和多個(gè)二階傳輸函數(shù)的乘積。一階傳輸函數(shù)比較簡(jiǎn)單,二階函

2010-05-23 10:31:24 18908

18908

本文將重點(diǎn)討論靜態(tài)特性,并闡述一種由輸出頻譜中觀察到的諧波成分導(dǎo)出DAC傳遞函數(shù)的方法。分析中假設(shè),傳遞函數(shù)而非瞬態(tài)輸出特性是所觀察到的諧波失真的主要來源。

2011-05-25 10:07:16 3150

3150

雙曲線函數(shù)發(fā)生電路電路采用了數(shù)/模轉(zhuǎn)換器DAC-20EX和運(yùn)放OP17G,雙曲線函數(shù)發(fā)生電路如圖所示。

2011-10-13 10:50:16 1023

1023

本文研究了離散T-S模糊系統(tǒng)H∞量化濾波問題。主要目的是針對(duì)存在量化的T-S模糊反饋系統(tǒng)設(shè)計(jì)可行的濾波器算法使其在消除量化的影響下漸進(jìn)穩(wěn)定的并滿足給定H∞性能指標(biāo)。具體是通過模糊Lyapunov函數(shù)

2015-12-18 16:03:05 12

12 組技術(shù)規(guī)格。 圖1 雖然這3個(gè)DAC拓?fù)浠ゲ幌嗤鼈兊募夹g(shù)規(guī)格與電氣描述非常類似。 一個(gè)主要的靜態(tài)DAC技術(shù)規(guī)格就是理想轉(zhuǎn)換函數(shù)(圖2)。在對(duì)這個(gè)普通轉(zhuǎn)換函數(shù)的圖示中,可以輕松地體會(huì)和理解零代碼、偏移、滿量程以及增益的定義。一旦你理解了上述概念,

2017-11-14 11:10:39 1

1 當(dāng)前面向單指令多數(shù)據(jù)( SIMD)擴(kuò)展部件的兩類向量化方法分別是循環(huán)級(jí)向量化方法和超字級(jí)并行(SLP)方法。針對(duì)當(dāng)前編譯器不能實(shí)現(xiàn)函數(shù)級(jí)向量化的問題,提出一種基于靜態(tài)單賦值的函數(shù)級(jí)向量化方法。該方法

2017-11-29 16:08:07 0

0 基于有限量化信息通信的切換網(wǎng)絡(luò)分布式量化次梯度優(yōu)化算法。在非平衡切換網(wǎng)絡(luò)中,通過設(shè)計(jì)具有有限量化水平的一致量化器使所有信息在發(fā)送之前都經(jīng)過量化,利用非二次李雅普諾夫函數(shù)方法,證明了所提出的多個(gè)體分布式量化

2018-03-29 10:44:25 0

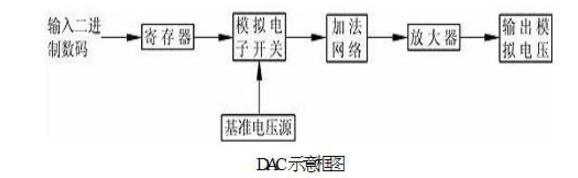

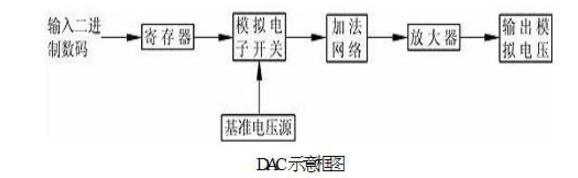

0 本文首先介紹了數(shù)模轉(zhuǎn)換器(DAC)原理,其次介紹了集成電路數(shù)模轉(zhuǎn)換器的原理及作用與二進(jìn)制數(shù)模轉(zhuǎn)換器電路圖,最后介紹了理想數(shù)模轉(zhuǎn)換器 (DAC) 的重要屬性。

2018-04-20 12:39:49 16585

16585

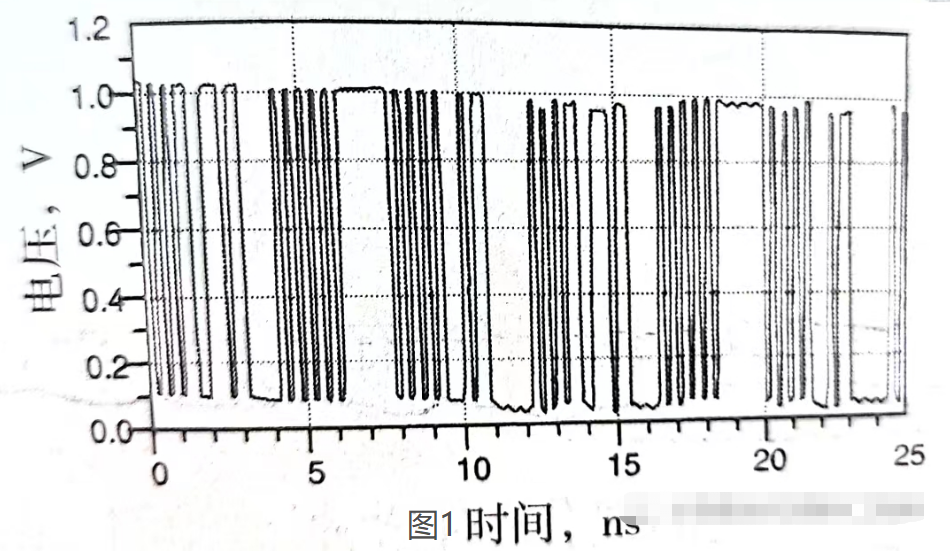

由于數(shù)據(jù)傳輸的差異,測(cè)試pattern生成的眼圖并不一定會(huì)是從一個(gè)完整的眼圖起始。因此,如果采用第一個(gè)眼圖來進(jìn)行校準(zhǔn),可能會(huì)出現(xiàn)所有LVDS數(shù)據(jù)輸出差分對(duì)得窗口不相一致。所以,第二個(gè)眼圖窗口將會(huì)是建議的首選,該眼圖必然是完整的采樣窗口。

2018-07-05 15:25:08 4895

4895 DAC 規(guī)范分為兩個(gè)基本類別:靜態(tài)與動(dòng)態(tài)。 靜態(tài)規(guī)范 是在穩(wěn)定輸出狀態(tài)下、在 DAC 輸出端觀察到的行為,而 動(dòng)態(tài)規(guī)范 則是指在代碼至代碼轉(zhuǎn)換過程中所觀察到的行為。在討論線性度與 DAC 傳輸函數(shù)

2018-07-26 09:56:14 6270

6270

DAC傳輸函數(shù)的端點(diǎn)及其如何偏離預(yù)期

2018-08-22 01:47:00 2507

2507 本文檔的主要內(nèi)容詳細(xì)介紹的是stm32f10x標(biāo)準(zhǔn)外設(shè)庫(kù)之DAC的固件函數(shù)詳細(xì)資料免費(fèi)下載 主要的功能有:還原DAC外設(shè)寄存器到默認(rèn)復(fù)位值,依照DAC_InitStruct指定的參數(shù)初始化DAC

2018-08-28 17:02:08 8

8 5G毫米波傳輸鏈路預(yù)算與4G的關(guān)鍵差異

2020-07-08 10:09:25 2181

2181 定義數(shù)據(jù)轉(zhuǎn)換器線性精度主要有兩個(gè)參數(shù):積分(INL)和差分(DNL)非線性。INL 是輸出傳輸函數(shù)和理想直線之間的偏差;DNL 是轉(zhuǎn)換器輸出步長(zhǎng)相對(duì)于理想步長(zhǎng)的誤差。可以采用兩種方法之一對(duì) INL

2020-12-28 06:15:00 6

6 的數(shù)據(jù)清洗方法,會(huì)讓你的能力調(diào)高100倍。 本文基于此, 講述pandas中超級(jí)好用的str矢量化字符串函數(shù) ,學(xué)了之后,瞬間感覺自己的數(shù)據(jù)清洗能力提高了。 ? 1個(gè)數(shù)據(jù)集,16個(gè)Pandas函數(shù) 數(shù)據(jù)集是黃同學(xué)精心為大家編造 ,只為了幫助大家學(xué)習(xí)到知

2021-04-13 10:37:43 2252

2252

電子發(fā)燒友網(wǎng)為你提供DAC傳遞函數(shù)資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-27 08:42:41 3

3 一般來講AOC有源光纜和DAC高速線纜有以下幾種區(qū)別: ①功耗不同:AOC有源光纜的功耗比DAC的功耗高; ②傳輸距離不同:理論上AOC最遠(yuǎn)傳輸距離可達(dá)300M,DAC最遠(yuǎn)傳輸距離為7M; ③傳輸

2021-05-13 17:14:35 1359

1359 AD7112:具有抗對(duì)數(shù)傳輸功能的雙CMOS乘法DAC,用于音量控制應(yīng)用產(chǎn)品手冊(cè)

2021-05-10 10:54:17 5

5 ADL6317:與射頻DAC和收發(fā)器配合使用的傳輸VGA數(shù)據(jù)表

2021-05-16 10:23:52 8

8 了解R2R和電阻串DAC架構(gòu)之間的差異(電源技術(shù)培訓(xùn)機(jī)構(gòu))-數(shù)模轉(zhuǎn)換器均采用兩種基本架構(gòu),您對(duì)其特性的了解將有助于為應(yīng)用選擇正確的轉(zhuǎn)換器架構(gòu)。由于大多數(shù)工程師都在工程類院校專門學(xué)習(xí)過有關(guān)模數(shù)轉(zhuǎn)換器

2021-09-17 13:21:45 4

4 作者:Kevin Duke? 德州儀器

在上篇“追求完美”一文中,我介紹了理想 DAC 概念并概括了其重要性能規(guī)范。現(xiàn)在我們將深入探討實(shí)際器件與理想 DAC 傳輸函數(shù)的差異,以及如何量化這些

2021-11-10 09:43:36 361

361

輸入阻抗等)。問題是沒有這么簡(jiǎn)單。

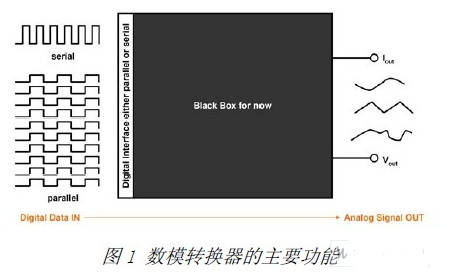

作為該系列博客文章的開始,Tony?和我想首先簡(jiǎn)單介紹一下理想數(shù)模轉(zhuǎn)換器 (DAC) 的屬性,然后再深入討論更為復(fù)雜的規(guī)范。下圖是理想 DAC 的傳遞函數(shù),重點(diǎn)

2021-11-10 09:43:39 494

494

stm32下標(biāo)準(zhǔn)庫(kù)函數(shù)與HAL庫(kù)函數(shù)編程方式的差異標(biāo)準(zhǔn)庫(kù)函數(shù)HAL庫(kù)函數(shù)標(biāo)準(zhǔn)庫(kù)函數(shù)與HAL庫(kù)函數(shù)代碼對(duì)比總結(jié)標(biāo)準(zhǔn)庫(kù)函數(shù)由于寄存器開發(fā)難度很大,因此ST公司就專門編寫了芯片的庫(kù)函數(shù)(固件庫(kù)),將一些

2021-12-09 14:21:06 15

15 以實(shí)例程序(串口通信),分析基于標(biāo)準(zhǔn)庫(kù)函數(shù)與基于HAL庫(kù)函數(shù)的stm32編程方式的差異一、基于標(biāo)準(zhǔn)庫(kù)函數(shù)的stm32編程方式二、基于HAL庫(kù)函數(shù)的stm32編程方式差異三、stdunio IDE試玩

2021-12-28 19:09:14 27

27 所有DAC都表現(xiàn)出一定程度的諧波失真,這是當(dāng)DAC的輸入由代表理想均勻采樣正弦波的數(shù)字序列驅(qū)動(dòng)時(shí),DAC在其輸出端再現(xiàn)完美正弦波的程度的指標(biāo)。由于DAC的非理想瞬態(tài)和靜態(tài)行為,輸出頻譜將包含諧波成分。

2023-02-01 15:46:44 832

832

精度計(jì)算器(ACCU)有助于數(shù)據(jù)轉(zhuǎn)換器應(yīng)用電路的設(shè)計(jì)和分析。它計(jì)算理想數(shù)據(jù)轉(zhuǎn)換器的直流精度,涵蓋模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)。數(shù)據(jù)轉(zhuǎn)換器的直流精度是與理想線性傳遞函數(shù)的最大偏差的量度

2023-02-07 14:36:57 697

697

,其電平低于轉(zhuǎn)換器的滿量程(FS)電平,通常為0.5dB至1dB。ADC使用非線性過程將信號(hào)轉(zhuǎn)換為離散輸出電平。最小的離散步長(zhǎng)稱為量化電平,它是ADC分辨率或位數(shù)的函數(shù)。實(shí)際正弦波值與量化電平之間存在差異(或誤差)。誤差可以是量化電平內(nèi)的任何值,從而產(chǎn)生理想轉(zhuǎn)換器的表達(dá)式

2023-02-25 11:05:22 962

962

之前的文章都在講理想傳輸線對(duì)單一信號(hào)的影響。本主題(有損傳輸線)收集關(guān)于非理想傳輸線對(duì)信號(hào)的影響。把非理想傳輸線稱為有損線。

2023-04-23 12:57:19 1275

1275

一個(gè)理想系統(tǒng)是從功率源100%地將能量傳送到負(fù)載,這需要信號(hào)源阻抗、傳輸線及其它連接器的特征阻抗與負(fù)載阻抗精確匹配。由于理想的傳輸過程不存在干擾,信號(hào)交流電壓在傳輸線兩端保持相同。

2023-06-03 09:15:16 360

360

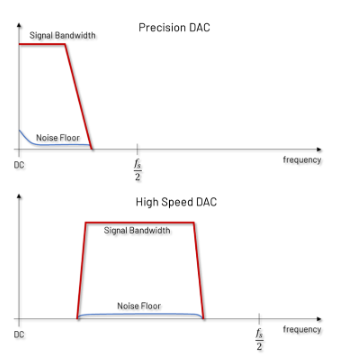

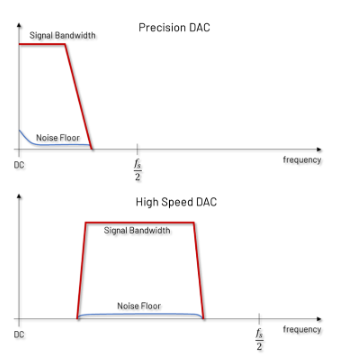

直流精度是高速DAC和快速精密DAC之間的主要區(qū)別。通常很難解釋這種差異的原因和影響,而且當(dāng)兩種類型的DAC提供相同的分辨率和相同的線性度時(shí)。甚至令人失望的是,快速精密DAC在更新速率方面僅觸及了高速DAC的下限。本博客介紹并分析了這兩種類型的DAC的異同。

2023-06-27 14:32:36 751

751

免費(fèi)音頻傳輸函數(shù)分析

2023-07-31 17:10:23 0

0 10GDAC是一種基于銅纜的高速連接線纜,支持10G以太網(wǎng)標(biāo)準(zhǔn),適用于短距離高速數(shù)據(jù)傳輸。DAC SFP-10G-CU是其中一種高速直連電纜以太網(wǎng)交互連接解決方案,具有高性能、低功耗、使用便捷等特點(diǎn),廣泛應(yīng)用于數(shù)據(jù)中心、企業(yè)網(wǎng)絡(luò)、云計(jì)算和虛擬化環(huán)境、高性能計(jì)算等領(lǐng)域。

2023-12-18 11:50:19 310

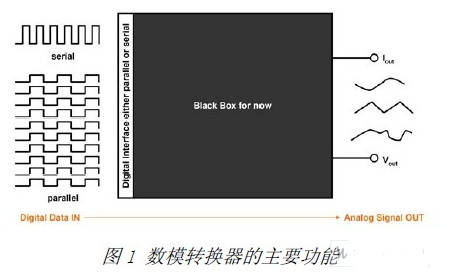

310 同樣,對(duì)于大多數(shù)人來說,DAC 只不過是一個(gè)輸入端為數(shù)字信號(hào)數(shù)據(jù)而輸出端為模擬信號(hào)數(shù)據(jù)的“黑匣子”。只有為數(shù)不多的人知道其在架構(gòu)方面的區(qū)別,以及與 R2R 梯形架構(gòu)相比一個(gè)電阻串架構(gòu)所具有的優(yōu)點(diǎn)和缺點(diǎn)。了解他們之間的不同之處并了解這些通用 DAC 的工作原理可以使設(shè)計(jì)人員為其應(yīng)用選擇的 DAC。

2024-02-15 16:45:00 113

113

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論