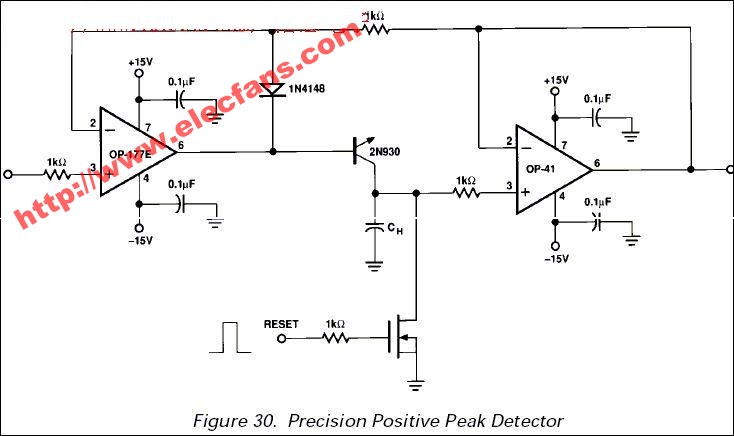

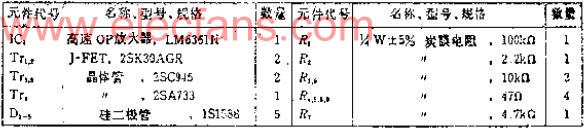

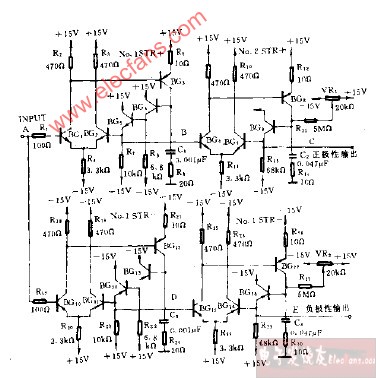

本文主要介紹了基于運放CA3140的峰值檢測電路的設計。本次電路的設計,可以較為精確的完成對峰值信號脈沖的檢測與保持,從而完成對脈沖幅度的測量,進而知道輻射的能量大小。主要解決了以下問題:由于此電路

2018-02-27 08:51:09 17775

17775

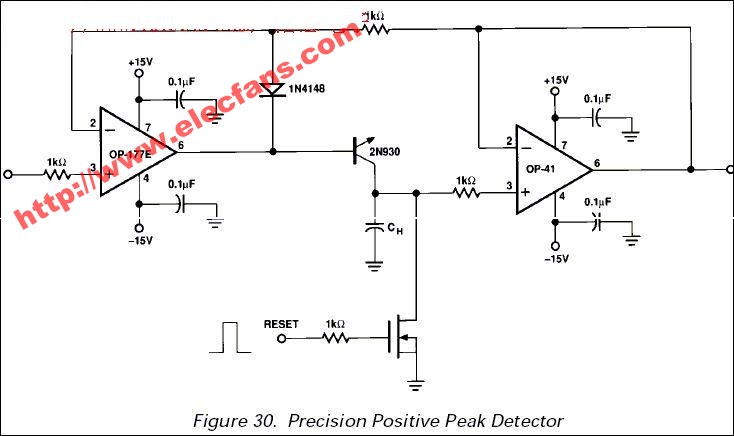

單脈沖電壓正向峰值保持電路

電路的功能

這是一種保持模擬信號電

2010-05-05 12:02:12 3617

3617

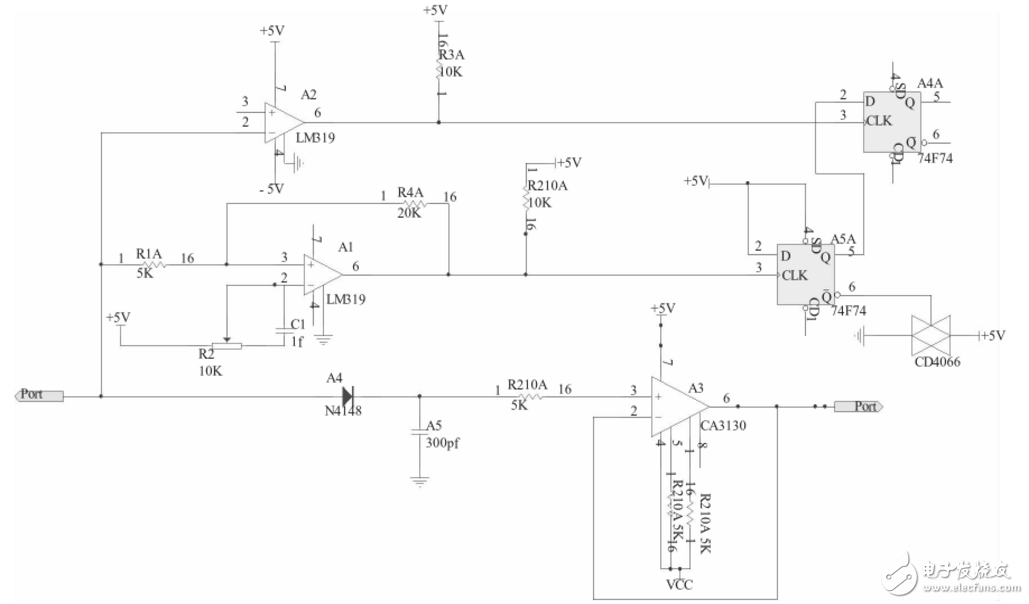

多道脈沖幅度分析器不僅能自動獲取能譜數(shù)據(jù),而且一次測量就能得到整個能譜,因此可大大減少數(shù)據(jù)采集時間,與此同時,其測量精度也顯著提高。自從20世紀50年代以來,

2010-09-25 09:26:13 2083

2083

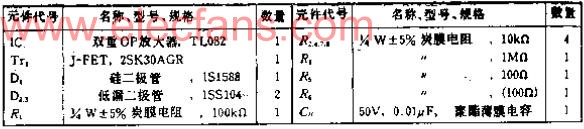

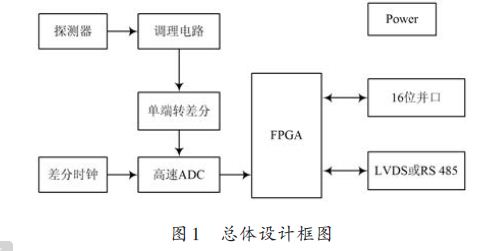

為了研究數(shù)字化γ能譜儀,本文提出一種基于FPGA的數(shù)字核脈沖分析器硬件設計方案,該方案采用現(xiàn)場可編程邏輯部件(FPGA),完成數(shù)字多道脈沖幅度分析儀的硬件設計。用QuartusⅡ軟件在FPGA平臺上完成了數(shù)字核脈沖的幅度提取并生成能譜。

2013-11-21 10:57:26 1948

1948

多道脈沖幅度分析儀和射線能譜儀是核監(jiān)測與和技術(shù)應用中常用的儀器。##FPGA

2014-06-09 10:42:39 1286

1286

基于FPGA 的數(shù)字核脈沖分析器硬件設計方案,該方案采用現(xiàn)場可編程邏輯部件(FPGA),完成數(shù)字多道脈沖幅度分析儀的硬件設計。

2015-02-03 09:55:05 1870

1870

脈沖幅度調(diào)制 (PAM) 是一種用于數(shù)字通信的編碼技術(shù),可將離散時間信號轉(zhuǎn)換為適用于高速有線通信系統(tǒng)的可變幅度連續(xù)時間信號。

2023-01-30 09:58:43 1732

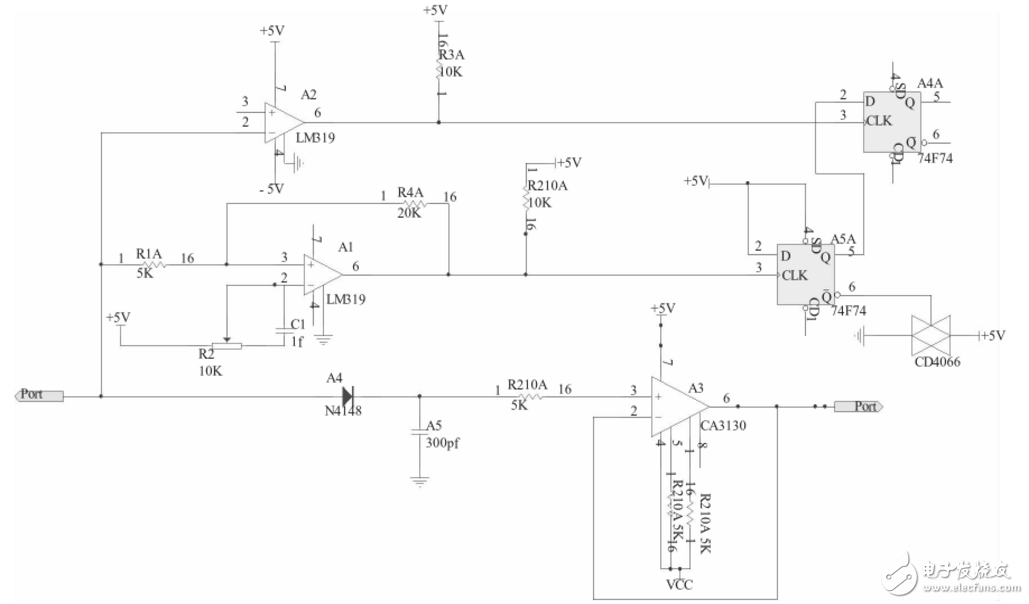

1732 各位大俠,現(xiàn)在需要檢測保持一個幾十ns的脈沖峰值,峰值大概在10mV左右(如果太小可以增大到幾百mV),如下圖所示。目前看了使用比較器的高速峰值保持電路,請問使用該電路能達到10ns的峰值檢測保持嗎?器件該怎么選擇?或者有沒有使用峰值檢波IC或者其他的方案可以選擇?希望各位指教。

2016-11-01 19:47:06

本帖最后由 xiaochezi 于 2016-3-30 11:23 編輯

如何將單片機PWM輸出的脈沖幅度升高至100V以上,頻率100Hz左右,能不能用脈沖變壓器實現(xiàn),12V電池供電的。

2016-03-30 11:21:17

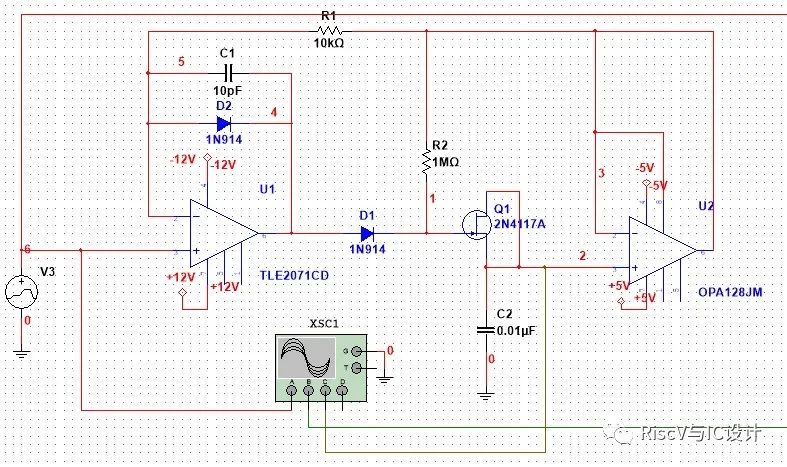

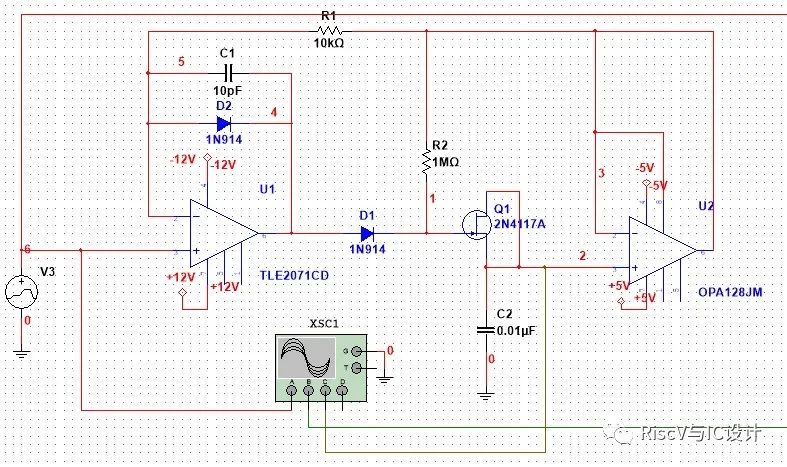

小弟最近正在搞一個高速窄脈沖峰值保持的電路,信號的上升沿>2ns,峰值在1V到2V之間,根據(jù)資料搭出了一個電路,但是峰值保持的電壓不對,不知道問題出在哪里。現(xiàn)在問題是上升沿為5ns時,峰值1V

2015-12-15 20:32:20

想要保持探測器輸入的窄脈沖信號的峰值,輸入脈沖寬度大概10ns,重頻幾十Hz,要實現(xiàn)峰值保持時間為幾毫秒,該使用哪種峰值保持電路設計,電壓型峰值保持電路能達到要求嗎?

2016-07-28 16:48:45

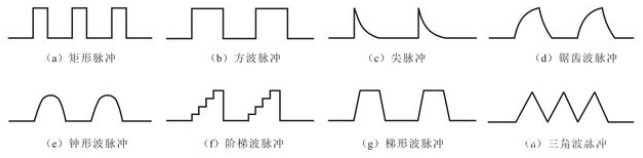

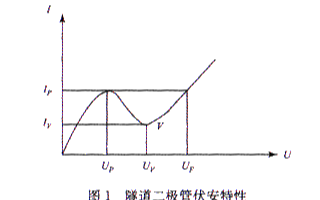

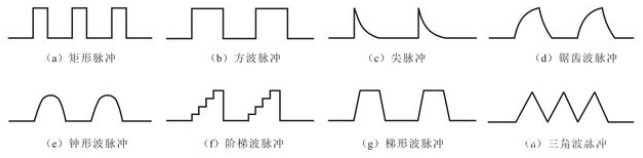

偶爾出現(xiàn)一次。 脈沖波形多種多樣,表征它們特性的參數(shù)也不盡相同,這里,僅以圖所示的矩形脈沖為例,介紹脈沖波形的主要參數(shù)。(1)脈沖幅度Vm--脈沖電壓或電流的最大值。脈沖電壓幅度的單位為V、mV

2008-05-26 13:12:14

=RC>>tk,電路就成為積分電路,見圖6。當輸入矩形脈沖時,由于電容器充放電很慢,輸出得到的是一串幅度較低的近似三角形的脈沖波。 (3)限幅器 能限制脈沖幅值的電路稱為限幅器或削波器。圖7是用二極管

2011-08-02 15:23:03

一般為2.5ns?ls。脈沖形成級的電路一般采用單穩(wěn)態(tài)觸發(fā)器和脈沖加、減電路。4、整形級為了使輸出的脈沖波形更趨近矩形,通常要求脈沖波形的前、后沿要陡峭,而整形級能充分改善矩形脈沖的形狀并具有電流

2017-10-16 10:25:44

一般為2.5ns?ls。脈沖形成級的電路一般采用單穩(wěn)態(tài)觸發(fā)器和脈沖加、減電路。4、整形級為了使輸出的脈沖波形更趨近矩形,通常要求脈沖波形的前、后沿要陡峭,而整形級能充分改善矩形脈沖的形狀并具有電流

2018-02-27 09:23:52

τ=RCt k ,電路就成為積分電路,見圖 6 。當輸入矩形脈沖時,由于電容器充放電很慢,輸出得到的是一串幅度較低的近似三角形的脈沖波。 ( 3 )限幅器 能限制脈沖幅值的電路稱為限幅器或削波器。圖 7

2013-12-16 21:51:39

設計要求:對脈沖信號進行放大,脈沖幅度20V, 頻率1MHZ 放到至500V 左右,應選何種放大器件? 高頻大功率三極管可以么?謝謝 賜教! (附件為脈沖信號及電路)附件333.png47.1 KB222.png73.5 KB

2018-08-13 06:57:15

高速數(shù)字電路設計的幾個基本概念高速數(shù)字電路設計的基本要求是什么

2021-04-27 06:19:05

本帖最后由 luna 于 2011-3-3 14:47 編輯

HM9102C/D是音頻/脈沖可轉(zhuǎn)換的撥號器,有上次號碼重撥(LNB)功能。它用CMOS工藝制成,無論在音頻方式還是在脈沖方式下,工作電壓范圍很寬。在掛機狀態(tài)下,消耗保持電流很小。

2011-03-02 23:56:27

蘇州泰思特電子科技有限公司研發(fā)的汽車微脈沖干擾模擬器GRP1-2A是專門用于車輛電子設備的抗擾度測試,期波形滿足ISO-7637-2(2004版)中P1和P2a脈沖要求。 其中脈沖P1用于模擬關(guān)斷

2014-05-18 09:51:33

混合信號設計調(diào)試。尤其適合對于單純模擬電路的調(diào)試和學習。項目名稱:高速脈沖電流采樣保持電路研究項目計劃:采用M2K自帶的任意波形發(fā)生器功能產(chǎn)生不同脈寬的脈沖信號,同時將峰保持電路的輸出接至M2K

2019-12-19 09:34:23

申請理由:脈沖NMR電源設計控制系統(tǒng)較為復雜,數(shù)據(jù)處理量大,需要高速設備,DSP能較好的滿足這一需求項目描述:一、應用脈沖NMR電源,主要應用于為磁體提供穩(wěn)定的高精度電源,產(chǎn)生高穩(wěn)定的磁場,可應用

2015-09-10 11:16:16

模擬設計中必須要考慮的因素有哪些?高精度高速A/D轉(zhuǎn)換器時鐘穩(wěn)定電路設計

2021-04-14 06:54:35

我想用51做一個C語言的檢測程序,如在20秒內(nèi)檢測脈沖數(shù)有10個,則有效,去觸發(fā),沒得有檢測脈沖的幅度,還有就是就是在20秒之內(nèi)檢測到的脈沖做個平均,看達到要求的脈沖個數(shù)如7個才觸發(fā),有高手給指點一下,用PIC也行,就是想檢測脈沖幅度單位時間內(nèi)達到要求的個數(shù)

2017-04-13 21:24:55

時鐘和PWM后續(xù)電路開關(guān)特性的限制。如果在實際中需要微妙級的T,則后續(xù)電路需要選擇開關(guān)特性很好的器件,以減小PWM波形的失真。 通過以上分析可知,基于PWM輸出的D/A轉(zhuǎn)換器轉(zhuǎn)換輸出的誤差,取決于通過低通濾波器

2011-08-26 09:49:56

脈沖幅度的計數(shù)分布曲線。能譜采集電路主要由線性放大器、過峰檢測電路、峰值保持電路、觸發(fā)ARM920T處理器S3C2410A內(nèi)置A/D模數(shù)轉(zhuǎn)換等組成。

2011-11-24 18:18:22

本帖最后由 gk320830 于 2015-3-9 15:55 編輯

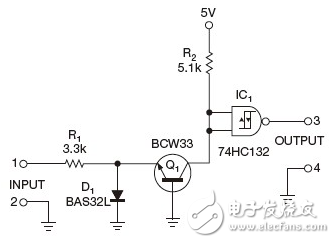

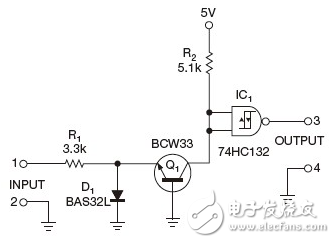

本例中的電路可將負脈沖轉(zhuǎn)換為正脈沖。盡管這個任務看似簡單,但負脈沖的幅度為-5V~-2V。按照不同應用要求,正脈沖也需要

2011-10-14 17:19:21

請教各位大神,我用STC12LE5A60S2單片機工作電壓3.3的,想監(jiān)測脈沖輸入,周期10--100mS,脈沖幅度5V。這部分電路如何設計?懇求各位幫忙,謝謝了。我不需要讀到具體的數(shù)據(jù),只要知道脈沖電平的高低變化,不知電路怎么設計?外部脈沖5V,單片機工作電壓只有3.3v,這部分電路要如何處理?

2017-01-10 10:33:58

多道脈沖幅度分析器結(jié)構(gòu)由那幾部組成基于LPC2134的多道脈沖幅度分析器設計

2021-04-09 06:44:29

你好,我需要一個峰值電壓采集保持器,來采集一系列脈沖的峰值,脈沖的電平為0-3.3v,求推薦。順便,還需要一個施密特特性的器件,把脈沖信號整形成一個方波,電平大于1v就判別為高,謝謝!

2018-08-24 11:28:34

決定敏捷脈沖的位置,這使HP 8131A成為快速評估數(shù)字電路的有用工具。隨著幅度命令的定時分辨率高于ECL器件的典型閥門時延值,可簡單地探測關(guān)鍵脈沖的參數(shù)的趨勢,而無需損失所需的定時關(guān)系。峰值可用

2020-09-28 22:14:16

HMC661LC4B用作峰值檢波器有一些疑問,想咨詢下這款芯片是否可以實現(xiàn)10ps左右寬的窄脈沖的峰值保持??

2019-01-04 10:37:40

如何用高速A/D轉(zhuǎn)換器測量脈沖波形?

2021-04-15 06:19:21

多道脈沖幅度分析器的結(jié)構(gòu)是怎樣設計的?多道脈沖幅度分析器的硬件是如何設計的?怎樣去設計多道脈沖幅度分析器的相關(guān)軟件?怎樣對多道脈沖幅度分析器的硬件電路進行仿真測試?

2021-04-14 06:31:11

有沒有ADG788和電容組成的脈沖發(fā)生電路?脈沖幅度高于供電電壓幅值。

2018-10-30 09:11:08

此圖是高壓正弦波放大電路,這個圖能自己產(chǎn)生正弦波,輸出幅度能達到峰峰值150V的要求嗎?對電路不是很了解,望高手分析,謝謝!

2018-12-28 11:32:49

顯示正、負峰值時,字體大,便于讀數(shù)。可設置倍率,直讀電壓峰值或電流峰值,讀數(shù)大于999時,自動調(diào)整小數(shù)點,以kA或kV為單位,采樣率最大40MSPS,采用12bit A/D轉(zhuǎn)換器,測量精度高。該儀表

2021-03-05 18:47:24

高壓脈沖發(fā)生器電路設計與制作資料推薦

2021-05-10 06:31:56

尖脈沖峰值電壓測量電路及制作

2009-04-14 10:12:45 7

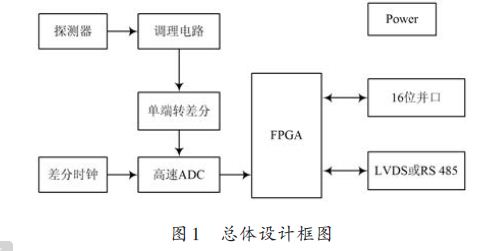

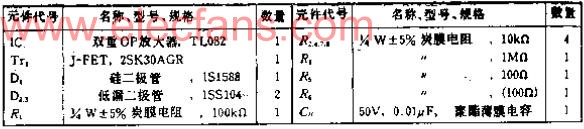

7 本文介紹一種采用電池供電的ADc和袖珍計算機Pc一1500通過接口電路組成的256道脈沖幅度分析器。其分析范圍為0.1—5V,微分非線性好于±2.5%,耗電約180mw,連續(xù)工作24小時道位漂移不

2010-05-19 09:12:18 30

30 摘要:通過對高精度脈沖幅度分析器的電路分析,得出了在使用過程中,采用高精度和低溫系數(shù)的電壓基準集成塊,可保證該脈沖幅度分析器比傳統(tǒng)脈沖幅度分析器靈敏度高、穩(wěn)定

2010-05-25 08:39:59 29

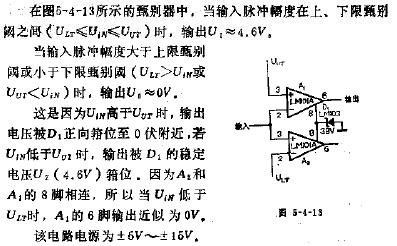

29 電壓脈沖峰值保持電路

2008-10-20 08:28:21 3636

3636

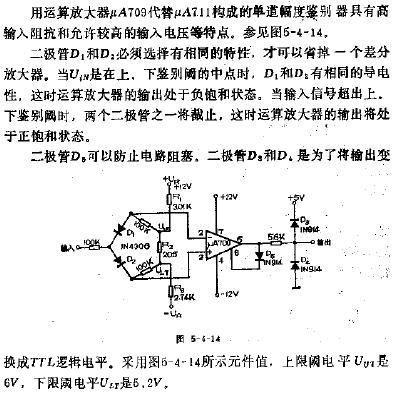

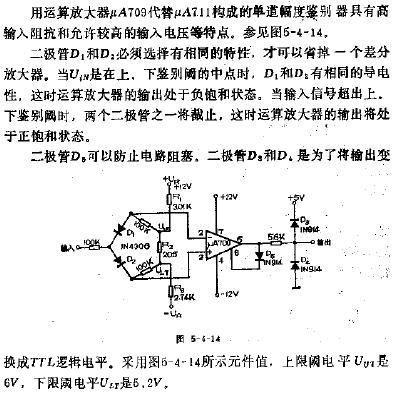

單值脈沖幅度鑒別器II

2009-04-13 10:53:17 1416

1416

單值脈沖幅度甄別器I

2009-04-13 10:53:54 1382

1382

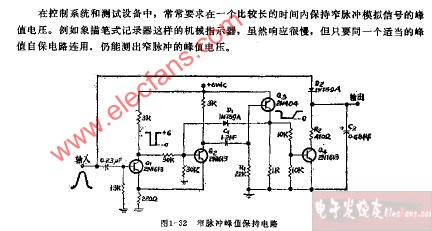

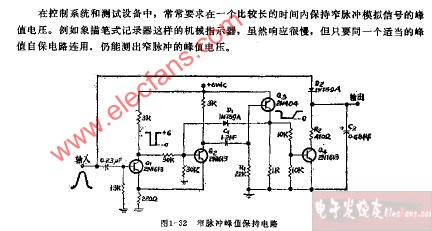

脈沖峰值保持電路圖

2009-06-20 11:15:38 1181

1181

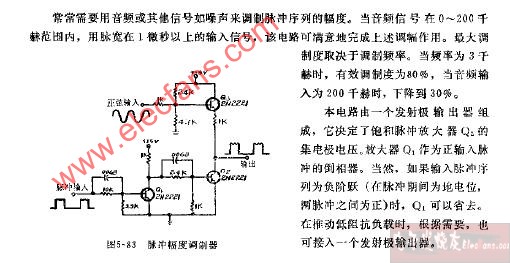

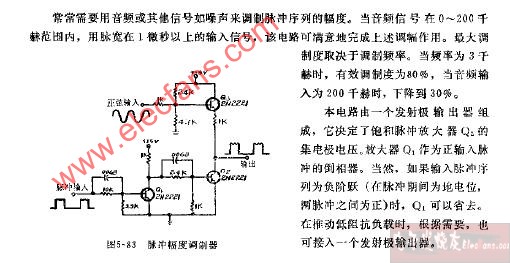

脈沖幅度調(diào)制器電路圖

2009-06-26 13:28:27 974

974

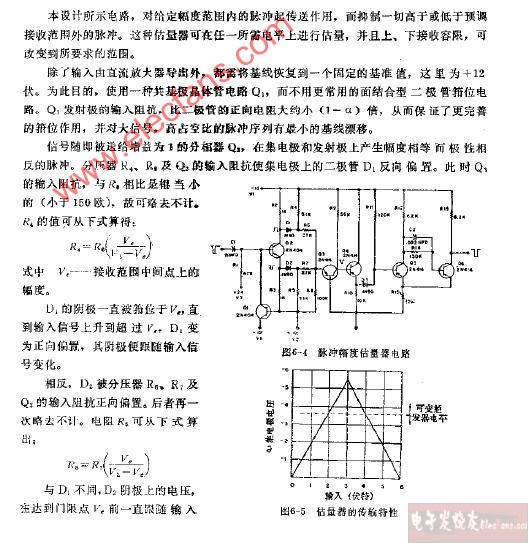

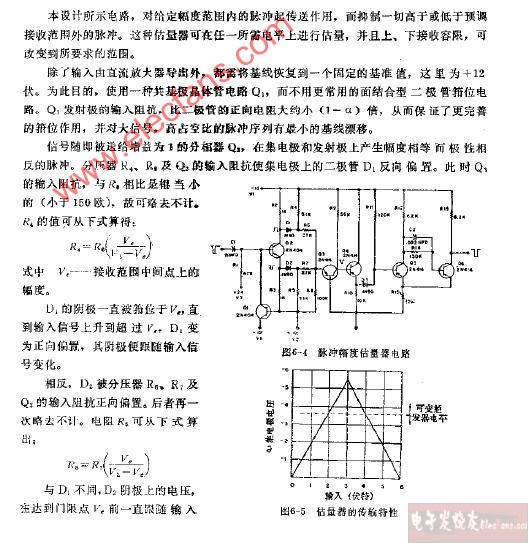

脈沖幅度估量器電路圖

2009-06-27 09:58:41 343

343

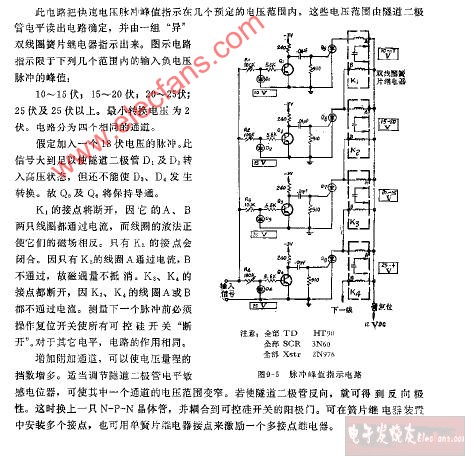

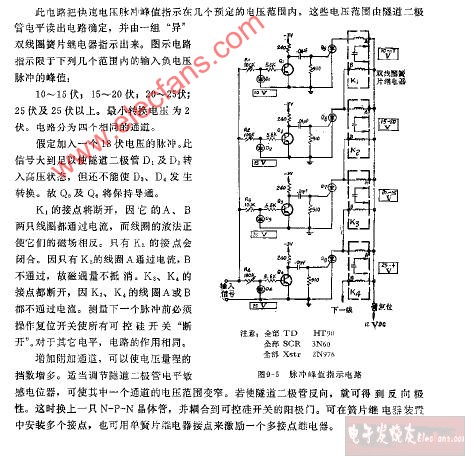

脈沖峰值指示燈電路圖

2009-06-29 13:15:18 603

603

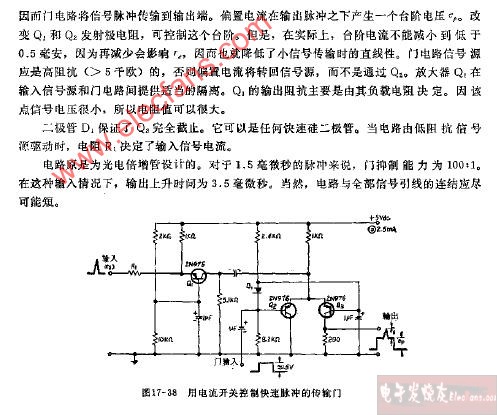

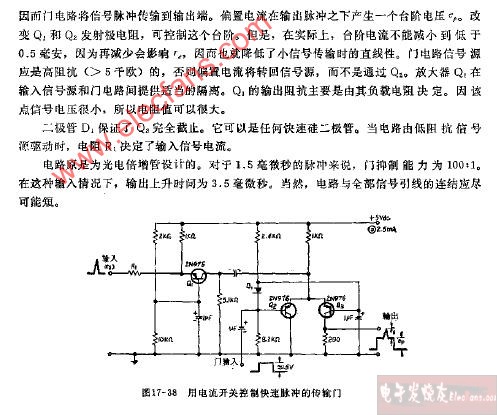

高速脈沖傳輸門電路電路圖

2009-07-03 11:41:11 1881

1881

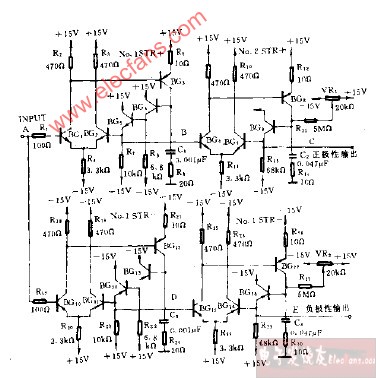

高速峰值保持電路圖

2009-07-17 11:38:31 798

798

窄脈沖高速峰值保持電路

電路的功能

“6-6”介紹的峰值保持電路,

2010-05-05 13:55:24 1601

1601

摘要:介紹一種以數(shù)字信號處理器(DSP)為核心的多道脈沖幅度分析器,它能夠進行核信號的采集\處理以及傳輸,然后經(jīng)過上位機的處理實現(xiàn)對射線的能量和強度的分析.DSP的采用保證了信號處理的實時性. 關(guān)鍵詞:DSP MCA A/D轉(zhuǎn)換 D/A轉(zhuǎn)換 探測器 高壓

2011-02-27 13:33:23 34

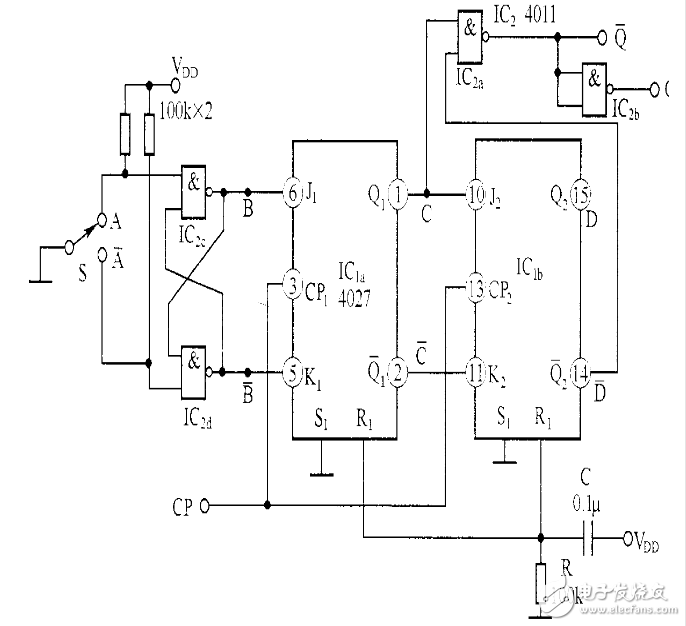

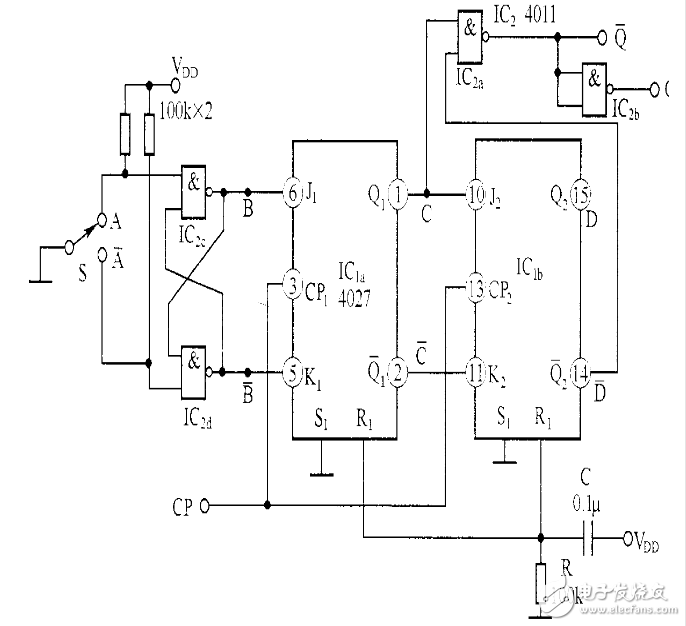

34 隨著脈沖技術(shù)的發(fā)展和普及, 在許多電子線路和控制系統(tǒng)中常常用到脈沖鑒相電路。它們可以把兩路周期波間的相位差轉(zhuǎn)換為方波脈沖寬度或進一步變換為直流電壓幅度 , 同時保持著信息的線性關(guān)系。集成組件 ! 就是這種類型電路之一。但它的轉(zhuǎn)換特性是雙值的, 即當

2011-03-08 18:13:13 206

206 用計數(shù)的方法解決

脈沖幅度分析器系統(tǒng)的丟峰問題,然后根據(jù)丟失

脈沖的個數(shù)進行補償,是解決

幅度分析系統(tǒng)中死時間問題的有效方法。本文詳細介紹了這種死時間損失補償?shù)姆椒ㄔ?/div>

2011-06-03 17:09:32 0

0 多道脈沖幅度分析器不僅能自動獲取能譜數(shù)據(jù),而且一次測量就能得到整個能譜,因此可大大減少數(shù)據(jù)采集時間,與此同時,其測量精度也顯著提高。

2011-10-13 12:01:13 4325

4325

電子發(fā)燒友網(wǎng): 本文主要分析了多道脈沖幅度分析器忙時間的形成特點,設計出來一套能減小系統(tǒng)忙時間的方案,從而大大地減少由于忙時間造成的脈沖漏計數(shù)。同時分析了改進后系統(tǒng)

2012-06-11 08:47:26 37

37 為滿足能譜分析中多道脈沖幅度分析器A/D轉(zhuǎn)換的要求,設計了一種高速脈沖峰值保持電路。以高速電壓比較器LM311、采樣/保持芯片LF398作為主要器件,具有幅度判別、波形采樣、峰值保

2012-06-28 17:16:15 639

639 2015 年 3 月 26 日,北京――是德科技公司(NYSE:KEYS)日前發(fā)布全新測量軟件,旨在幫助工程師使用 Keysight V 系列、Z系列和 S 系列實時示波器平臺快速和精確地表征 PAM-4(四電平脈沖幅度調(diào)制)信號。

2015-03-26 18:12:15 1012

1012 介紹了一種以采樣/ 保持器L F398 芯片為主要器件的峰值保持電路。該電路具有結(jié)構(gòu)簡單、調(diào)試方便、性能優(yōu)良等優(yōu)點可廣泛應用于各種脈沖分析系統(tǒng)。

2016-03-16 14:48:35 131

131 表1。脈沖掩模T1接口規(guī)范 額定線速度1.544兆位/秒 介質(zhì)一平衡雙絞線應用于每個傳輸方向。 測試負載阻抗1005%電阻性負載測試。 脈沖振幅的脈沖幅度為積極的孤立脈沖應為3.6V的之間。 脈沖形狀近似于孤立脈沖的每個脈沖形狀應符合圖1中的掩碼。此形狀以標準化形式顯示,標稱脈沖幅度顯示為1。

2017-04-07 15:16:18 3

3 基于LPC1764的多道脈沖幅度分析器的電路設計

2017-09-25 11:45:51 4

4 基于CPLD_ARM的多道脈沖幅度分析器設計

2017-09-25 12:55:06 8

8 摘要 :本文介紹了一種以采樣/ 保持器 L F398 芯片為主要器件的峰值保持電路。該電路具有結(jié)構(gòu)簡單、調(diào)試方便、性能優(yōu)良等優(yōu)點 ,可廣泛應用于各種脈沖分析系統(tǒng)。

2017-11-04 10:07:35 24454

24454

電壓毛刺脈沖在信號鏈路徑中很常見,特別在系統(tǒng)加電或斷電時更是如此。根據(jù)峰值幅度和毛刺脈沖持續(xù)時間的不同,系統(tǒng)輸出中的最終結(jié)果會是災難性的。其中的一個示例就是工業(yè)電機控制系統(tǒng),在這個系統(tǒng)中,數(shù)模轉(zhuǎn)換

2017-11-14 14:20:15 1

1 本例中的電路可將負脈沖轉(zhuǎn)換為正脈沖。盡管這個任務看似簡單,但負脈沖的幅度為-5V~-2V。按照不同應用要求,正脈沖也需要不同的脈沖寬度,而負脈沖是梯形的。脈沖必須先經(jīng)過一個長距離的傳輸線才能

2017-11-30 14:19:03 8840

8840

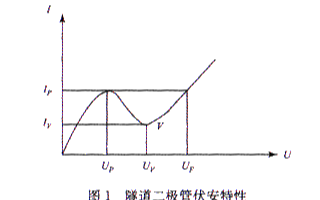

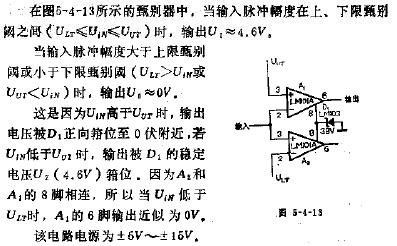

、生物學、化學、考古學等學科扮演著越來越重要的角色。由于閃爍記數(shù)器、半導體探測器等核輻射探測器輸出的脈沖信號幅度和入射粒子的能量成正比關(guān)系,因此,測量這些脈沖的幅度,就可以知道輻射的能量。

2018-01-23 09:45:01 4302

4302

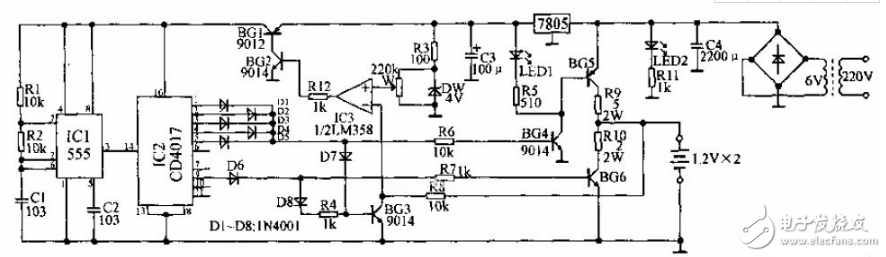

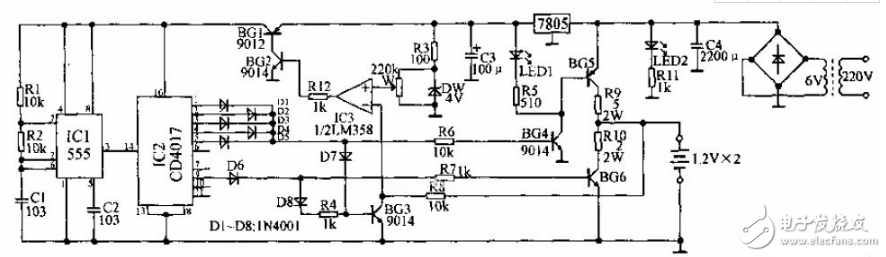

本文主要介紹了單次脈沖發(fā)生器電路圖大全(七款單次脈沖發(fā)生器電路設計原理圖詳解)。雙D觸發(fā)器CD4013、14二進制串行計數(shù)器/分頻器和振蕩器CD4060等組成的單脈沖/連續(xù)脈沖發(fā)生電路,主要應用于

2018-03-26 10:55:00 88680

88680

本文主要介紹了脈沖充電器電路圖大全(八款脈沖充電器電路設計原理圖詳解)。對電池(包括Nicd或NiH)充電的最好方式是脈沖式的充電法,其特點是脈沖高電平時對電池充電,而低電平時可對電池放電,要求放電

2018-03-05 10:37:43 76354

76354

核分析能譜測量所用的多道脈沖幅度分析器,在進行模數(shù)轉(zhuǎn)換時需要一定的時間,會使分析器產(chǎn)生漏計數(shù),給測量分析帶來誤差,需要對死時間進行修正。針對這種情況,探討了兩種有效的死時間修正方法。核分析能譜測量

2018-04-09 11:11:45 12

12 本文介紹一種采用電池供電的ADC和袖珍計算機PC-1500通過接口電路組成的256道脈沖幅度分析器。

2018-04-09 11:19:24 9

9 針對當前對多道脈沖幅度分析器的高處理速度、高集成度、友好人機交互的要求,采用三星公司生產(chǎn)的S3C2410芯片設計并實現(xiàn)了一種便攜式的核數(shù)據(jù)采集系統(tǒng)設計方案。對傳統(tǒng)的多道脈沖幅度分析器進行改進和簡化

2018-04-09 11:51:32 6

6 PAM是脈沖載波的幅度隨基帶信號變化的--種調(diào)制方式若脈沖載波是沖激脈沖序列,則前面討論的抽樣定理就是脈沖振幅調(diào)制的原理。也就是說,按抽樣定理進行抽樣得到的信號就是一一個PAM信號。

2018-11-06 18:56:22 0

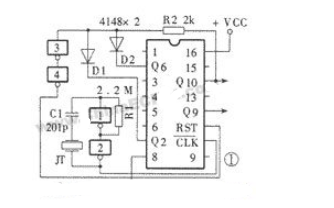

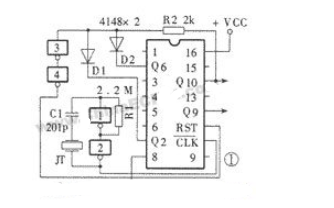

0 60Hz脈沖信號是時鐘電路常用到的信號。本文介紹一種60Hz脈沖信號發(fā)生電路,分析其存在的誤差,并給出減少誤差的改進電路。

2019-02-05 01:56:00 4176

4176

脈沖信號在通過甄別電路和控制電路時,甄別電路給出脈沖的過峰信息,并啟動A/D轉(zhuǎn)換。

2020-05-25 10:34:06 1491

1491 在高速脈沖中,上升、下降時間直接決定了脈沖的質(zhì)量,隨著快速沿脈沖在示波器的瞬態(tài)響應、時域反射技術(shù)、元器件的開關(guān)特性等方面的廣泛應用,人們不僅關(guān)注脈沖信號的頻率、幅度、寬度等特性,脈沖的上升、下降時間也得到了越來越大的重視。高速脈沖不僅僅要求脈沖的頻率高,脈寬窄,同樣對脈沖的快速沿提出了很高要求。

2020-07-27 15:38:45 3853

3853

實驗一脈沖幅度調(diào)制(pam)與系統(tǒng)實驗(電源技術(shù)作業(yè) 2018年發(fā)布的答案)-實驗一脈沖幅度調(diào)制(pam)與系統(tǒng)實驗.........

2021-09-24 11:23:06 15

15 半導體脈沖種子源驅(qū)動電路設計

2021-12-16 14:24:33 22

22 脈沖電路是可提供脈沖信號的功能單元電路,最基本的功能是產(chǎn)生脈沖信號,并對產(chǎn)生的脈沖信號進行必要的轉(zhuǎn)換處理,使其滿足電路需要。

2022-08-16 16:55:37 3083

3083

本應用筆記提供了DS2148/DS21348/DS21Q48/DS213Q48和DS21448的寄存器設置,用于配置發(fā)送器的脈沖幅度不同于數(shù)據(jù)資料中記錄的線路構(gòu)建(LBO)模式。下表列出了寄存器

2023-02-13 15:42:40 583

583 脈沖變壓器的規(guī)格主要包括與o/p響應相關(guān)的不同參數(shù),這些參數(shù)將定義允許的脈沖失真限制,主要包括:脈沖幅度;脈沖幅度是信號除無用尖峰之外的最高峰值。·上升時間(Tr);上升時間是輸出信號在初級嘗試

2023-05-29 15:41:23 339

339 是德Keysight 86100D-9FP PAM-N 分析軟件。該軟件可以提供 全面的光和電 PAM-4 信號分析,幫助工程師應用Keysight 86100D DCA-X示波器平臺完成快速且精確的PAM-4(4 電 平脈沖幅度調(diào)制)信號測試和驗證。

2023-09-22 14:44:22 291

291

峰值保持電路是用于捕捉變化的輸入信號的峰值,是利用記錄儀記錄峰值的關(guān)鍵電路,其有各種電路結(jié)構(gòu),分析也相對簡單。

2023-10-13 15:08:25 3130

3130

延時脈沖電路是一種可以在輸入脈沖信號的基礎(chǔ)上產(chǎn)生一個延時后的輸出脈沖信號的電路。

2023-10-26 09:20:21 524

524 什么是正尖脈沖?什么是負尖脈沖? 正尖脈沖和負尖脈沖是時間信號中常見的兩種形式。它們是一種特殊的脈沖信號,具有較短的持續(xù)時間和較高的峰值幅度。 首先,正尖脈沖是一種單極性脈沖信號,其峰值幅度快速上升

2024-02-18 09:43:36 334

334 非常重要。 晶閘管的觸發(fā)脈沖需要滿足以下三種要求: 觸發(fā)脈沖幅值要足夠大: 晶閘管需要一個足夠大的觸發(fā)脈沖幅值來進行開門,通電流。觸發(fā)脈沖的幅值必須能夠超過晶閘管的保持電流和激勵電流,以確保晶閘管能夠可靠地觸發(fā)。 觸發(fā)脈沖寬

2024-02-27 14:32:32 149

149 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論