二進制中的兩個數字0和1稱為位(bit, 是二進制數字binary digit的縮寫)。在數字電路中,使用兩個不同的電平表示這兩個位。一般情況下,1 用高電平表示,0用低電平表示,這種邏輯體制稱為正邏輯。

2024-02-04 16:54:09 462

462

電路圖如下!~想用光敏三極管的信號來使用單片機的外部中斷,但是單片機I/O口一直保持初始值高電平,不能被光敏三極管的信號改變。同樣的管腳,用一個震動模塊產生的信號可是實現功能,但是光敏三極管就不能實現。請教高手是什么原因!~~如何解決?

2019-10-15 21:57:14

的方法是擴展一片8251 或 8250 通用同步/異步接收發送芯片(USART),需額外占用單片機I/O 資源。本文介紹一種用單片機普通I/O 口實現串行通信的方法,可在單片機的最小應用系統中實現與兩個

2012-06-07 15:17:42

我已經成功地編程了CyPress I/O模塊,但是當我進入驅動站時,診斷標簽中的I/O LED不會變成綠色。 以上來自于百度翻譯 以下為原文I've successfully programmed

2019-01-09 14:11:31

對于剛進入嵌入式學習的小伙伴,是不是總會遇到 I/O和GPIO的說法,兩個到底都是什么呢?這里為你揭開I/O和GPIO的神秘面紗,快來學習一波。一句話總結, I/O是泛指所有類型的輸入輸出端口,包括單向的端口如邏輯門電路的輸入輸出管腳和雙向的GPIO端口。

2021-12-09 07:31:48

我想用布爾開關來控制I/O輸出的高低電平,請問出現圖片這種情況,該怎么解決。還有如果要用8個開關控制8個口要用8個DAQ助手還是可以合在一起的。

2017-05-13 23:01:59

數字邏輯功能單元數字邏輯最終是需要通過數字電路的形式來實現的緩沖門:是僅具有緩沖功能的基本門電路,僅有一個輸入端口,也僅有一個輸出端口功能:將輸入端口的信號電平原封不動地搬移到輸出端口,輸入為0

2021-07-29 08:04:47

數字邏輯功能單元有哪些呢?數字邏輯是怎樣通過數字電路的形式來實現的?

2021-11-02 07:08:41

你好,當我直接連接邏輯低“0”到數字輸出引腳,似乎輸出引腳應始終是Low,但它總是高電壓時,我檢查了數字萬用表輸出引腳。為什么它的產量總是很高?最好的問候,…添加我的項目。如果你有什么問題,請告訴我

2018-09-13 15:20:20

輸入管腳的處理 在多數情況下,集成電路芯片的管腳不會全部被使用。例如74ABT16244系列器件最多可以使用16路I/O管腳,但實際上通常不會全部使用,這樣就會存在懸空端子。所有數字邏輯器件的無用端子

2009-04-12 12:03:33

的《邏輯器件選型指導書》。3.6:邏輯器件的使用指南1:多余不用輸入管腳的處理在多數情況下,集成電路芯片的管腳不會全部被使用。例如74ABT16244系列器件最多可以使用16路I/O管腳,但實際上通常不會

2008-06-24 09:38:52

小弟畢設需要用到一個邏輯電平轉換模塊,主要問題如下: 1、FPGA輸出的 3.3V 數字信號 需要通過 邏輯電平轉換芯片,轉換為1.8V或2.5V或3.3V中的一種。 2、 本設計需要16路數字IO

2015-09-04 21:21:28

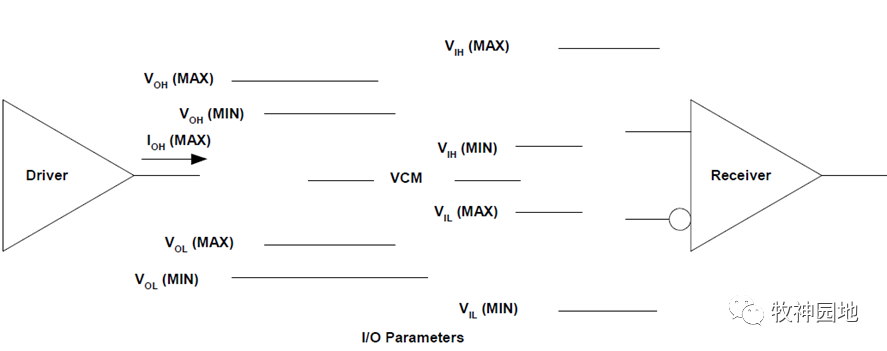

兼容的問題。這并不罕見,例如,當工作于1.8V的數字電路必須和工作于3.3V的模擬電路通信時就會有這個問題。本文分析了邏輯電平的基本原理,并主要研究了如何在串行數據系統中不同的邏輯電平范圍之間進行轉換。[/hide]

2009-10-24 13:43:45

確定: - 損壞的用戶I / O引腳的鉗位二極管運行良好(我測量過) - 為LVCMOS25和上拉設置了正確的FPGA配置 - 即使在損壞的用戶I / O引腳上將輸入電壓設置為邏輯電平“0”,我也始終

2020-04-07 12:26:15

雙向管腳的控制代碼本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 對于單向的管腳,輸入信號或者輸出信號

2015-07-01 10:32:49

實際的應用系統中,由于考慮未來的功能擴展或其它原因,經常會有未使用的 I/O。如何處理這些 I/O,關系應用系統的消耗電流甚至系統可靠性。因此,正確處理未使用的 I/O 端口,對于基于MCU

2021-11-04 09:09:01

量輸入模塊+數字量輸出模塊實現方式1、在200SMART軟件里面添加遠創智控YC9000的GSD文件,操作步驟由下圖所示:點擊GADML管理,點擊瀏覽找到GSD文件放置位置選擇您使用的plc,以我

2023-01-04 11:53:47

STM32F4開發板怎樣通過引腳輸入高低電平的方式對電機的正反轉進行邏輯控制呢?STM32F4開發板與驅動模塊如何實現對兩個電機的邏輯控制呢?

2021-09-18 07:33:39

TC4052B各引腳功能及管腳電壓 概述:TC4052B 多路邏輯開關用于選擇與混合模擬信號和數字信號。TC4052B 是帶參考電平的雙向雙路單刀四擲譯碼器。控制端子的數字信號經

2008-10-10 17:42:47

都可配置成輸入、輸出。每個bank的首尾管腳只能作為單端I/O,其余48個I/O則可配置成24對差分I/O。在差分信號的實現過程中,管腳分配應選擇相應電平標準的bank中除首尾以外的其他48個IO

2020-12-23 17:17:47

,首先需要將模擬信號轉換為數字信號,并對其編碼后再提交給數字系統處理。 顯然,為了滿足以上這些要求,需要設計許多種類的數字電路才能實現人類的需求。數字邏輯就是這樣一種用來分析和設計復雜的數字邏輯電路或

2009-04-07 10:44:14

labview怎么實現像plc一樣的通過輸入輸出I/O量,控制開關量,比如通過I/O點控制繼電器的吸合。怎么給I/O量分配地址,怎么在程序里使用這些變量實現一系列有序的動作。希望能附上一份樣例程序,讓小弟學習領會,請多指教,謝謝。

2016-04-25 00:51:33

stm32 的電平是3.3V,但是有些模塊的電平要求5V,大家是怎么實現的呢?

2016-11-28 22:34:36

i2c_master_bit_ctrl.v 完成位傳輸的功能。位傳輸的功能包括數據按位傳輸的實現和I2C協議各個命令的實現兩部分。如圖 4-5 所示開始和重復開始命令的產生包括 5 個階段:idle

2018-10-09 11:43:44

8-1數據選擇器 邏輯功能:上圖是8-1數據選擇器的真值表,我們從真值表中可以看出,當A=000時,輸出I0為高電平,其余為低電平,對應高電平的開關閉合,而對應低電平的開關則仍保持斷開,因此,Y的輸出為

2020-04-24 15:07:49

)來實現組合邏輯,每個查找表連接到一 個D觸發器的輸入端,觸發器再來驅動其他邏輯電路或驅動I/O,由此構成了既可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模塊,這些模塊間利用 金屬連線互相連接或

2019-08-11 04:30:00

請問一下我在使用51最小系統板做流水燈的時候通過程序無法改變I/O輸出電平是怎么回事,I/O持續輸出5V高電平,但是把芯片換到另一個基座就可以改變,請問哪里可能出問題了

2023-09-27 07:38:20

為什么配置I/O口:I/O端口寄存器復位后默認為輸入(輸出高阻態);為實現I/O端口功能需要先對端口進行I/O口初始化配置I/O口需要的幾種寄存器:ANSELx(模擬選擇寄存器):0 = 數字I/O

2021-11-24 06:19:54

前言此實驗是通過STM32CubeMX來配置stm32實現按鍵輸入,以此來了解stm32I/O的輸入操作及如何使用HAL庫來實現I/O輸入。本實驗中的按鍵操作使用的是軟件中斷,并未用到stm32

2022-03-01 06:58:08

,輸出高低電平。就是通過這簡單的控制電平來實現大多數的應用控制。1. 什么是 I/O 口?I 表示 IN(輸入),O 表示 OUT(輸出),所以 I/O = 輸入/輸出2. I/O 具體能做什么呢?如果你是剛剛步入電子的新手,那你最好要知道一下I/O口具體能做什么。感性的認識對你的..

2021-11-24 06:47:23

UEFI學習(四)-SuperIo的訪問一、什么是Super I/O?二、我們要用SuperIo實現什么三、NCT5581D的訪問機制一、什么是Super I/O?Super I/O 芯片也叫 I

2022-01-24 08:12:27

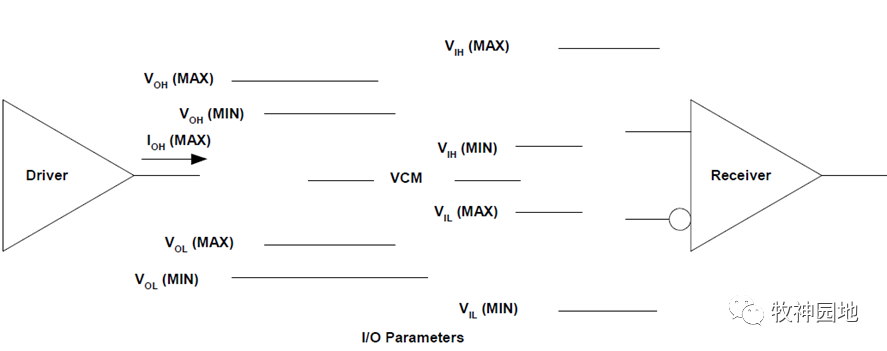

本文介紹了數字I/O和邏輯分析儀的常用術語和定義。

2021-05-06 06:39:26

P1.7使用上升沿觸發中斷。在仿真運行時,在外部還沒有加上中斷信號時,會進入一次中斷。每次都是這樣,是不是由于仿真過程中I/O管腳有上升電平造成的?

2015-02-10 14:13:16

使用MCU的I/O管腳連接物理按鍵,當按鍵按下時會發送上升沿或下降沿的電平出發中斷,這個容易判斷。

請問,對于按鍵雙擊動作,以及按鍵長按動作,應該如何判斷?

是否存在簡單的實現方法,最好能給Demo源碼,多謝!

2023-08-24 07:42:04

的作用。因此,探討一些鍵盤的特殊結構,用盡可能少的輸入輸出端口實現較多數量的按鍵數仍具有重要的應用價值。 有些特殊情況下,在組成一個最小的單片機系統的過程中,由于通用的I/O口有限,而又需要大量的按鍵

2012-02-15 22:02:49

邏輯門是數字電路的基礎。各種多姿多彩的邏輯門組合在一起,形成了數字電路的大千世界。實際上,邏輯門反映的是邏輯代數的幾種基本運算,只要你能夠實現這樣的邏輯代數規則,你就能夠用其他設備來實現邏輯門的功能,看!

2019-07-23 07:03:30

單片機I/O口如何檢測按鍵輸入電平?

2021-10-26 07:01:11

單片機應用系統中,常有用單片機的I/O口來實現自關機(徹底關機)的功能。一般用單片機的一個I/O口控制一個電子開關來實現,因單片機關電后,失去電源,所以在關機時,實現關機的IO口的電平必須用低電平

2017-12-14 20:15:53

信號,而非電平信號)直接模擬輸入到片上外設模塊,比如ADC模塊等等。開漏輸出模式開漏輸出模式下,通過設置位設置/清除寄存器或者輸出數據寄存器的值,途經N-MOS管,最終輸出到I/O端口。這里要注意

2021-05-18 06:30:00

12路、模擬輸入 4路:Neuron3150芯片I/07至I/0010管腳用來接收室內溫濕度值,配置成4路模擬電路;I/O-O至I/O-6管腳和利用地址總線擴展出的3路I/O口共同形成24路數字

2021-06-17 07:30:00

12路、模擬輸入 4路:Neuron3150芯片I/07至I/0010管腳用來接收室內溫濕度值,配置成4路模擬電路;I/O-O至I/O-6管腳和利用地址總線擴展出的3路I/O口共同形成24路數字

2021-06-23 07:30:00

的SSI接口卡,但價格昂貴且驅動程序較為復雜。工控機上多配備數字量輸入/輸出卡。本文采用數字量輸入/輸出卡控制SSI并行接口模塊SSI208P,實現了一種SSI接口的低成本、高速數據采集方法。1

2019-05-28 05:00:03

芯片上,接通Sink節點和計算機就可以實現該功能. 3.1 程序流程圖 程序流程圖如圖2所示. 3.2 程序結構 3.2.1 實現I/O控制的配件文件 配件中定義了I/O控制的模塊

2018-11-13 16:27:39

我畢設要做一個多通道數采系統,需要用NI 多功能數采卡的數字I/O輸出控制CD4051的3個控制端,在數字輸出的編程上遇到了點問題。想請教一下,這個DO輸出的數字量是瞬時的還是持續的?我需要通道選定后保持,然后發波、采集,完了之后再切換通道,即改變數字輸出量。這個數字I/O編程怎么實現?

2014-04-25 21:44:34

如何實現數字系統的電平和極性轉換?比較器在電路中起到什么作用?

2021-04-14 06:31:09

在數字電路中開關(switch)是一種基本的輸入形式,它的作用是保持電路的連接或者斷開。Arduino從數字I/O管腳上只能讀出高電平(5V)或者低電平(0V),因此我們首先面臨到的一個問題就是

2022-01-17 08:35:42

操作PIC24 I/OPIC24是一款16位的單片機,它的I/O操作和STM32差不多,但是比STM32更簡單。操作PIC24的I/O輸出高低電平需要配置一下寄存器:1.TRISx,該寄存器控制I

2021-11-24 07:30:02

至 300VDC 輸入電壓的靈活解決方案通過 MCU 實現可編程開關閾值優秀的長期可靠性,并提供數字隔離功能提供濕電流控制選項輸出可以是 I2C 輸出,也可以是數字輸出

2018-09-20 08:55:55

MCU通用I/O引腳擴展 低端MCU由于I/O口數量不足導致部分功能無法實現,用戶需要使用數字集成芯片進行擴展,如74LS系列移位寄存器,但是這種集成芯片也會由于引腳數量限制而無法確保單片機端口

2024-01-08 09:35:10

怎么實現基于可編程邏輯器件的數字電路設計?

2021-05-06 08:36:18

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

嗨,大家好,我需要能夠驅動連接到的特定設備3.3 I / O bank(配置為輸出)至邏輯高電平為3.5V。有可能的將I / O引腳上的上拉電阻器設置為+ 5v以幫助實現此目的?如果你想知道什么我

2019-05-15 14:18:47

。這類轉換器的常見應用是以字節(byte)訪問的存儲器及I/O器件。 自動感測雙向邏輯電平轉換器(推挽型輸出)的工作原理是:啟用(EN)引腳為低電平時,轉換器處于待機狀態;EN引腳為高電平、I/O

2018-10-10 17:10:37

硬件設備樹莓派 * 157H76兩相四線步進電機 * 1DM542驅動器 * 136V DC開關電源3.3V-5V電平轉換(驅動器輸入需要5V脈沖,樹莓派可控管腳輸出電壓不夠)接線接線如下所示

2021-07-08 09:29:55

描述此參考設計是一個具有雙隔離輸出的 1W 電源,適合于空間受限的應用。利用 24V 和 3.3V 隔離輸出,此設計專用于為工廠自動化設置的可編程邏輯控制器 (PLC) I/O 模塊供電。此設計符合

2022-09-22 06:22:07

電平才能跳變,否則維持原來狀態。如下圖,A、B分別是2個輸入端電平,O是輸出端電平,怎樣用簡單的電路實現功能?關鍵是第2階段和第4階段的跳變條件要滿足。

2013-10-28 14:16:25

DSPF2812 GPIOF12配置成通用I/O,發現輸出不了邏輯高電平,結果發現這個管腳沒有內部上拉,是這個原因嗎?

2020-06-04 14:04:45

閃存設備管理技術的現狀及存在的問題是什么?閃存設備I/O軟件的分層結構是怎樣的?怎樣設計并實現閃存設備I/O軟件?

2021-04-27 06:44:40

輕松實現高速串行I/OFPGA應用設計者指南輸入/輸出(I/O)在計算機和工業應用中一直扮演著關鍵角色。但是,隨著信號處理越來越復雜,I/O通信會變得不可靠。在早期的并行I/O總線中,接口的數據對齊

2020-01-02 12:12:28

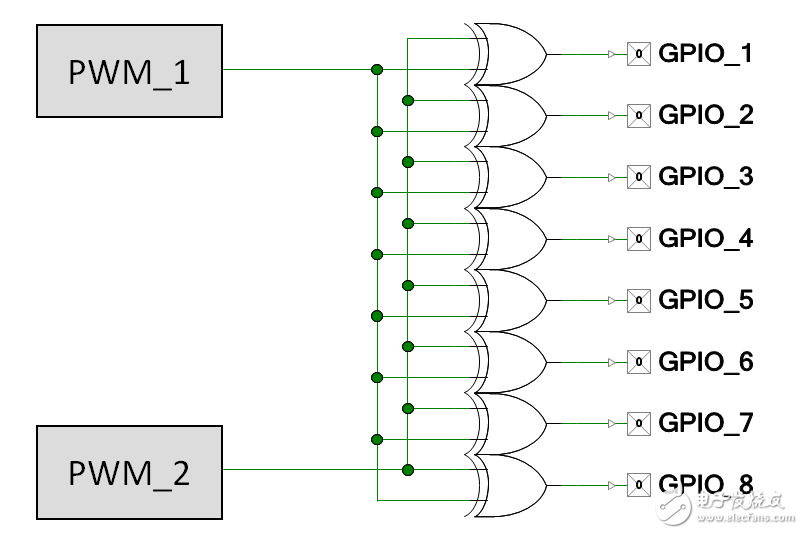

硬件實現的應用包括了靈活的編碼輸入,PWM 信號I/O,PID 控制,定制計數器實現,數字協議仿真,離散控制和定制測量等等。[hide] [/hide]

2009-07-23 08:15:57

。以下將要討論基于下一代I/O技術的一些應用。設計挑戰1、高數據吞吐量需要新的信令方案由于高端手機LCD顯示器的分辨率超過了SVGA(800×600),而翻蓋式電話中應用處理器和LCD模塊之間的RGB

2019-05-27 05:00:06

機型豐富,更多選擇 S7-200 SMART PLC提供不同類型、I/O點數豐富的CPU模塊,單體I/O點數最高可達60點,可滿足大部分小型自動化設備的控制需求。另外,CPU模塊配備標準型

2020-12-04 16:21:47

MxxxT 工業遠程以太網I/O 數據采集模塊內嵌32 位高性能微處理器MCU,集成1 個工業級10/100M 自適應以太網接口支持標準

2021-10-26 19:50:14

數字系統的基本算法與邏輯電路實現:本章主要介紹數字系統的基本算法設計及對應的邏輯電路的實現方法。算法設計中主要考慮的因素1.邏輯指標這是數字系統最重要、

2009-09-01 09:04:09 0

0 摘 要:介紹了聲納脈沖偵察模塊的測向測距原理、硬件設計及其實現。聲納脈沖偵察模塊硬件電路以數字信號處理器為核心,通過可編程門陣列實現邏輯控制,再配以適當

2006-04-07 00:36:43 722

722

二值數字邏輯和邏輯電平

二進制數正好是利用二值數字邏輯中的0和1來表示的。二值數字邏輯是Binary Digital Logic的譯稱。 與模擬信

2009-04-06 23:37:10 3518

3518

摘要:邏輯電平轉換技術及其缺陷—Maxim的解決方案。

對邏輯電平轉換的需求越來越多的數字IC采用與以往不兼容的電源電壓、更低的VDD、或者VCORE和VI/O不同的

2009-04-23 14:01:11 3035

3035

基于FPGA和CPLD數字邏輯實現ADC技術

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現

2010-05-25 09:39:10 1309

1309

本文是對三極管實現邏輯電平轉換進行具體分析,希望能幫助到大家!

2016-03-24 17:35:11 14

14 三電平SVPWM方案的實現,有需要的下來看看

2016-03-30 14:59:59 24

24 邏輯門是數字電路的基礎。各種多姿多彩的邏輯門組合在一起,形成了數字電路的大千世界。實際上,邏輯門反映的是邏輯代數的幾種基本運算,只要你能夠實現這樣的邏輯代數規則,你就能夠用其他設備來實現邏輯門的功能。

2017-09-19 14:19:18 23

23 問題而寫。文章先介紹常用的幾種邏輯電平,然后給出其與光模塊的接口電路。 TTL 電路的電平就叫 TTL 電平,CMOS 電路的電平就叫 CMOS 電平。 TTL 集成電路的全名是晶體管-晶體管邏輯集成電路(Transistor-Transistor Logic),標準 TTL 輸入高電平最小 2V,輸出高電平

2017-11-06 16:50:08 100

100 異或門是數字邏輯中實現邏輯異或的邏輯門。有多個輸入端、1個輸出端,多輸入異或門可由2輸入異或門構成。若兩個輸入的電平相異,則輸出為高電平1;

2017-11-28 12:07:05 65781

65781

DigilentPmodLVLSHFT是一個數字邏輯電平轉換器。

2019-11-29 14:53:50 1774

1774

本文檔的主要內容詳細介紹的是使用單片機實現單個數碼管指示邏輯電平的C語言實例免費下載。

2020-11-12 17:33:55 9

9 電平轉換在實際電路設計中常常會用到,不同種類邏輯電平之間的轉換一般通過特定邏輯功能器件實現(如使用MAX232實現TTL轉RS232等等),但隨著器件集成度的增加,工藝的提升,現在的控制器使用的邏輯

2021-01-07 17:07:00 12

12 電子發燒友網為你提供實現管腳電平數字邏輯功能和降低CPU負載資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-14 08:46:14 9

9 為了精簡電路 電器中會用到邏輯電平代替復雜的接線 他們都是如何設計的呢? CMOS器件與TTL器件? ? CMOS電平與TTL電平 ? 如何利用MOS管實現雙向電平轉換 ? 什么是LVDS電平

2022-12-14 11:36:07 437

437 差分邏輯電平之間的匹配,主要應用于時鐘和高速信號。

2023-06-25 14:56:13 1499

1499

進行邏輯計算或判斷,從而實現數字電路的功能。 在現代電子設備中,信號的邏輯狀態往往通過邏輯電平來表示。邏輯電平分為高電平和低電平兩種,通常高電平表示“1”,低電平表示“0”。“1”和“0”是數字電路中最基本的邏輯符號,

2023-09-19 17:16:11 694

694 為什么要進行電平轉換?電平轉換的幾種實現方式? 電平轉換是在數字信號中,將信號的電平從一種電平轉換為另一種電平的過程。電平轉換通常用于將數字信號從一個設備傳輸至另一個設備。 在數字系統中,電平轉換

2023-11-01 14:56:17 1194

1194 什么是線與邏輯,要實現它,在硬件特性上有什么具體要求? 線與邏輯是一種基本的數字邏輯電路,用于實現布爾代數中的邏輯運算。在線與邏輯中,當所有輸入信號都是高電平時,輸出信號才為高電平;否則,輸出信號

2023-11-17 14:11:38 1408

1408 Metal-Oxide-Semiconductor)。 TTL是一種基于晶體管的數字邏輯電平標準,使用5V電源供電,邏輯高電平(1)通常在2.4V以上,邏輯低電平(0)在0.4V以下。TTL邏輯電平的優點是速度快、噪聲容忍度高,常見于早期的數字電路。然而,由于功耗較大,現在更常用的是

2023-11-17 14:16:06 650

650 邏輯電平是數字電子系統中的關鍵概念之一。它決定了信號被認定為高電平還是低電平,并進一步影響著數字電路的正確操作。邏輯電平是用來表示數字信號狀態的電壓水平。在數字電子系統中,常用的邏輯電平有高電平

2023-11-24 08:20:20 1681

1681

電子發燒友App

電子發燒友App

評論