1. 概述

隨著集成電路技術的快速發展,半導體存儲、微處理器等相關技術的發展得到了飛速發展。FPGA以其可靠性強、運行快、并行性等特點在電子設計中具有廣泛的意義。作為一種可編程邏輯器件,FPGA在短短二十年中從電子設計的外圍器件逐漸演變為數字系統的核心。伴隨著半導體工藝技術的進步,FPGA器件的設計技術取得了飛躍發展及突破。

分頻器通常用來對某個給定的時鐘頻率進行分頻,以得到所需的時鐘頻率。在設計數字電路中會經常用到多種不同頻率的時鐘脈沖,一般采用由一個固定的晶振時鐘頻率來產生所需要的不同頻率的時鐘脈沖的方法進行時鐘分頻。

在FPGA的設計中分頻器是使用頻率較高的基本設計,在很多的設計中也會經常用到芯片集成的鎖相環資源,如用Xilinx的DLL以及Altera的PLL來進行時鐘的分頻、倍頻與相移。在一些對時鐘精度不高的場合,會經常利用硬件描述語言來對時鐘源進行時鐘分頻。

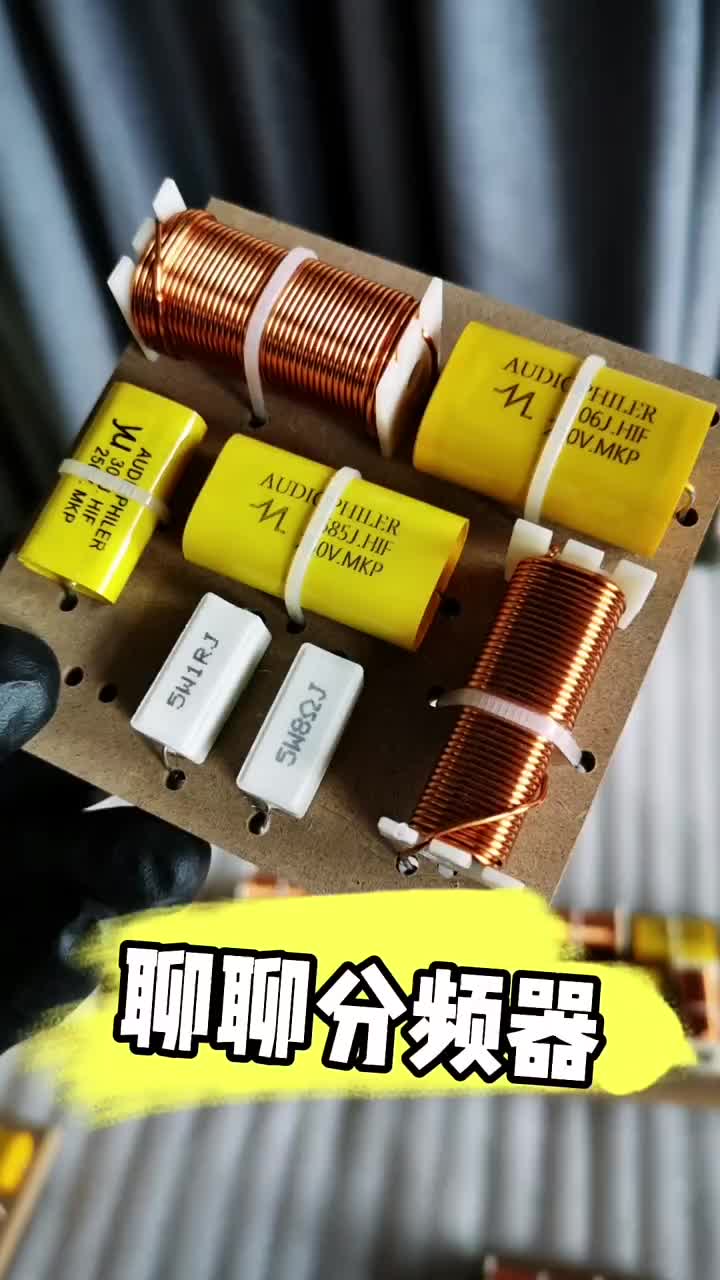

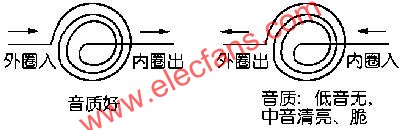

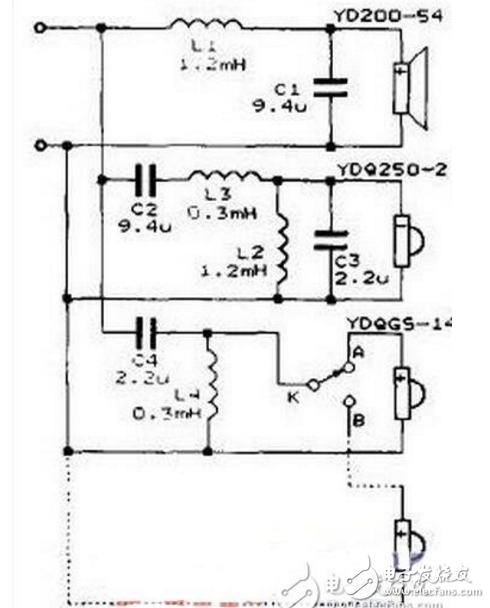

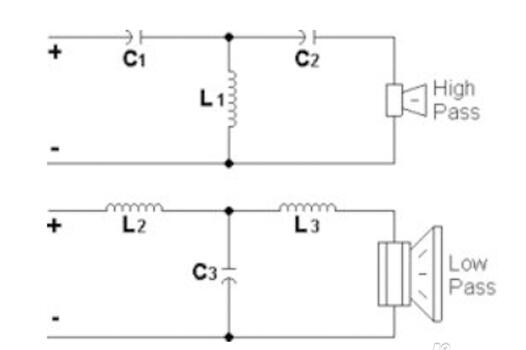

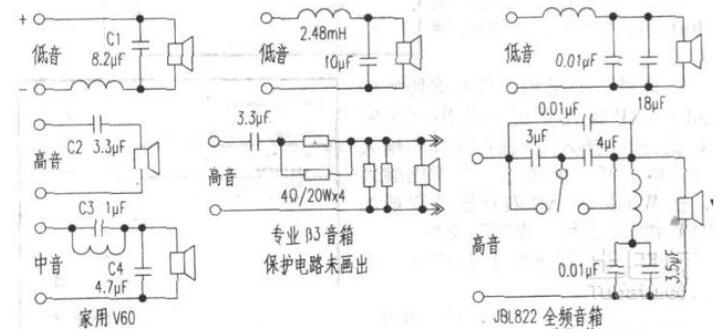

分頻器是一種基本電路,一般包括數字分頻器、模擬分頻器和射頻分頻器。根據不同設計的需要,有時還會要求等占空比。數字分頻器采用的是計數器的原理,權值為分頻系數。模擬分頻器就是一個頻率分配器,用帶阻帶通實現(比如音箱上高中低喇叭的分配器)。射頻分頻器也是濾波器原理,用帶內外衰減,阻抗匹配實現。

隨著FPGA技術的發展,基于FPGA技術的硬件設計數字分頻器已成為數字系統設計的研究重點。數字分頻器通常分為整數分頻器和小數分頻器。在有些需求下還要分數分頻器。

本設計是基于FPGA的數字分頻器,通過VHDL硬件設計語言,在Modelsim6.5上對設計的分頻器進行仿真驗證。

2. 數字分頻器的設計

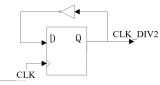

數字分頻器的設計與模擬分頻器的設計不同,數字分頻器可以使用觸發器設計電路對時鐘脈沖進行時鐘分頻。分頻器的一個重要指標就是占空比,即在一個周期中高電平脈沖在整個周期中所占的比例。占空比一般會有1:1,1: N等不同比例的要求,由于占空比的比例要求不一樣,所以采用的時鐘分頻原理也各不同。在FPGA的數字分頻器設計中,主要分為整數分頻器、小數分頻器和分數分頻器。現在分別介紹整數分頻器的設計、小數分頻器的設計和分數分頻器的設計。

2.1 整數分頻器的設計

整數分頻器是指基準時鐘與所需的時鐘頻率成整數倍關系。整數分頻器的分頻種類一般包括奇數分頻和偶數分頻。雖然時鐘分頻原理會根據時鐘分頻的要求不同而不同,但均可采用標準計數器原理來實現。

偶數分頻器的設計原理較為簡單,主要是利用計數器來實現。假設要進行n(n為偶數)分頻,設定一個在分頻時鐘上升沿觸發的計數器循環計數來實現。當計數器值為0-((n/2)-1)時,輸出時鐘信號進行翻轉,同時給計數器一個復位信號,使下一個時鐘上升沿到來時,計數器重新開始計數,由此不斷循環。

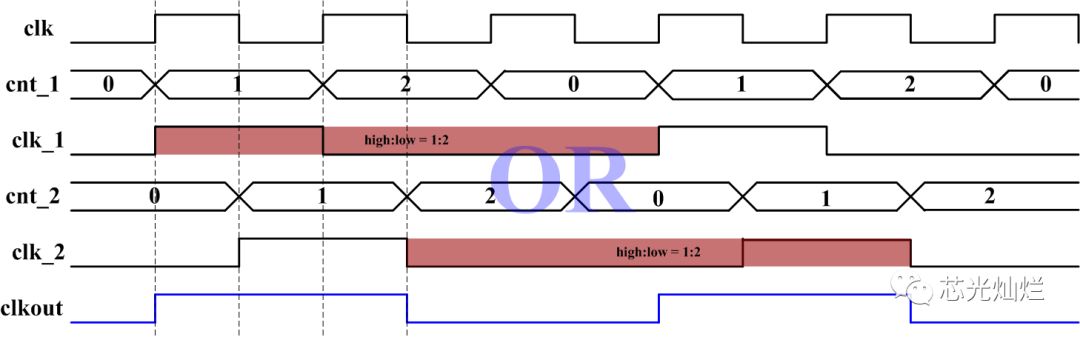

奇數分頻器的設計原理與偶數分頻的設計方法很相似,都是通過計數器來實現的。如果要進行n(n為奇數)分頻,直接設計n進制的計數器即可。還有一種方法就是選擇兩個計數器cnt1和cnt2,分別在時鐘上升沿和下降沿觸發計數。cnt1和cnt2均當計數器值為0-((n/2)-1)時,輸出時鐘信號進行翻轉,同時給計數器一個時鐘復位信號,使下一個時鐘上升沿到來時,計數器重新開始計數,如此進行循環下去。由此可知,計數器cnt1和cnt2的實現方法一樣,只是翻轉邊沿不一樣,最終輸出的時鐘為clkout = clk1 + clk2。

2.2 小數分頻器的設計

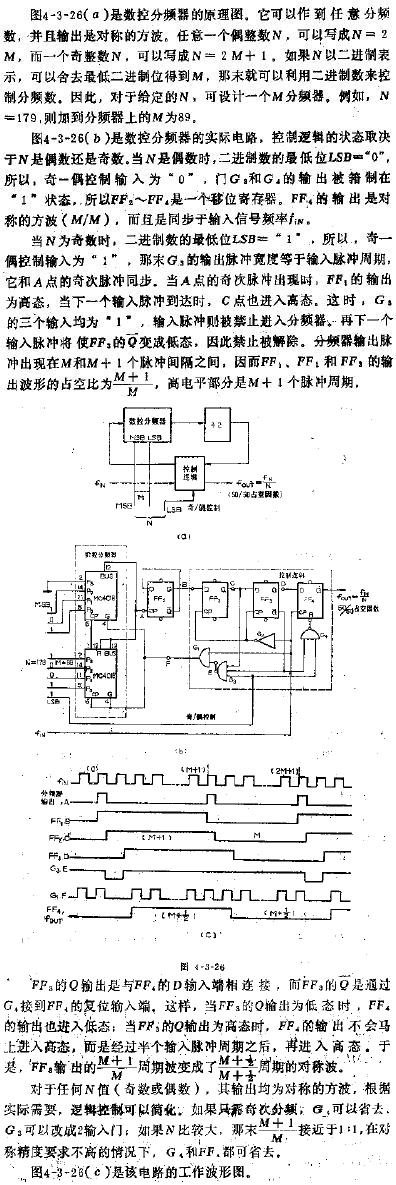

小數分頻的基本原理是采用脈沖吞吐計數器和鎖相環技術先設計兩個不同分頻比的整數分頻器,然后通過控制單位時間內兩種分頻比出現的不同次數來獲得所需的小數分頻值,分頻系數為N-0.5(N為整數)時,可控制扣除脈沖的時間,以使輸出成為一個穩定的脈沖頻率,而不是一次N分頻,一次N-1分頻。

小數分頻器有很多種設計方案,但其基本原理是一樣的,都是在若干個分頻周期中采取某種方法使幾個周期多計一個數或少計一個數,從而在整個計數周期的總體平均意義上獲得一個小數分頻比。還有一種分頻方法就是,利用狀態機和計數器。假設時鐘信號的頻率為1khz,需要產生750khz的分頻信號,其分頻系數為6/8。基本設計思想是,在8個時鐘信號中保留6個時鐘信號。這種方法是需要預先設定狀態機的個數,主要用于已經知道需要使用哪一個小數分頻系數的情況下。如果分頻系數發生變化,則需要在程序內部進行修改。

雙模前置小數分頻的設計方法是,假設要進行m,n時鐘分頻(其中m、n都是整數,且n《10),因為只有一位小數,所以總共要進行10次分頻。總的規律是:進行n次m+1分頻,10-n次m分頻。例如,設計一個分頻系數為3.6的分頻器,將小數部分的6按倍累加,假設累加的值為a,如果a《10,則進行3分頻,如果a《10下一次則加上6。此后,如果a》=10,則進行4分頻,4分頻過后再將累加值減去4后與10比較以決定下一次分頻是4分頻還是3分頻,這樣分頻器設計成6次4分頻,4次3分頻,總的分頻值為(6×4+4×3)/(6+4) = 3.6。

2.3 分數分頻器的設計

分數分頻器的數據輸入部分與小數分頻基本相同,差別僅在于數碼管顯示部分顯示三位分頻系數。由于分數在一定情況下可以轉化為小數進行計算,所以分數分頻的設計思想與小數分頻的很相似。假設進行分頻,總分頻數由分母m決定,規律是進行n次j+1分頻和m-n次j分頻。兩種分頻交替進行的計算方法和小數分頻的很類似。累加分結果是大于等于分母還是小于分母決定是進行j分頻還是j+1分頻。

3. 數字分頻器的FPGA設計及仿真

利用FPGA對8192kHz的基準時鐘進行時鐘分頻,分別得到1024kHz、512kHz、256kHz和1kHz的時鐘頻率,需要分別進行8分頻、16分頻、32分頻和8192分頻。在利用FPGA進行設計整數分頻器時,通過VHDL硬件描述語言利用計數器方式來實現。

3.1 1024kHz時鐘分頻

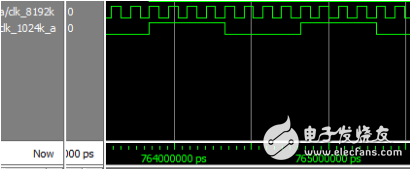

根據所需的時鐘頻率為1024kHz的時鐘,而晶振時鐘的頻率為8192kHz,晶振時鐘與所需的時鐘頻率恰巧是8倍的整數倍關系,因此需要對8192kHz的晶振時鐘進行8分頻來獲得所需要的時鐘。根據整數倍分頻器的設計方法原理,通過ISE9.1邏輯設計工具,利用VHDL硬件描述語言來進行8分頻的分頻器設計。然而8又是偶數,所以需要設計的是偶數分頻器。對設計的內容通過Modelsim6.5仿真軟件進行仿真驗證,結果如圖3-1所示。

圖3-1 1024kHz時鐘分頻

由圖3-1得知,當8192kHz的晶振時鐘輸入8個時鐘,系統輸出1個時鐘,即一個1024kHz頻率的時鐘。程序設計中采用計數器來實現,當計數器值為0-((n/2)-1)=-3時,輸出時鐘信號進行翻轉,同時給計數器一個復位信號,使下一個時鐘上升沿到來時,計數器重新開始計數,不斷循環下去。

3.2 512kHz時鐘分頻

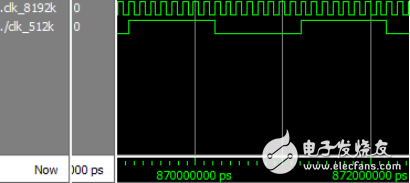

根據所需的時鐘頻率為512kHz的時鐘,而晶振時鐘的頻率為8192kHz,晶振時鐘與所需的時鐘頻率恰巧是16倍的整數倍關系,因此需要對8192kHz的晶振時鐘進行16分頻來獲得所需要的時鐘。根據整數倍分頻器的設計方法原理,通過ISE9.1邏輯設計工具,利用VHDL硬件描述語言來進行16分頻的分頻器設計。然而16又是偶數,所以需要設計的是偶數分頻器。對設計的內容通過Modelsim6.5仿真軟件進行仿真驗證,結果如圖3-2所示。

圖3-2 512kHz時鐘分頻

由圖3-2得知,當8192kHz的晶振時鐘輸入16個時鐘,系統輸出1個時鐘,即一個512kHz頻率的時鐘。程序設計中采用計數器來實現,當計數器值為0-((n/2)-1)=-7時,輸出時鐘信號進行翻轉,同時給計數器一個復位信號,使下一個時鐘上升沿到來時,計數器重新開始計數,不斷循環下去。

3.3 256kHz時鐘分頻

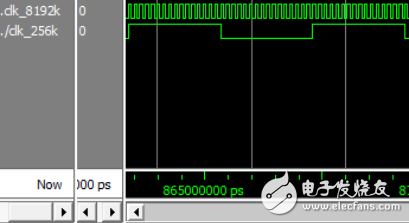

根據所需的時鐘頻率為256kHz的時鐘,而晶振時鐘的頻率為8192kHz,晶振時鐘與所需的時鐘頻率恰巧是32倍的整數倍關系,因此需要對8192kHz的晶振時鐘進行32分頻來獲得所需要的時鐘。根據整數倍分頻器的設計方法原理,通過ISE9.1邏輯設計工具,利用VHDL硬件描述語言來進行32分頻的分頻器設計。然而32又是偶數,所以需要設計的是偶數分頻器。對設計的內容通過Modelsim6.5仿真軟件進行仿真驗證,結果如圖3-3所示。

圖3-3 256kHz時鐘分頻

由圖3-3得知,當8192kHz的晶振時鐘輸入32個時鐘,系統輸出1個時鐘,即一個256kHz頻率的時鐘。程序設計中采用計數器來實現,當計數器值為0-((n/2)-1)=-15時,輸出時鐘信號進行翻轉,同時給計數器一個復位信號,使下一個時鐘上升沿到來時,計數器重新開始計數,不斷循環下去。

3.4 1kHz時鐘分頻

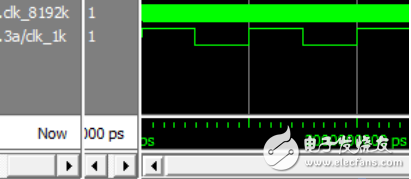

根據所需的時鐘頻率為1kHz的時鐘,而晶振時鐘的頻率為8192kHz,晶振時鐘與所需的時鐘頻率恰巧是8192倍的整數倍關系,因此需要對8192kHz的晶振時鐘進行8192分頻來獲得所需要的時鐘。根據整數倍分頻器的設計方法原理,通過ISE9.1邏輯設計工具,利用VHDL硬件描述語言來進行8192分頻的分頻器設計。然而8192又是偶數,所以需要設計的是偶數分頻器。對設計的內容通過Modelsim6.5仿真軟件進行仿真驗證,結果如圖3-4所示。

圖3-4 1kHz時鐘分頻

由圖3-4得知,當8192kHz的晶振時鐘輸入8個時鐘,系統輸出1個時鐘,即一個1kHz頻率的時鐘。程序設計中采用計數器來實現,當計數器值為0-((n/2)-1)=-4095時,輸出時鐘信號進行翻轉,同時給計數器一個復位信號,使下一個時鐘上升沿到來時,計數器重新開始計數,不斷循環下去。

4. 結束語

本文給出了基于FPGA的數字分頻器設計方法。采用計數器設計方法實現了對8192kHz的基準時鐘進行分頻,分別得到1024kHz、512kHz、256kHz和1kHz的時鐘頻率。其他的偶數倍分頻也可采用類似的方法分頻的到需要的頻率時鐘。通過在Modelsim6.5仿真工具驗證了設計的正確性。

電子發燒友App

電子發燒友App

評論