氮化鎵技術(shù)的不斷進(jìn)步促使設(shè)備在更高的功率、電源電壓和頻率下工作。

圖1、QPD1013 晶體管的照片

如圖1所示,Qorvo的QPD1013晶體管采用0.50 μm GaN-on-SiC技術(shù)。它采用具有成本效益的6.6x7.2 mm DFN(雙邊扁平無引腳)封裝,與傳統(tǒng)的金屬陶瓷封裝相比,可以實(shí)現(xiàn)更簡單的PCB組裝。

盡管Qorvo的GaN晶體管效率非常高,但考慮到高RF功率電平意味著即使是高效的PA,晶體管也將具有顯著功耗。由于晶體管是SMT組件,因此需要仔細(xì)設(shè)計(jì)PCB以優(yōu)化熱性能。已經(jīng)對兩種方法進(jìn)行了評估,并報(bào)告了兩者的結(jié)果。

第一種方法在晶體管的接地焊盤下使用覆銅孔陣列,第二種方法使用銅幣技術(shù)。銅幣是在制造期間嵌入到PCB中的一塊實(shí)心銅(通常稱為金屬塊),以允許從晶體管到安裝了PCB的載體的有效熱傳遞。許多PCB制造商都具有覆銅孔技術(shù)經(jīng)驗(yàn),但射頻頻率下的銅幣技術(shù)還未成熟。

晶體管測量

該設(shè)計(jì)使用以20mil厚度的Rogers RO4350組裝的樣品晶體管的大信號和小信號測量值。晶體管靜態(tài)偏置為65V,240mA。

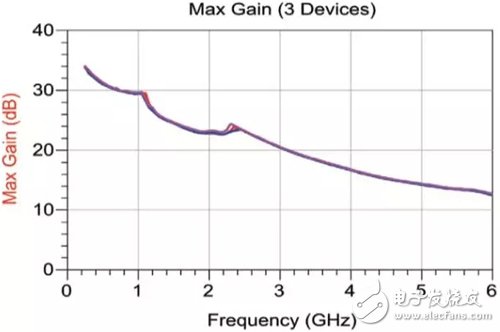

圖2、晶體管MAG與頻率3個(gè)晶體管

圖2 顯示了三個(gè)不同晶體管隨頻率變化的最大可用增益(MAG),這清楚地表明非常好的單元間一致性。雖然QPD1013表現(xiàn)出的增益超過6GHz,但出于實(shí)用性考慮,它最適合在最高約3.5GHz下工作。

最大增益(3 臺設(shè)備)最大增益(dB) 頻率(GHz)

負(fù)載牽引測量值顯示,當(dāng)以10%的占空比和100 μs脈沖寬度工作時(shí),晶體管可提供超過52dBm 160 W) 的RF輸出功率,效率約為70%。此負(fù)載牽引數(shù)據(jù)被用作PA大信號設(shè)計(jì)的基礎(chǔ)。

功率放大器設(shè)計(jì)

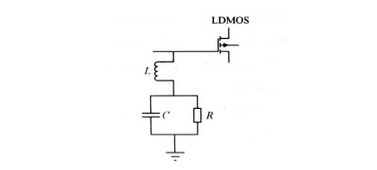

PA設(shè)計(jì)的起點(diǎn)是使晶體管在整個(gè)工作頻段內(nèi)無條件保持穩(wěn)定。必須首先確保帶內(nèi)的穩(wěn)定性,這通過在RF輸入端納入RC穩(wěn)定網(wǎng)絡(luò)來實(shí)現(xiàn)。串聯(lián)電阻消耗的功率對于傳統(tǒng)SMT組件來說過高,所以使用了來自IMS的高功率氮化鋁電阻。放大器需要在-40°C以下的所有頻率中無條件保持穩(wěn)定,以使放大器在較廣的溫度范圍內(nèi)工作。通過在偏置饋電點(diǎn)添加適當(dāng)?shù)腞C去耦(可在設(shè)計(jì)過程中稍后添加),可以大大提高低頻段穩(wěn)定性。

由Qorvo提供的初始負(fù)載牽引數(shù)據(jù)用于確定1.2GHz至1.8GHz之間輸出功率和漏極效率的最佳負(fù)載阻抗。QPD1013在某些負(fù)載條件下可提供高達(dá)200W的功率,但還需要仔細(xì)考慮工作效率,以確保晶體管的工作溫度可以接受。選擇導(dǎo)致最高漏極效率的負(fù)載阻抗作為由輸出匹配網(wǎng)絡(luò)呈現(xiàn)的目標(biāo)阻抗。相應(yīng)的RF輸出功率電平仍然很高,并且更高的效率確保了可接受的熱性能。

輸出匹配網(wǎng)絡(luò)利用帶通拓?fù)鋪頋M足目標(biāo)負(fù)載阻抗。高工作電壓和高RF功率電平對粗心的設(shè)計(jì)師構(gòu)成潛在陷阱。保持RF軌道足夠?qū)捯员苊庥捎诜浅8叩腞F功率電平引起的溫度過高和潛在破壞,這非常重要。必須仔細(xì)選擇匹配電容以具有足夠的擊穿電壓,從而承受具有足量Q的直流加RF電壓擺幅,以避免過多的功耗和效率降低。

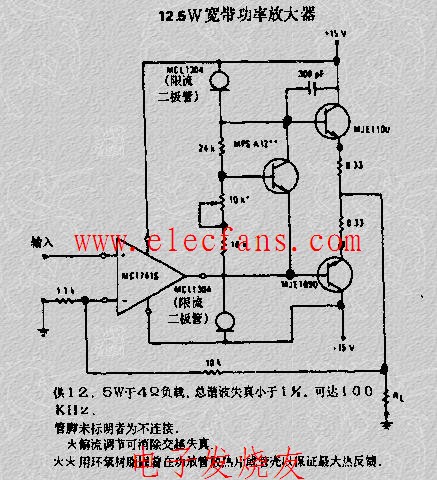

使用Keysight Momentum對輸出匹配網(wǎng)絡(luò)的金屬件進(jìn)行平面EM仿真,并結(jié)合O805 SMT組件的嵌入式高頻模型模擬多端口S參數(shù)塊。圖3 顯示了輸出匹配網(wǎng)絡(luò)電路的混合EM/原理圖。

圖3、EM 模擬輸出匹配

圖4、目標(biāo)(虛線)到模擬(實(shí)線)負(fù)載阻抗,10 Ω圖

模擬負(fù)載阻抗針對圖4中標(biāo)準(zhǔn)化為10 Ω的史密斯圓圖上的目標(biāo)進(jìn)行繪制。在提供的負(fù)載牽引輪廓(未示出)上覆蓋模擬負(fù)載曲線,表明將滿足目標(biāo)功率和效率值。

S(3,3) QPD1013_Opt_Zload_v1..S(1,1)

頻率(1.200GHz 至1.9000GHz)

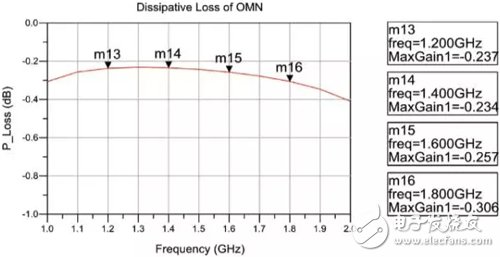

輸出網(wǎng)絡(luò)的模擬插入損耗如圖5 所示。

圖5、輸出網(wǎng)絡(luò)的模擬插入損耗

輸出匹配網(wǎng)絡(luò)損耗來自PCB介質(zhì)中的傳輸線損耗和SMT組件損耗。在這些輸出功率電平下,即使是零點(diǎn)幾dB的損耗也將達(dá)到幾瓦特的耗散功率,這顯著降低了總體PA效率。

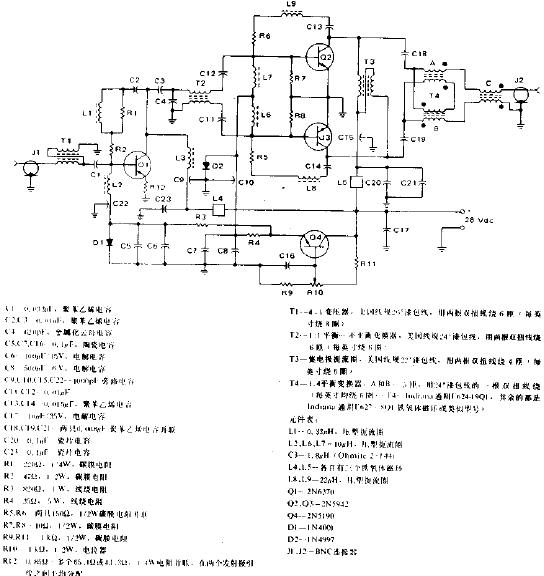

圖6、EM模擬輸入匹配

輸入匹配網(wǎng)絡(luò)采用低通架構(gòu)。IMS氮化鋁電阻用于柵極穩(wěn)定性網(wǎng)絡(luò)。這些可以消耗幾瓦的功率,這使得PA能夠承受在P-3dB壓縮下操作PA所需的10至20W的高輸入驅(qū)動電平。圖6顯示了輸入匹配網(wǎng)絡(luò),其模擬方式與輸出匹配網(wǎng)絡(luò)相同。

可以看出,輸入和輸出匹配網(wǎng)絡(luò)的布局都包括感應(yīng)回路和焊盤,以便在制造后調(diào)整PA性能。最后,這些都是不需要的,而唯一的制造后修改是對電容值的小改動。

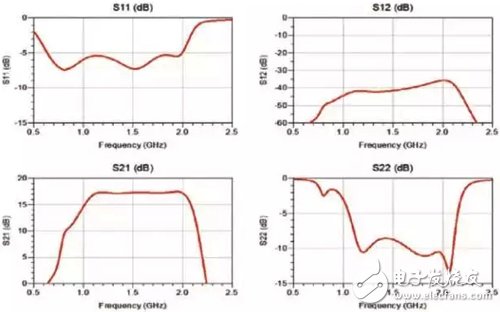

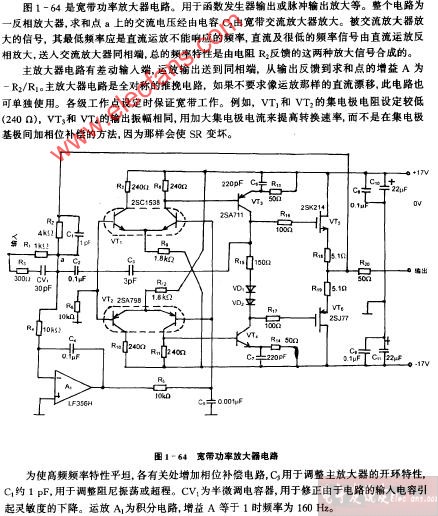

PA的模擬小信號性能如圖7所示。說明了寬帶寬和平坦增益與頻率響應(yīng)。

圖7、模擬的小信號性能

熱考量

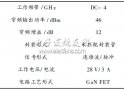

氮化鎵比LDMOS或GaAs具有更高的功率密度。這樣的結(jié)果是耗散功率需要從封裝中有效去除,以便保持足夠低的結(jié)溫,并確保較長的晶體管壽命。

封裝的主要傳熱機(jī)制是通過芯片貼裝板進(jìn)入PCB。PCB的精心設(shè)計(jì)對于確保向環(huán)境的良好熱傳遞至關(guān)重要,因此將晶體管溫度保持在適當(dāng)?shù)牡退健T诠ぷ髦性u估了兩種實(shí)際方法,一種方法使用覆銅孔陣列(如圖8右側(cè)所示), 另一種方法使用裝配到PCB中的銅幣(如圖8左側(cè)所示)。在這兩種情況下,PCB都安裝在了鋁載體上。

圖8、銅幣(左)和覆銅孔(右)

實(shí)現(xiàn)與測量的性能

圖9顯示了一個(gè)完全組裝的功率放大器的照片。鋁載體前面的孔允許將熱電偶直接放置在QPD1013晶體管的正下方。

圖9、制造的PA的照片

使用覆銅孔和銅幣技術(shù)制造PA。在這兩種情況下測量的RF性能非常相似;但與覆銅孔PCB相比,在使用工作溫度低于10°C的晶體管時(shí),銅幣提供了更高的熱性能。除非另有說明,否則下面給出的結(jié)果屬于PCB覆銅孔版。

小信號測量

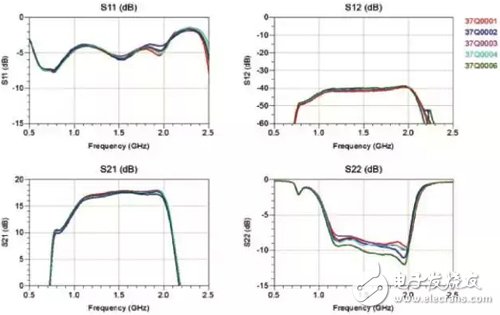

圖10、在25℃下測量的5個(gè)PA的S參數(shù)

圖10 繪出了25°C(晶體管基礎(chǔ)溫度)下5個(gè)PA的小信號S參數(shù)。特別值得注意的是,整個(gè)工作頻段的增益平坦度和模擬與測量之間的良好一致性。所有四張圖顯示了測量的PCB范圍內(nèi)的一致性。

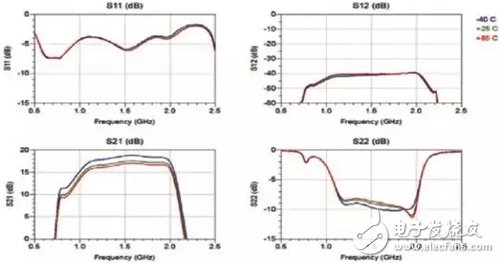

圖11、一個(gè)PA隨溫度變化測量的S參數(shù)

圖11繪出了一個(gè)PA隨溫度變化的小信號性能。相對于25°C下的測量值,測量的S21在-40°C時(shí)約為1 dB,在85°C時(shí)約為0.5dB。

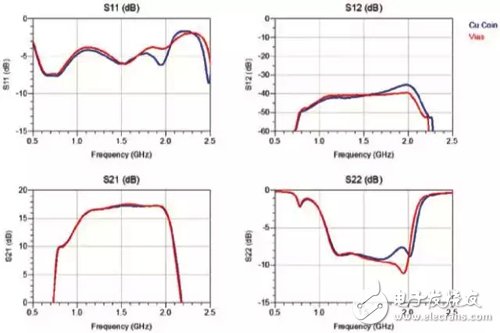

圖12、覆銅孔PCB與銅幣PCB的S參數(shù)比較

圖12顯示了使用覆銅孔和使用銅幣PCB技術(shù)的PA小信號性能的比較。可以看出,RF性能非常相似,而且在大信號性能中也觀察到了這點(diǎn)。

大信號測量

測量了多個(gè)PA隨溫度變化的功率傳遞特點(diǎn)。單元間的性能非常相似,采用覆銅孔PCB 獲得的性能與使用銅幣技術(shù)的PA獲得的性能相似。

圖13、在P-3dB下,測量的不同溫度的RF輸出

圖13繪出了一個(gè)PA在三個(gè)不同溫度下的典型性能,從中可以看出,頻段高端的最小輸出為100 W,頻段低端的最小輸出為160W。

圖14、在P-3dB下,測量的不同溫度的效率

圖14 顯示PA輸出的典型效率為55%,其中包括輸出匹配網(wǎng)絡(luò)和連接器損耗。雖然PA的效率令人印象深刻,但耗散功率仍可以超過100W,突顯出需要有效的熱解決方案。

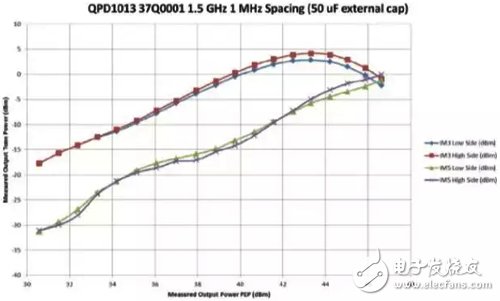

圖15、雙音互調(diào)產(chǎn)品

此外,還測量了PA的雙音互調(diào)性能。圖15 繪出了典型放大器與輸出功率的三階和五階產(chǎn)品的電平。對于10W (40 dBm) 的總RF輸出功率,輸出IP3約為+60 dBm。

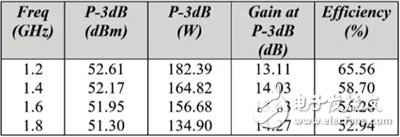

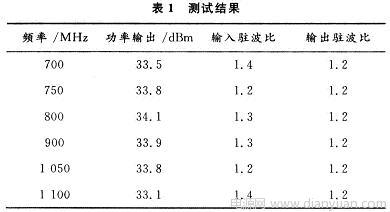

表1、測量的性能總結(jié)

結(jié)論

本文介紹了使用市售SMT晶體管(Qorvo的QPD1013)的GaN PA的設(shè)計(jì)與實(shí)現(xiàn)。該放大器覆蓋1.2至1.8 GHz的頻段,并提供約160W的RF輸出功率,效率約為60%。放大器與頻率的關(guān)鍵性能數(shù)據(jù)列于表1。

與所有功率晶體管一樣,謹(jǐn)慎的熱設(shè)計(jì)是可靠運(yùn)行的關(guān)鍵。使用兩種不同的PCB方法(覆銅孔陣列和嵌入式銅幣)制造并評估了PA的不同版本,以確保良好的熱性能。這兩種情況下的RF性能非常相似。使用銅幣PCB導(dǎo)致通道溫度降低10°C。

雖然銅幣PCB實(shí)現(xiàn)的熱阻抗改進(jìn)很有吸引力,但必須高度注意以確保PCB的表面保持平坦,并在銅幣和DFN的接地焊盤之間形成良好的接觸。任何氣隙或焊縫都可能會削減銅幣方法的內(nèi)在優(yōu)勢。

電子發(fā)燒友App

電子發(fā)燒友App

評論