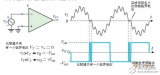

隨著數字集成電路規模的不斷擴大及功能的增強,數字電子技術作為一門專業技術基礎課程,顯得更加重要。對觸發器的描述有特性表、特性方程式、狀態轉換圖,而觸發器的電壓波形圖既是重點又是難點。例如基本RS觸發器。同步RS觸發器中的不定態和主從型RS觸發器的不定態有何不同,主從型RS觸發器和主從型JK觸發器的動作特點又是什么。下面就從電壓波形圖來對RS和JK觸發器進行分析。RS觸發器的狀態轉換圖如圖l所示。JK觸發器的狀態轉換圖如圖2所示。

觸發器的電路結構和邏輯功能的關系

一、邏輯功能指觸發器的次態和現態及輸入信號之間在穩態下的邏輯關系,

可用特性表、特性方程或狀態轉換圖表示。

分類:RS觸發器、JK觸發器、D觸發器、T觸發器、T/觸發器等。

二、電路結構形式不同,動作特點不同。

分類:基本TS觸發器、同步RS觸發器、主從觸發器、邊沿觸發器等。

三、同一邏輯功能的觸發器可用不同的電路結構實現;

同一電路結構形式可作成不同邏輯功能的觸發器。

即:邏輯功能與電路結構無固定對應關系。

四、邏輯功能相同而電路結構不同,則是在狀態翻轉時動作特點不同。

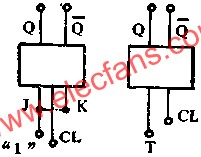

五、JK觸發器包含了RS觸發器和T觸發器的所有邏輯功能。

目前生產的時鐘控制觸發器定型產品只有JK觸發器和D觸發器兩大類。

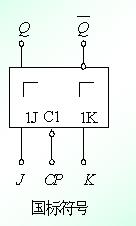

JK觸發器中

1、令J=S,K=R且J、K不同時為1,約束條件SR=0,構成RS觸發器。

2、令J=K=T,則為T觸發器。

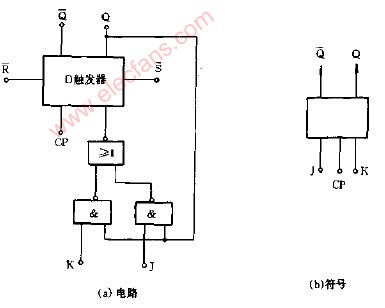

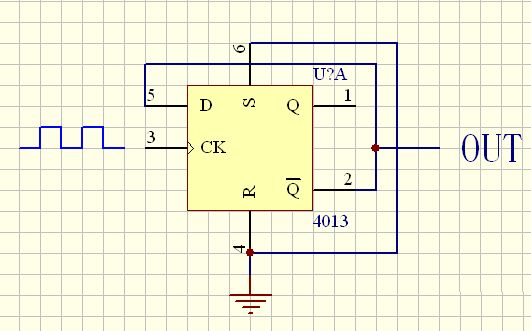

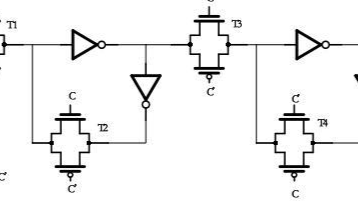

用D觸發器構成JK觸發器

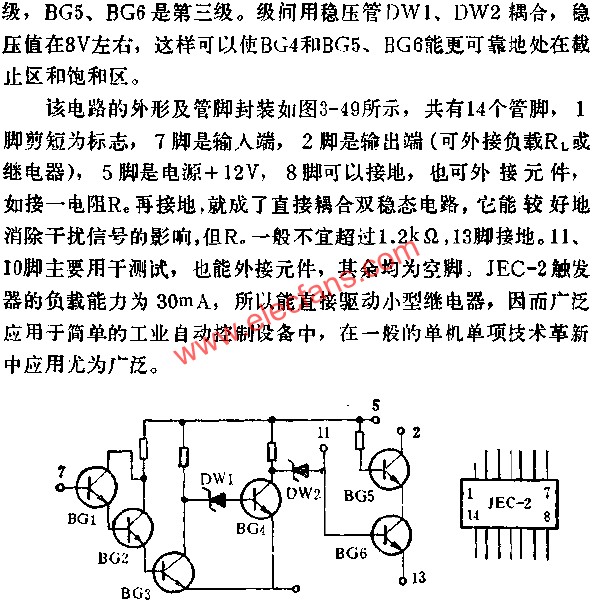

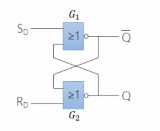

RS觸發器電路分析

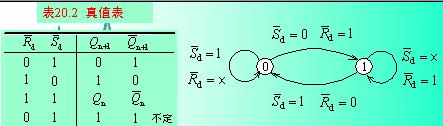

RS觸發器的特性由特性表和狀態轉換圖可知,當S=R=1時,其狀態均為不定態,而不同電路結構的觸發器,其動作特點是有區分的。

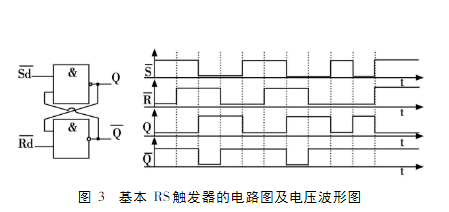

1.1 基本RS觸發器

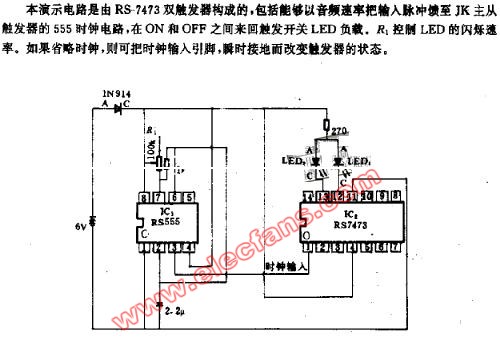

基本RS觸發器的電路圖及電壓波形圖如圖3所示。

根據對基本RS觸發器電路的分析得知:當SD=RD=0時,Q、均為高電平,一且SD、RD同時變為高電平,Q、輸出為O,1(或1,0)無法確定。也就是說當SD=RD=0時,Q和輸出端的狀態是確定的,即為1,狀態不定是指當SD、RD同時從0變成1后,Q、輸出端的狀態不確定(Q= 1,=0,還是Q=0,=1,不能確定)。

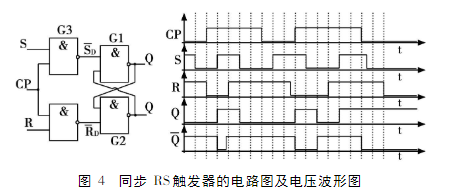

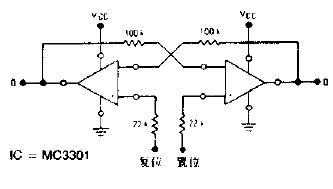

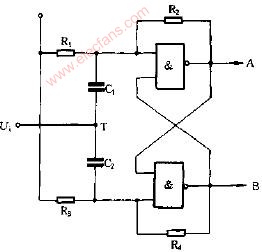

1.2 同步RS觸發器

同步RS觸發器的電路圖及電壓波形圖如圖4所示。

根據對同步RS觸發器電路的分析得知:CP=0時,S=X,R=X,Q、輸出端保持不變;CP=1時,其工作情況同基本RS觸發器一樣(設Q初態為0)。

CP=1期間,S=R=1,Q和輸出同時為高電平1,一旦CP從高電平變為低電平,Q、輸出端的狀態同樣是不定的(即可能Q=0,=1,也可能Q=1,=0)。其輸出狀態是隨機的,無法確定。

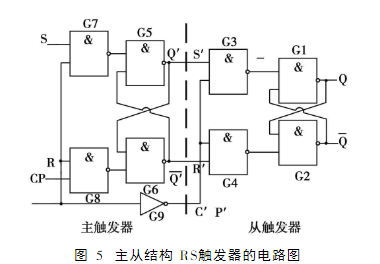

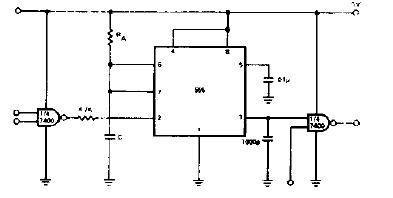

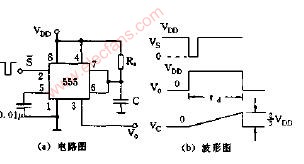

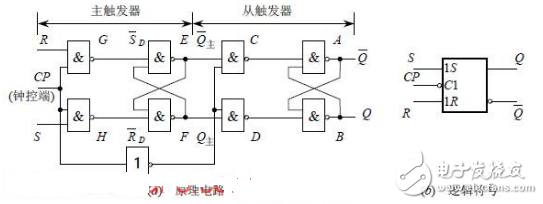

1.3 主從結構RS觸發器

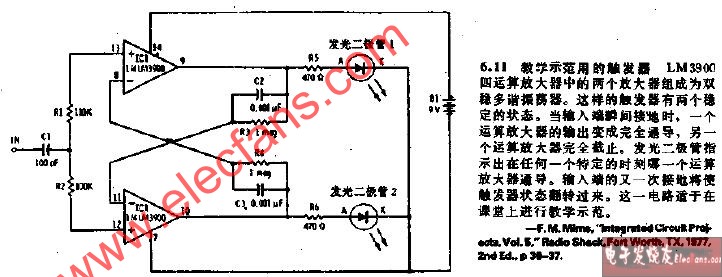

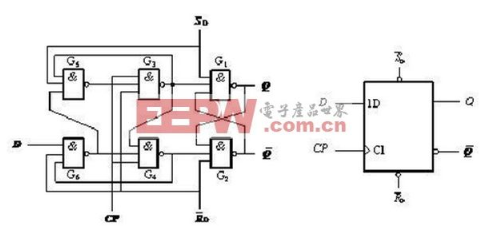

主從結構RS觸發器的電路圖如圖5所示,由主觸發器和從觸發器組成。

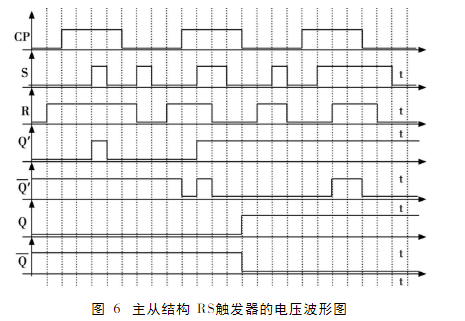

主、從觸發器分別由兩個同步RS觸發器組成。根據對主從型RS觸發器電路的分新,畫出其相應的電壓波形圖,主從結構RS觸發器的電壓波形圖如圖6所示(設初態為0)。

CP=1時,主觸發器觸發工作,從觸發器的Q、輸出端保持不變;CP=O時,從觸發器觸發工作,主觸發器的Q’、輸出端保持不變。輸出端輸出狀態的變化發生在CP信號的下降沿,但卻是受到CP=1期間R、S輸入信號的影響。圖4中的脈沖3,CP=1,S=R=1時,Q’==1,且持續到CP下降沿時刻,則Q’=0,=1,還是Q‘=1,=0不確定。所以當CP下降沿時刻一到從觸發器Q端輸出高電平還是低電平無法確定,其狀態不定,并不是指Q、同時輸出高電平,和基本RS、同步RS觸發器的理解不同。

通過對電路的分析總結出主從型RS觸發器Q端電壓波形變化的描述方法。

從觸發器是按照CP下降沿時刻到這一時刻主觸發器輸出端Q’、的信號觸發工作。即Q’=1,=0,則Q=1,=0;Q‘=0,=1,則Q=0,=1。所以不需要對CP=1期間,主觸發器Q’、的信號全部分析出來。可以在每個CP脈沖下降沿到來這一刻往前去確定Q’、,一旦明確知道Q’、的信號,就不需要知道前面Q‘、的信號,即知道CP下降沿這一時刻的Q’、的信號,則CP下降沿時刻一到,從觸發器的輸出也明確了。

圖4中脈沖1下降沿t2時刻到,如何判斷Q端的信號?由于t1-t2期間S=O,R=1,主觸發器量0,即Q’=0,=1,所以t2時刻一到,Q=Q’=0,==1,不需要對t1之前的信號再進行詳細分析。

同理脈沖2下降沿t5時刻到,由于t4-t5期間,S=R=O。主觸發器處于保持狀態,而Q’、保持什么狀態不清楚,再看t3-t4期間,S=1,R=0,主觸發器置1,使Q’=1,=0,由此可知t4-t5期間主觸發器保持1狀態,所以在t5時刻一到Q=Q’=1,==0。

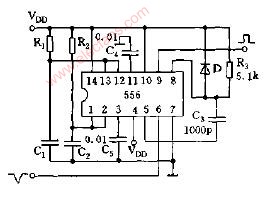

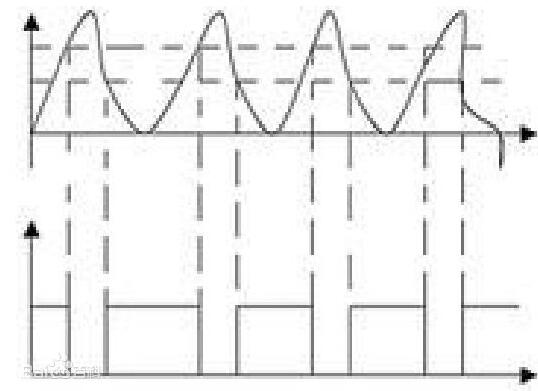

2 JK觸發器電路分析

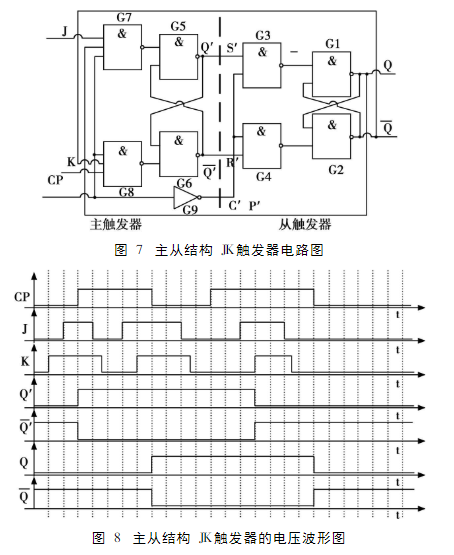

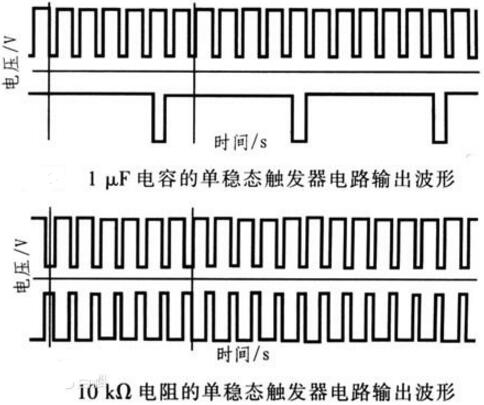

主從結構JK觸發器和主從結構RS觸發器區別在于當J=K=1時,觸發器將翻轉為與初始狀態相反的狀態,所以JK觸發器不再存在輸出狀態不定的情況。主從結構JK觸發器電路圖如圖7所示。圖8為主從結構JK觸發器的電壓波形圖(設初態為0)。

脈沖1:當CP=1時,t1-t2期間J=K=1,Q’取反,由原來的0取反為1。主觸發器的狀態改變了一次不會再翻轉回來,所以t2-t3期間,盡管j、k輸入端的信號發生變化,卻不用再詳細分析,t3下降沿時刻一到,從觸發器Q端亦從0翻轉到1。脈沖2:當CP=1時,t4-t5期間,J=K=0,為保持不變狀態,狀態沒有變化,故需要對下一時間段進行分析,t5-t6期間,J=1,K=O,主觸發器量1,而原狀態就為1,狀態沒有發生改變,所以還需對下一時間段進行判定,t6時刻一到,J=K=1,主觸發器輸出狀態,取反為0,由于主觸發器的狀態只能改變一次,所以不需要再分析后面的時間段,下降沿t7時刻一到,從觸發器跟從主觸發器—樣輸出低電平。

3 電壓波形圖

通過對不同電路結構觸發器電壓波形圖的分析,發現僅了解觸發器的特性表,特性方程式,狀態轉換圖是不夠的,還需理解其電路結構才能真正掌握觸發器電路。并由此得到主從型RS觸發器和主從型JK觸發器電壓波形圖的描繪方法。

主從型RS觸發器:判斷每個CP下降沿時刻到時狀態的變化,是自這一時刻起自后往前判定,CP=1期間,主觸發器的狀態,一旦主觸發器的狀態明確了,就不需再往前判定主觸發器的狀態,該狀態即為CP下降沿到時主觸發器的狀態,而從觸發器在CP下降沿時刻一到跟隨主觸發器的狀態變化即可。

主從型JK觸發器:判斷每個CP下降沿到時輸出狀態的變化,是從CP為高電平開始(即上升沿這一時刻)根據J、K輸入端的信號變化自前往后分時間段判定主觸發器的狀態,—旦狀態變化了一次,就不需要再分析后面的輸入信號,因為CP=1期間,主觸發器的狀態只能改變一次,此狀態維持到CP下降沿到時,從觸發器跟隨主觸發器的狀態而變化。

4 結束語

觸發器作為構成數字系統的一種基本邏輯單元,由于其不同的電路結構帶來不同動作特點,在電路設計和使用時,須區分使用。而在介紹觸發器這一章時,由于是從組合邏輯問題過渡到時序邏輯問題,對觸發器電路的分析及描述方法和組合邏輯電路不同,故需對不同電路結構的觸發器,在分析其電路結構的基礎上,總結出其動作特點和規律,以便正確掌握和使用觸發器。

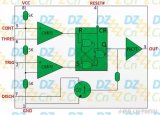

在實際的電路中,一般使用觸發器,通過時鐘脈沖進行控制,用得最多的時D觸發器和J-K觸發器;觸發器能保證一個脈沖內的信號穩定。當然,也存在其它類型的觸發器(如T觸發器和T’觸發器等)。

觸發器和組合電路中的譯碼器、編碼器、選擇器、分配器等組合在一起能構成所有我們需要的電路,這也是后續課程如計算機組成原理和嵌入式等課程的基礎,牢記并理解組合電路和典型觸發器的功能特性是進行后續課程學習保證。

電子發燒友App

電子發燒友App

評論