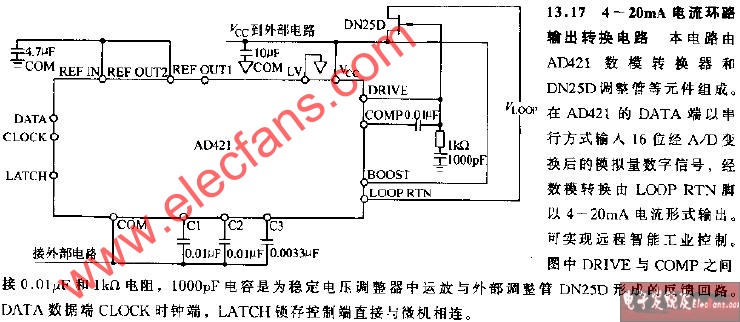

AD420是一款完整的數字至電流環路輸出轉換器,旨在滿足工業控制的需要市場。它提供高精度,完全集成,低成本用于產生電流回路信號的單芯片解決方案,緊湊型24引腳SOIC或PDIP封裝。輸出電流范圍可編程為4 mA至20 mA,0 mA至20 mA或0 mA至超量程功能24毫安。

AD420也可以提供電壓輸出從一個可配置為提供0 V至5 V的獨立引腳,0 V至10 V,±5 V或±10 V,增加一個外部電阻緩沖放大器。3.3 M波特串行輸入邏輯設計最大限度地降低了成本電流隔離,通常可以簡單連接使用過的微處理器。它可以用于3線或異步模式和串行輸出引腳用于允許菊花鏈接隔離柵的電流回路側有多個DAC。

AD420采用sigma-delta(Σ-Δ)DAC技術實現16位單調性,成本極低。全面結算至0.1%發生在3毫秒內。唯一的外部組件要求(除了正常的瞬態保護電路)兩個低成本電容器用于DAC輸出濾波器。如果AD420在極端溫度和電源下使用電壓,外部輸出晶體管可用于最小化

通過BOOST引腳在芯片上實現功耗。錯誤當環路中發生開路時,DETECT引腳發出信號。

片上電壓參考可用于提供精度除AD420外,還可以向外部元件施加+ 5V電壓用戶希望溫度穩定性超過25 ppm /°C,a外部精密基準電壓源如AD586可用作參考資料。

AD420采用24引腳SOIC和PDIP工作溫度范圍為-40°C至+ 85°C。

特征:

4 mA-20 mA,0 mA-20 mA或0 mA-24 mA電流輸出、16位分辨率和單調性

±0.012%最大積分非線性

±0.05%最大偏移(可修剪)

±0.15%最大總輸出誤差(可微調)

靈活的串行數字接口(3.3 MBPS)

片上環路故障檢測

片上5 V基準電壓(最大25 ppm /°C)

異步CLEAR功能

最大供電范圍為32 V.

輸出環路符合0 V至VCC - 2.75 V

24引腳SOIC和PDIP封裝

功能框圖

產品亮點:

1. AD420是一款單芯片解決方案,可產生4 mA電流控制器端的20 mA或0 mA至20 mA信號當前循環。

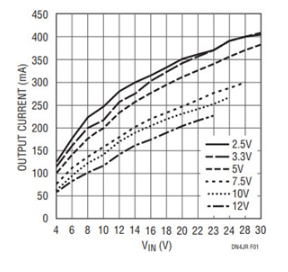

2. AD420的電源范圍為12 V至32 V.輸出環路兼容性為0 V至VCC - 2.75 V.

3.靈活的串行輸入可用于3線模式使用SPI?或MICROWIRE?微控制器,或使用異步模式,最小化數量需要控制信號。

4.串行數據輸出引腳可用于任何菊花鏈AD420的數量在3線模式下一起使用。

5.上電時,AD420將其輸出初始化為低電平所選范圍的結束。

6. AD420有一個異步CLEAR引腳,可以發送輸出到所選范圍的低端(0 mA,4 mA,或0 V)。

7. AD420 BOOST引腳可容納外部引腳晶體管可以降低芯片的功耗。

8.偏移量為±0.05%,總輸出誤差為±0.15%如果需要,可以使用兩個外部電位計進行修整。

引腳配置和功能描述

1、VLL輔助緩沖+4.5 V數字邏輯電壓。該引腳是數字的內部電源電壓電路,可用作上拉電阻的終端。外接+5 V電源即可連接到VLL。它將覆蓋此緩沖電壓,從而降低內部功耗。該應使用0.1μF電容將VLL引腳去耦至GND。請參閱電源和去耦部分。

2、故障檢測故障檢測連接到上拉電阻,當輸出電流不匹配時置為低電平DAC的編程值,例如,在電流環斷開的情況下。

3、RANGE SELECT 2選擇轉換器的輸出操作范圍。一個輸出電壓范圍和三個

4、RANGE SELECT 1輸出電流范圍可用。

5、CLEAR有效VIH無條件強制輸出達到其編程范圍的最小值。 CLEAR之后移除DAC輸出將保持此值。輸入寄存器中的數據不受影響。

6、LATCH在3線接口模式下,上升沿并行將串行輸入寄存器數據加載到DAC中。至使用異步式通過限流電阻將LATCH連接到VCC。

7、時鐘數據時鐘輸入。時鐘周期等于3線接口模式下的輸入數據比特率異步模式下比特率的16倍。

8、串行數據輸入數據。

9、DATA OUT串行數據輸出。在3線接口模式下,此輸出可用于菊花鏈多路復用AD420s。在異步模式下,正脈沖將指示停止位后的幀錯誤接收。

數字線路上的三線接口快速邊緣INPUT其中一個串行輸入具有快速上升沿(《100 ns)

(CLOCK,DATA IN,LATCH)而另一個輸入為邏輯高電平,該部分可能被觸發進入測試模式和內容數據寄存器可能會損壞,這可能會導致輸出加載的值不正確。 如果是快速邊緣預計在數字輸入線上,建議使用在串行加載DAC期間,鎖存線保持在邏輯0。同樣,在更新期間,時鐘線應保持低電平DAC通過鎖存引腳。 或者,添加小數字線上的電容值將減慢邊沿。

異步接口

請注意,在異步模式操作的時序圖中,每個數據字由START(0)位和STOP幀構成(1)位。 數據時序是相對于上升沿的CLOCK位于每個位單元的中心。 位單元是16個時鐘long,第一個單元(START位)從第一個時鐘開始跟隨START位的前沿(下降沿)。 就這樣MSB(D15)在開始后24個時鐘周期采樣START位,D14在時鐘編號40采樣,依此類推。在寫下一個字DATA之前的任何死區時間IN引腳必須保持在邏輯1。當接收到STOP位時,DAC輸出會更新。 在幀錯誤的情況(STOP位采樣為0)AD420將在DATA OUT引腳輸出一個時鐘脈沖采樣后的時鐘周期內的周期寬STOP位。如果成幀,DAC輸出將不會更新檢測到錯誤。

解析度:對于16位分辨率,1 LSB = FSR的0.0015%。在里面4 mA-20 mA范圍1 LSB = 244 nA。積分非線性ADI公司將積分非線性定義為最大值實際調整后的DAC輸出偏離理想值模擬輸出(從0到FS的直線 - 1 LSB)任何位組合。這也稱為相對準確度。

微分非線性:微分非線性是衡量變化的指標模擬輸出,歸一化到滿量程,與LSB相關聯更改數字輸入代碼。單調行為需要差分線性誤差大于-1 LSB感興趣的溫度范圍。

單調性:如果輸出增加或保持,則DAC是單調的恒定增加數字輸入,結果是輸出將始終是輸入的單值函數。

增益錯誤:增益誤差衡量理想值之間的輸出誤差DAC和實際設備輸出,在偏移后加載全1錯誤已經調整出來。

偏移誤差:失調誤差是輸出電流與理想值的偏差值表示為滿量程輸出的百分比在DAC中加載0。

漂移:漂移是參數(例如增益和偏移)的變化指定的溫度范圍。漂移溫度系數,以ppm /°C表示,通過測量參數計算得出在TMIN,25°C和TMAX并除以其中的變化參數由相應的溫度變化。

電流環路電壓符合性:電壓兼容性是IOUT引腳的最大電壓輸出電流將等于編程值。

運作理論

AD420采用sigma-delta(Σ-Δ)架構來實現數模轉換。這種架構尤其如此非常適合相對較低的帶寬要求工業控制環境因其固有的特點高分辨率的單調性。

在AD420中,二階調制器用于將復雜性和芯片尺寸降至最低。來自的單比特流調制器控制一個開關電流源由兩個連續時間電阻器 - 電容器部分濾波。電容器是唯一必須的外部元件添加了標準的電流輸出操作。濾波后的電流被放大并鏡像到供電軌以便應用只需看到4 mA-20 mA,0 mA-20 mA或0 mA-24 mA相對于地的電流源輸出。 AD420采用BiCMOS工藝制造,非常適合實現高性能的低壓數字邏輯和高壓模擬電路。

AD420還可以提供電壓輸出而不是電流如果需要,循環輸出。增加了一個外部放大器允許用戶獲得0 V-5 V,0 V-10 V,±5 V或±10 V.

AD420具有一個環路故障檢測電路,可以發出警告IOUT的電壓試圖超過合規范圍開環電路或電源電壓不足。該故障檢測是一個有效的低開漏信號,因此一個可以將幾個AD420連接到一個上拉電阻全局錯誤檢測。上拉電阻可以連接到VLL引腳或外部+5 V邏輯電源。IOUT電流由PMOS晶體管控制內部放大器如功能框圖所示。產生故障輸出的內部電路避免了使用具有窗口限制的比較器,因為這需要FAULT DETECT輸出之前的實際輸出錯誤變得活躍。相反,當信號產生時AD420輸出級的內部放大器小于剩余約1伏的驅動能力何時輸出PMOS晶體管的柵極幾乎到達地。因此,FAULT DETECT輸出會在之前稍微激活達到合規限制。由于進行了比較在輸出放大器的反饋回路內,輸出通過開環增益保持精度,無輸出在故障檢測輸出變為活動狀態之前發生錯誤。3線數字接口,包括DATA IN,CLOCK,和LATCH,連接所有常用的串行微處理器,無需添加任何外部膠水邏輯。數據是在CLOCK的控制下加載到輸入寄存器中

當選通LATCH時加載到DAC。如果用戶想要從本質上減少電流隔離器的數量安全應用,AD420可配置為運行異步模式。通過連接選擇此模式通過限流電阻將LATCH引腳連接至VCC。數據

然后必須與開始和停止位組合以構建幀信息并觸發內部LATCH信號。

AD420可提供4 mA-20 mA,0 mA-20 mA或0 mA-24 mA輸出,無任何有源外部元件。過濾電容器C1和C2可以是任何類型的低成本陶瓷電容。為滿足3 ms的指定滿量程建立時間,需要低介電吸收電容(NPO)。合適的值是C1 =0.01μF和C2 =0.01μF。

標準配置圖

驅動感應負荷

驅動電感或定義不明確的負載時,請連接0.01μFIOUT(引腳18)和GND(引腳11)之間的電容。這確保了AD420的穩定性,負載超過50 mH。沒有最大電容限制。電容元件加載可能導致較慢的穩定,但這可能會被掩蓋AD420的建立時間。程序化的變化電流可能會導致輸出端產生反電動勢電壓超出AD420的合規性。為了防止這種電壓從超過供電軌連接保護二極管

IOUT與每個VCC和GND之間。

電壓模式輸出

由于AD420是單電源器件,因此需要添加一個外部緩沖放大器到VOUT引腳以獲得選擇雙極性輸出電壓范圍如下圖所示。

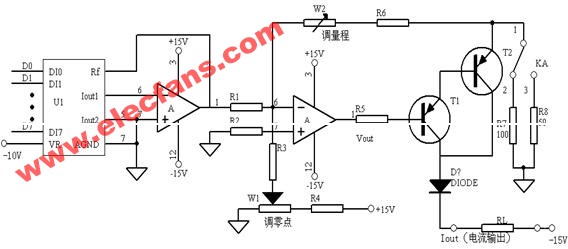

可選的跨度和零修剪

對于希望低于指定值的用戶偏移和增益誤差,下圖顯示了一種修剪這些的簡單方法參數。應注意選擇低漂移電阻因為它們會影響溫度漂移性能DAC。調整算法是迭代的。程序在4 mA-20 mA模式下調整AD420即可

完成如下:

1.偏移調整。加載全零。調整RZERO4.00000 mA輸出電流。

2.增益調整。加載所有。調整RSPAN為19.99976 mA(FS - 1 LSB)輸出電流。返回步驟I并迭代直到獲得收斂。

REF OUT(5 V)和GND引線之間的RZERO變化偏移調節范圍為-1.5 mA至6 mA(1.5 mA / V.

以1 V為中心。5kΩRSPAN2電阻與電阻并聯內部40 W感應電阻,導致增益增加+ 0.8%。當RSPAN變為500Ω時,REF IN上的電壓為通過RSPAN和30kΩREFIN的組合衰減輸入電阻。與RSPAN2一起添加時結果調整范圍為-0.8%至+ 0.8%。

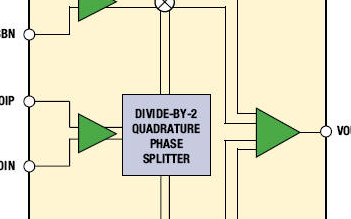

三線接口

下圖顯示了采用3線接口連接的AD420模式。AD420數據輸入模塊包含一個串行輸入移位寄存器和并行鎖存器。移位寄存器的內容由DATA IN信號和上升沿控制時鐘。根據LATCH引腳的請求,DAC和內部鎖存器從移位寄存器并行輸出更新。該更新DAC時,CLOCK應保持不活動狀態。

使用具有故障檢測的多個DAC3線接口模式可以使用串行數據輸出輕松連接多個DAC。對兩個AD420進行編程上圖中,需要32個數據位。前16位是時鐘控制的進入DAC1的輸入移位寄存器。接下來的16位發送通過DATA OUT引腳的前16位DAC1到DAC2的輸入寄存器。輸入移位寄存器兩個DAC作為單個32位移位寄存器工作,具有前導16位表示DAC2和DAC2的信息尾隨16位用于DAC1。 然后更新每個DAC根據LATCH引腳的要求。菊花鏈可以根據需要擴展到盡可能多的DAC。

異步接口使用

光電耦合器AD420以異步接口模式連接光耦合器如下圖所示。異步操作最小化隔離所需的控制信號的數量來自控制回路的數字系統。連接電阻器需要在LATCH引腳和VCC之間激活它模式。對于VCC低于18 V的操作,請使用50kΩ上拉電阻電阻器;從18 V到32 V,使用100kΩ。

異步模式要求時鐘以16倍的速度運行因此,數據比特率以最大輸入數據速率運行在150 kBPS時,需要2.4 MHz的輸入時鐘。實際上實現的數據速率可能受光耦合器類型的限制選擇。可以進一步減少控制信號的數量通過在電流回路上創建適當的時鐘信號隔離屏障的一面。如果光耦合器比較慢使用上升和下降時間,可能需要施密特觸發器數字輸入,以防止錯誤的數據被呈現DAC。

電子發燒友App

電子發燒友App

評論