工業和醫療設計推動產品的精度和速度日益提高。模擬集成電路行業總體能夠跟上速度的發展要求,但在精度要求上卻有所不足。許多系統都競相邁入1 ppm精度之列,特別是如今,1 ppm的線性ADC日益普遍。本文將介紹運算放大器的精度局限性,以及如何選擇為數不多的有可能達到1 ppm精度的運算放大器。另外,我們還將介紹一些針對現有運算放大器局限性的應用改善。

精度(Accuracy)與數值相關:系統特性與絕對真實數值之間的差距。精密(Precision)是以數字形式表示的數值深度。在本文中,我們將使用精度一詞,它包括噪聲、偏移、增益誤差和非線性度等系統測量的所有限制。許多運算放大器的某些誤差在ppm量級,但沒有個運算放大器的所有誤差都達到了ppm量級。例如,斬波放大器可提供ppm級的失調電壓、直流線性度和低頻噪聲,但它們的輸入偏置電流和頻率線性度存在問題。雙極性放大器具有低寬帶噪聲和良好的線性度,但其輸入電流仍可能導致內部電路誤差(對于內部電路,我們將使用“應用”一詞)。MOS放大器具有出色的偏置電流,但通常在低頻噪聲和線性度領域存在缺陷。

在本文中,我們將在轉換函數中使用大致相當于1 ppm的非線性度表現諧波失真的–120 dBc失真。

非ppm放大器類型

讓我們來看看非高線性度的放大器類型。線性度最低的類型即所謂的視頻或線路驅動器放大器。這些都是直流精度不太好的寬帶放大器:偏移達幾毫伏,偏置電流在1 μA至50 μA范圍內,并且1/f噪聲性能通常較差。理想的直流精度在0.3%至0.1%之間,但交流失真可以介于–55 dBc至–90 dBc(線性度:2000 ppm至30 ppm)之間。

下一項分類是傳統經典運放設計,例如OP-07,可能具有高增益、CMRR、PSRR以及良好的失調電壓和噪聲性能,但其失真卻無法優于–100 dBc,特別是在達到1 kΩ或更高負載的情況之下。

然后,還有一些或新或舊的廉價放大器,其失真在負載超過10 kΩ的情況下都無法優于–100 dBc。

此外,還有音頻放大器類運算放大器。它們相當實惠,且失真表現可能非常好。但是,它們的設計不合適且不能提供良好的失調電壓和1/f噪聲性能。此外,他們的失真或許在大于10 kHz后也不能變的更好了。

有些運算放大器旨在支持MHz信號的線性度。它們通常為雙極性,并具備較大的輸入偏置電流和1/f噪聲。在該應用領域,運算放大器更多追求的是–80 dBc至–100 dBc程度的性能,實現ppm性能不太現實。

無論寬帶及壓擺率多大,電流反饋放大器也不能支持深線性度,甚至是適度的精度。它們的輸入級有很多誤差源,并且增益、輸入和電源抑制性能都不高。電流反饋放大器還具有熱漂移效應,會大幅拓展正常的建立時間。

然后,我們擁有現代的通用型放大器。它們一般具備1 mV的偏移和微伏級1/f噪聲。支持–100 dBc失真,但在高負載時通常無法實現。

運算放大器的誤差源

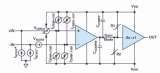

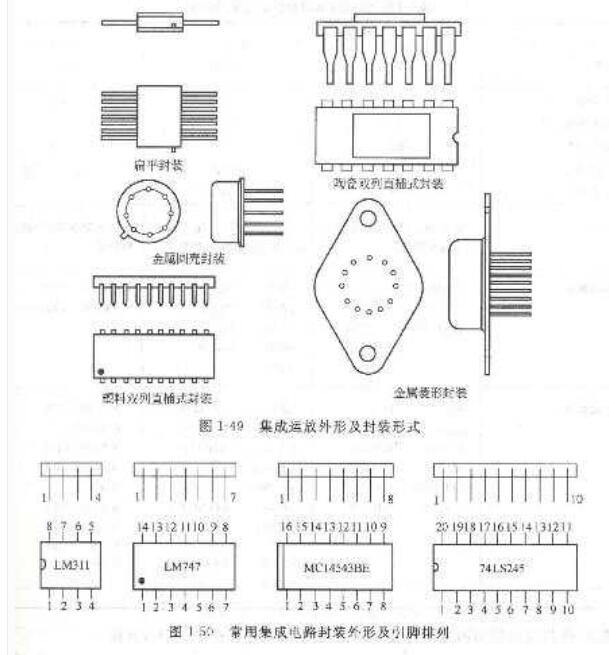

圖1顯示的是簡化的運算放大器框圖,并添加了交流和直流誤差源。拓撲為帶有輸入跨導(gm)的單極點放大器,驅動輸出緩沖單元的增益節點。盡管有許多運算放大器拓撲,但所示的誤差源對它們全部適用。

圖1.簡化的運算放大器和誤差源

輸入噪聲

有的輸入噪聲電壓VNOISE包含寬帶和1/f頻譜成分。如果噪聲的幅度類似或超過系統LSB,則無法準確地測量信號。例如,如果寬帶噪聲為6 nV/√Hz,系統帶寬為100 kHz,那么輸入端的有效值噪聲則會達到1.9 μV。我們可以使用濾波器來降低噪聲:例如,將帶寬降至1 kHz可使噪聲降至0.19 μV rms或1 μV p-p(峰峰)左右。頻域的低通濾波可降低噪聲幅度,就像ADC輸出隨時間推移而平均化一樣。

不過,由于速度太慢,1/f噪聲實際上無法過濾或均化。1/f噪聲通常使用0.1 Hz至10 Hz頻譜范圍內生成的峰峰值電壓噪聲體現。大多數運算放大器的低頻噪聲都介于1 μV p-p至6 μV p-p之間,因而不太適合對直流精度要求高的ppm級別,特別是在提供增益的情況下。

圖2顯示的是優良的高精度放大器(LT1468)的電流和電壓噪聲。

圖2.LT1468輸入電壓和電流噪聲

在圖1的輸入端,還有偏置電流噪聲源INOISE+和INOISE–。它們包含寬帶和1/f頻譜成分。INOISE乘以等效電阻會產生更多輸入電壓噪聲。一般而言,同相端和反相端的兩個電流噪聲之間互不相關,不會隨著兩端輸入電阻值相等而抵消,而是以rms方式增加。INOISE乘以輸入等效電阻產生的噪聲電壓常常會超過1/f區的VNOISE。

輸入共模抑制和偏置誤差

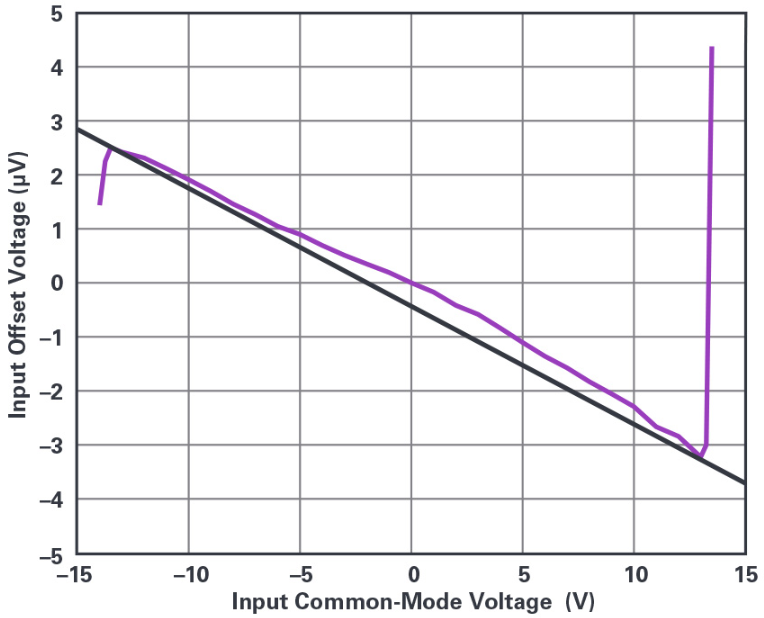

下一種誤差源是VCMRR。這體現在共模抑制比指標參數上,其中失調電壓會隨著相對于兩個供電軌的輸入電平而變化(所謂的共模電壓,VCM)。使用的符號指示箭頭方向的電源相互影響,通過它的分割線表示其可變,但可能是非線性變化。CMRR對信號的主要影響在于使線性部分與增益誤差無法區分。非線性部分將會失真。圖3顯示了LT6018的CMRR。增加的線與CMRR曲線在該曲線分化到過載之前的極點相交。該線的斜率提供的CMRR = 133 dB。范圍每相差30 V,CMRR曲線與理想線之間的偏差僅約為0.5 μV,表示ppm以下級別的輸入非常成功。其他放大器的曲率可能更大。

圖3.LT6018輸入失調電壓與VCM

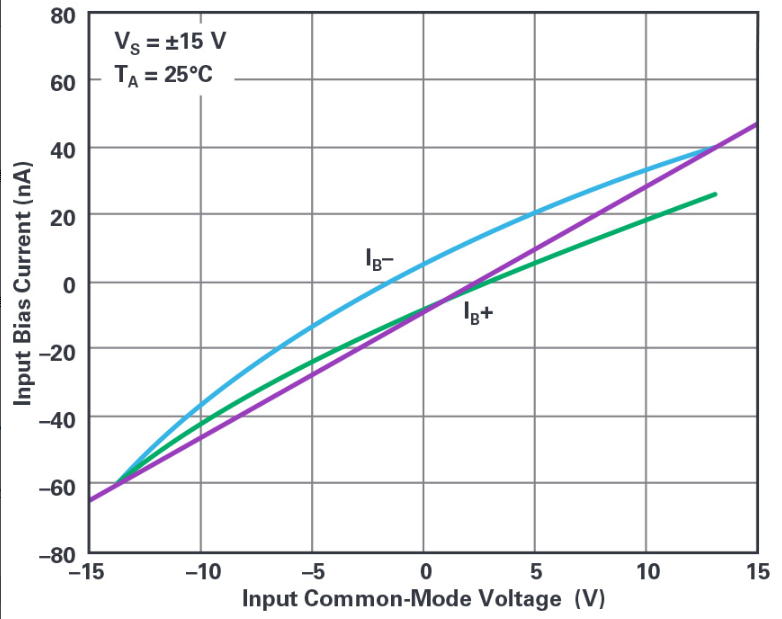

失調電壓(VOS)將歸入此處的CMRR。斬波放大器的輸入失調電壓低于10 μV,相對于2 V p-p至10 V p-p的典型輸入信號,接近于單ppm誤差。甚至,最佳ADC的失調電壓通常會多達100 μV。所以,10uV級的失調電壓不會對運算放大器自身造成太大的負擔;無論如何,系統本身會自動調零。與輸入信號的共模電平相關的是ICMRR,即輸入偏置電流及其隨電源的變化情況。斷線表明偏置電流會隨電壓變化,并且也可能不是線性變化。共有四個ICMRR,因為兩個輸入端有獨立的偏置電流和電平相關性,并且每個輸入端隨兩種電源的變化不同。ICMRR乘以應用電阻的阻值會增加電路的整體失調電壓。圖4顯示了LT1468的偏置電流與VCM(ICMR規格)。添加的線所示的斜率為~8 nA/V,在使用1 kμΩ應用電阻或低ppm誤差的情況下將為8 μV/V。它與直線的偏差約為15 nA,由此在1 kμΩ應用環境下會在26 V范圍內產生15 μV的誤差,或非線性度達0.6 ppm。

圖4.LT1468輸入偏置電流與VCM

輸入級失真

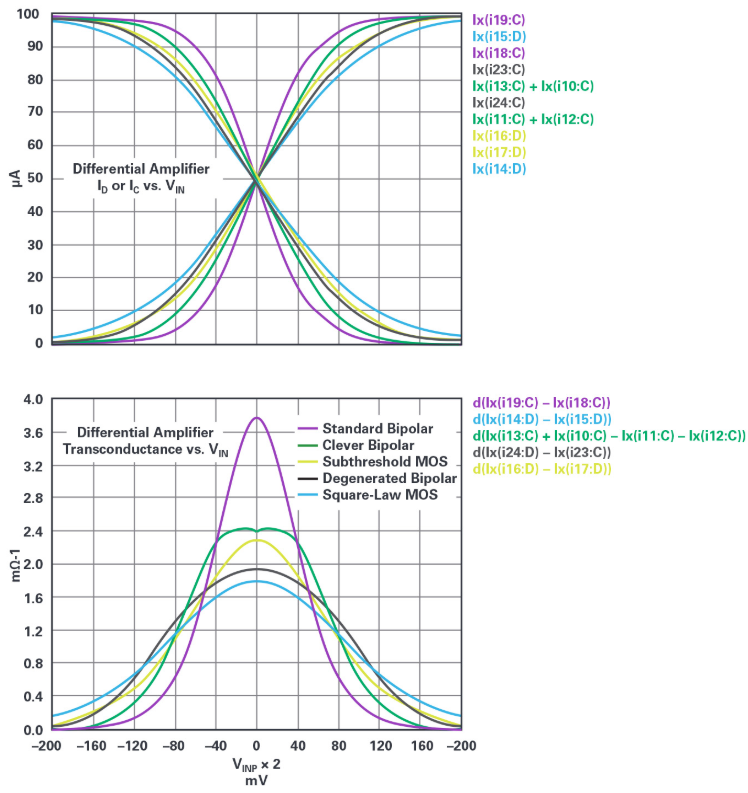

圖1顯示了輸入級,它們通常是由一對差分晶體管設計成跨導電路。圖5頂部顯示了各種差分放大器類型的集電極或漏電流以及差分輸入電壓。我們模擬一個簡單的雙極性對、一個跨線性電路(我們稱之為“智能雙極”)、一個低閾值(即非常大)的MOS差分對、一個帶發射極電阻的雙極性對(圖5中已退化)和一個超越閾下區域而進入平方律機制運行的小型MOS對。使用100 μA的尾電流模擬所有差分放大器。

在顯示圖5底部所示的跨導與VIN之前,明確的信息不多。跨導(gm)是輸出電流相對于輸入電壓的導數,使用LTspice?模擬器生成。語法當中包含d(),其在數學上等同于d()/d(VINP)。gmis的非平面度即運算放大器在頻率下的基本失真機制。

對于直流,運算放大器的開環電壓增益約為gm(R1||R2),但前提是輸出緩沖區增益大約1。R1和R2表示信號路徑中各種晶體管的輸出阻抗,每個電阻均連接到一個供電軌或其他單元。這就是運算放大器中增益受限的基礎。R1和R2不能保證為線性;它們可能導致空載失真或非線性度。除線性度之外,我們需要增益達到或超過一百萬,才能實現ppm級的增益精度。

觀察標準雙極性晶體管曲線,我們可以看到它在該組中的跨導最高,但該跨導會隨著輸入從零伏開始變化而快速消退。這一點讓人擔憂,因為線性度的基本要求就是增益或gm恒定。另一方面,誰會在乎放大器的電壓增益如此之高,以致于差分輸入隨輸出電壓的伏特級增加只能實現微伏級增加?下面是CCOMP。

圖5.各種差分放大器的輸出電流和跨導以及輸入電壓

CCOMP(CCOMPP和CCOMPM的平行線)會吸收gm在頻率范圍內的大多數輸出電流。它可設定放大器的增益帶寬乘積(GBW)。GBW可設定:在頻率f下,放大器的開環增益為GBW/f。如果該放大器在f = GBW/10時的輸出為1 V p-p,閉環增益為10,那么輸入之間將有100 mV p-p。也就是,平衡±50 mV。請注意,圖5中顯示的標準雙極性曲線在±50 mV時損耗了約一半的增益,從而保證了大規模失真。不過,智能雙極僅損耗了13%的增益,閾下MOS損耗了26%,退化雙極損耗了12%,平方律MOS損耗了15%。

圖6顯示了輸入級的失真與振幅。在應用電路輸出時將顯示這些信息(乘以噪聲增益)。輸出失真可以繼續增加,但不能減少。

圖6.輸入級的總諧波失真與差分輸入電壓

除智能雙極的輸入級之外,輸入級的差分放大器顯示失真與輸入的平方成正比。在增益一致的應用中,輸出失真與輸入失真的影響相同。這是大多數運算放大器的主要失真來源。

請考慮一個采用雙極輸入的增益一致的緩沖區。若輸出VOUT峰峰值電壓,輸入差分信號將為

我們估算

和

其中,GNOISE為應用的噪聲增益。

1 ppm非線性度相當于–120 dBc諧波失真,比例為0.0001%。假定一個放大器使用雙極性輸入級,GBW為15 MHz,作為緩沖區的輸出為5 V p-p,通過方程式2可得知該線性度的最大頻率僅為548 Hz。上述的假設前提是放大器在較低頻率下的線性度最低。當然,當放大器提供增益時,噪聲增益增加,且–120 dBc的頻率會下降。

閾下MOS輸入級支持的–120 dBc頻率最高為866 Hz,平方律MOS最高支持1342 Hz,退化雙極最高支持1500 Hz。智能雙極的失真不符合預測模式,人們必須根據數據手冊進行估算。

我們可以使用更簡單的公式

其中,K可從運算放大器數據手冊的失真曲線中找到。

附加一點,許多運算放大器都是使用軌到軌輸入級。大多數放大器通過兩個獨立的輸入級都能實現此功能,即在輸入共模范圍內,不同輸入級之間可以轉換。這種轉換會導致失調電壓變化,還可能導致偏置電流、噪聲乃至帶寬變化。此外,基本上還會導致輸出時出現開關瞬變現象。如果信號總是穿過交越區,那么則不能對低失真應用使用這些放大器。不過,對于相反的應用場合可以使用它們。

我們還沒有討論壓擺增強型放大器。這些設計在差分輸入較大的情況下不會耗盡電流。遺憾的是,差分輸入較小的場合仍會導致gm出現與所討論的輸入幅度類似的變化,并且低失真仍需要有較大的頻率環路增益。

由于我們要尋找的是ppm級的失真度,所以我們不會以接近壓擺率限值的任何方式運行放大器,所以十分異常的壓擺率不是ppm級頻率線性度的重要參數,只考慮GBW即可。

前面,我們討論了單極補償設計模式的開環增益。并不是所有運算放大器都以該方式提供補償。通常,開環增益可從數據手冊的曲線中找到,而方程式中的GBW/(GNOISE × fSIGNAL)就是頻率的開環增益。

增益節點誤差

接下來,我們來看圖1中的R1和R2。這些電阻連同輸入gm提供放大器的開環直流增益:gm × (R1||R2)。原理圖中繪制的這些電阻帶有可變的非線性刪除線。這些電阻的非線性度體現了放大器的空載失真度。而且,R1會從正電源施加影響,以致于直流正電源電壓抑制比(PSRR+)約等于gm × R1。同理,R2負責PSRR–。請注意,為什么PSRR的幅度幾乎等于開環增益?CCOMPP和CCOMPM向R1和R2注入類似的電源信號;它們在頻率范圍內設置PSRR+和PSRR–。

增益適度(《《106)的放大器的線性度可能很好,但適度增益會限制增益精度。

電源端口可能會導致失真。如果輸出級驅動的負載較大,其中某個電源就會提供負載電流。在一定頻率下,遠端電源的遠程調制能力可能很小,以致于運算放大器的旁路電容成為實際的電源。通過旁路電容后,電源電流下降。下降幅度取決于ESR、ESL和電抗,并且它們會造成電源干擾。由于輸出為AB類,所以只有一半的輸出電流波形會調制電源,形成平穩的諧波失真。頻率范圍內的PSRR可降低電源干擾。例如,如果我們觀察到電源干擾為50 mV p-p,并希望PSRR抑制電源輸入干擾使其在輸出端降至低于5 μV p-p,則PSRR在信號頻率下需達到80 dB。估算PSRR(f)~Avol(f),GBW為15 MHz的放大器在低于1500 Hz的頻率下則會擁有充足的PSRR。

輸出級失真

圖1中的最后一項是輸出級,輸出級在本文中被視為緩沖區。圖7展示了一個典型的輸出級轉換函數。

圖7.不同負載的輸出緩沖區的轉換函數

對于不同的負載,我們可看到四種誤差。首先是削波:盡管假設該輸出級的標稱增益為1,但它不完全是軌到軌輸出級。這種情況下,甚至空載輸出時,每個電源軌也會削波100 mV。隨著負載增加(降低負載電阻),輸出電壓會逐步削減。顯然,削波會嚴重影響失真,而且必須降低輸出擺幅才能避免削波。

下一種誤差是增益壓縮,當轉換函數的曲率達到信號極限情況時,我們會看到這種現象。隨著負載增加,在電壓早期階段就會出現壓縮。同削波一樣,在這種機制下,通常無法實現ppm級失真。這種壓縮通常是由輸出級較小而難以滿足輸出需要的電流所致。最好的解決方案是,使放大器提供的線性、無壓縮最大輸出電流僅約為輸出短路電流的35%。

另一種顯著的失真來源在于交越區約為VIN = 0。空載時,交越扭結可能不那么明顯。但隨著負載增加,我們可看到綠色曲線的扭結增加。估算交越失真通常需要強大的電源電流。

最后一種失真比較難以理解。由于有些放大器電路輸出正電壓和電流,還有一些輸出負信號,所以無法保證它們具有相同的增益,特別是在帶負載時。圖7顯示了負載時負信號的增益減少情況。

通過環路增益可降低所有這些失真。如果輸出級的失真為3%,那么環路增益需要為30,000才能達到–120 dBc電平。當然,這種情況發生在GBW/(30,000 × GNOISE)頻率以下,對于15 MHz的放大器通常為1 kHz機制。

有些輸出級的失真與頻率有關,但也有許多輸出級與頻率無關。開環增益可抑制輸出級失真,但該增益會隨頻率而下降。如果輸出失真不隨頻率而變化,則增益損耗會產生輸出失真,并隨頻率而線性增加。同時,輸入失真會導致總體輸出失真隨頻率而增加。這種情況下,總體閉環輸出失真可能主要為輸入失真,從而掩蓋輸出級失真的影響。

另一方面,如果輸出級失真確實隨頻率而線性變化,那么環路增益下降除導致輸入失真之外,還會導致另一種輸出失真,該失真隨頻率的平方而變化,并且無法與輸入失真區分開來。

低功耗運算放大器包含的輸出級通常較少,靜態電流低。輸出失真可能主要是由這些放大器的輸出級導致,而不是輸入級。所以,至少需要2 mA電源電流才能獲得低失真運算放大器,這種說法一定程度上是正確的。

ppm級精度的規格要求

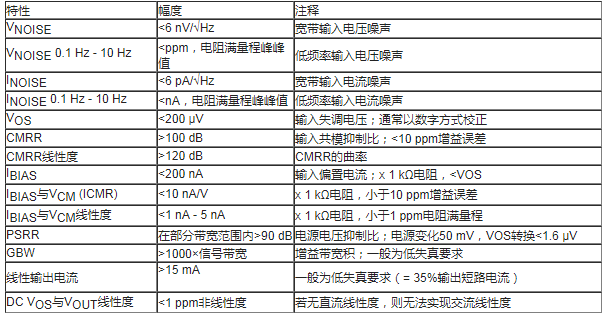

在實際電平轉換、衰減/增益和有源濾波器電路中,運算放大器需滿足一些基本要求才能支持±5 V信號、適用于1 kΩ環境并實現表1所示的1 ppm線性度。

表1.ppm精度所需的運算放大器誤差和幅度列表

現在,我們了解了運算放大器在ppm精度領域的局限性,那么我們該如何改善它們?

噪聲:顯然,首先要選擇一款輸入噪聲電壓不高于應用電阻組合噪聲的運算放大器。這樣可以降低應用電路的總阻抗,從而降低噪聲。當然,隨著應用的阻抗下降,通過它們的信號電流會增加,并可能使負載誘發的失真加大。在任何情況下,都不必使運算放大器級別的輸出噪聲遠低于其驅動級別的輸入噪聲。

電流噪聲會乘以應用阻抗,進而形成更多的電壓噪聲。在電流噪聲很低的應用中,MOS輸入非常吸引人,但它們的1/f電壓噪聲通常比雙極性輸入大。雙極性輸入的電流噪聲為pA/√Hz級別,可能會產生較大的應用噪聲,但1/f電流內容生成的應用電壓噪聲可能大于放大器的1/f電壓噪聲。一般而言,應用阻抗應小于放大器的VNOISE/INOISE,以避免IBIAS為主的應用噪聲。雙極性放大器的VNOISE越低,INOISE則越高。

幫助運算放大器實現最佳性能

減少輸入誤差

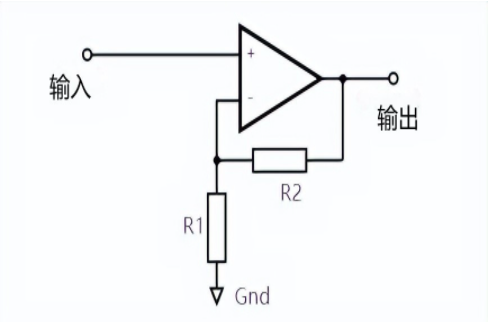

除選擇CMRR優良的運算放大器之外,設計人員還可以選擇用運放搭建反相放大電路而不是同相放大電路。在反相電路中,輸入會與地面或一些基準電壓源相連,完全不會引發CMRR誤差。不過,并不是所有應用電路都能反相,而且通常負電源無法用于負信號偏移。圖8顯示了非反相電路和反相電路中應用的雙極點Sallen-Key濾波器。

圖8.非反相(左)和反相(右)Sallen-Key有源濾波器

如果兩個輸入端均包含應用電阻,則每個輸入端的偏置電流乘以相應的電阻產生的電壓誤差會在輸出端抵消,因此也可以抵消ICMR誤差。例如,如果設置的放大器增益為10,附帶900 Ω反饋和100 Ω接地電阻,則在正輸入端安置串聯的90 Ω(900Ω||100Ω)電阻即可抵消完全相等的輸出偏置電流產生的電壓誤差。大多數雙極性運算放大器的偏置電流搭配都很恰當,使得選擇0.1%(而不是常見的1%)電阻即可實現最佳ICMR抑制。在圖4中,補償電阻與反相輸入端-input串聯放置。它們應能夠被旁路通過。因為額外的輸入電阻會導致噪聲增加(電流噪聲乘以連接的等效電阻)。

反相增益讓我們能夠使用包含軌到軌輸入的運算放大器,而不必讓信號穿過切換點(假設我們已偏置電源和共模輸入電平,以避免切換電壓)。

電源注意事項

輸出電流將會調節本地的供電電源。電源信號將通過PSRR傳輸到輸入端。被影響的輸入會生成輸出信號,圍繞其環路運行。在1 kHz頻率下,1 μF本地旁路電容的阻抗為159 Ω,遠低于電源之間線路加上電源本身的阻抗。因此,本地旁路電容實際上在低于100 kHz的頻率下沒有效果。在1 kHz頻率下,調控情況由遠程電源控制。在1 kHz頻率下,放大器可能達到90 dB電源抑制比。請注意,運算放大器電源端口的大部分電流包含了大量的信號諧波,所以我們希望從輸出到供給電源的增益低于30 dB,以實現120 dBc的目標。要實現30 dB的增益,需要電源阻抗《30×負載阻抗。因此,500 Ω負載需要電源的阻抗小于17 Ω。這種情況可行,但是這樣就不能在電源與運算放大器之間串聯電阻和電感。在10 kHz頻率下,要求則更加嚴格;PSRR將從90 dB降至70 dB,而電源阻抗則必須降至1.7 Ω。可行,但要求嚴苛。使用大型本地旁路可提供幫助。

圖9.負載和電源電流環路

圖10.復合放大器與單一放大器失真測試

從布局角度來看,了解輸出電流環路的路徑非常重要,如圖9所示。

圖9左側的圖表顯示了驅動至負載的正電源電流,然后又通過地面回歸負載。在整個接地路徑中可能存在壓降,以致于偶諧波電源電流的電壓從信號源降至輸出,從反饋分頻器降至輸出或輸入地。不過,此地非彼地。圖9右側顯示了一種傳輸電源電流的更好方式。電源電流從輸入和反饋節點傳出。

在高于100 kHz的更高頻率下,電源線路的磁輻射可能成為失真來源。電源的偶諧波電流可通過磁性方式耦合到反饋網絡的輸入,從而使失真隨頻率大幅增加。在這些頻率之下,審慎的布局至關重要。有些放大器采用的是非標準引腳;它們的電源引腳遠離輸入,有些甚至會在輸入側提供額外的輸出端口,以避免磁干擾。

減少負載為主的失真

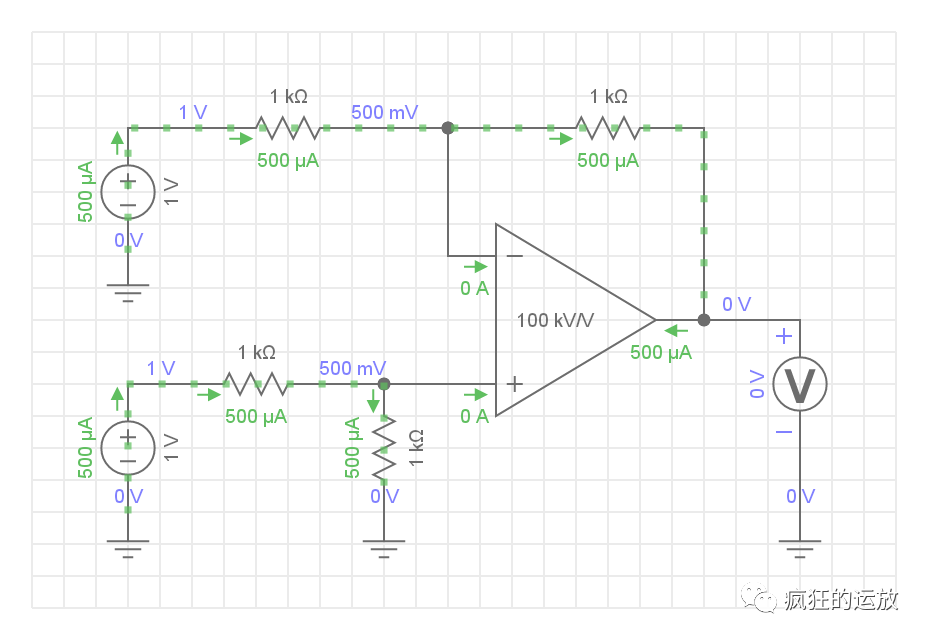

在高負載環境下,許多運算放大器的輸出級都會成為主要的失真來源。您可以通過一些技巧來改善負載失真。其一,使用復合放大器,即一個放大器驅動輸出,另一個放大器進行控制,如圖10所示。

此電路通過LTspice仿真設計實現。LTC6240和LT1395的spice模型文件中包含失真回放功能的宏模型。大多數宏模型都不會嘗試顯示失真情況,即使顯示,仿真結果也可能不準確。該工具(LTspice)可查看宏模型的文本文件,確實如此,這些宏模型的失真模擬效果非常不錯。

圖10右側是LTC6240,提供的增益為2,驅動電阻為100 Ω,對于該放大器而言負載較大。圖10左側是一款復合放大器,輸入端另設一個LTC6240,并有一款良好的寬帶電流反饋放大器(CFA)作為獨立放大器來驅動相同的負載。復合放大器的理念是,輸出運算放大器已具備適度的低失真,并且通過輸入放大器在頻率范圍內的環路增益可進一步減少該失真。對于獨立放大器和復合放大器,我們的閉環增益都為2,但在復合放大器中,可以對LT1395單獨設置其自身的增益(通過Rf1和Rg1設置為4),以降低控制放大器的輸出擺幅。由于輸入引發的失真隨輸出振幅的平方增加,由此可進一步減少控制運算放大器的失真。

圖11顯示了10 kHz、4 V p-p輸出的頻譜。

諧波失真的計算方式為:每個諧波電平(dB)減去基波電平(在10 kHz頻率下)。如圖底部所示,輸入信號的失真約為–163 dBc,非常好,足以讓人相信模擬效果。V(out2)來自于獨立的LTC6240,失真為–78 dBc。也不錯,但當然沒有達到ppm級。

圖11.復合放大器和常規放大器的失真頻譜

圖11頂部顯示了復合放大器的失真,–135 dBc,相當出色。這么好的結果,我們能否相信?為了加以驗證,中間部分顯示了原理圖上節點的失真。如果復合放大器輸出端的失真接近于零,但輸出放大器本身的失真確實有限,那么反饋過程會在其輸入端(中間)為輸出放大器失真設置負值。中間部分的失真為–92 dBc,這實際上與LT1395數據手冊的曲線匹配!我仍會想,如果宏模型中體現出物理LTC6240輸入CMRR或ICMR曲率,它們可能還會增加實際的電路失真。

遺憾的是,很少有宏模型包含失真。您必須閱讀宏模型.cir文件的標題來查看其是否受支持。要了解失真是否與數據手冊的曲線匹配,需要進行一些模擬。

復合放大器的補償可能有點棘手,但在我們的示例中,第二個放大器的帶寬比輸入放大器高出10倍以上,只需少許Cf即可提供電路補償。在此補償架構中,如果控制放大器的總體增益中包括BW的帶寬,那么輸出放大器的帶寬應》3 × BW,而總體帶寬應保守設置為約等于BW/3。

為避免帶寬損耗,我們可以使用增強放大器的方法。這樣相比復合方案對失真的改善較小,但帶寬及建立時間都會毫發無損。圖12顯示了測試原理圖。

圖12右側顯示了U2,即我們的獨立LTC6240;左側顯示了兩個LTC6240放大器。U1同獨立放大器類似,控制輸出,增益為2;U2的增益為3。U2在增強節點的輸出電壓大于U1的相應電壓,所以U2會向輸出端驅動輸送電流。RBOOST和U2的增益可以配置,以使U2向Rl驅動輸送96%的負載電流,并使U1保持輕載,從而改善失真。我們需要確保U2包含足夠的裕量,以承載額外的擺幅。

LTC6240在kΩ范圍內的負載失真主要為輸入失真,但對于100 Ω負載則主要為輸出級失真。

圖13顯示了頻譜結果。

同樣,獨立放大器在10 kHz頻率下的失真為–78 dBc。增強型放大器提供的失真為–106 dBc;不像復合放大器那么好,但比獨立放大器幾乎高出30 dBc。不過,增強型放大器的帶寬只會降低少許。

圖12.增強型放大器與獨立放大器的模擬設置

請注意,RBOOST微調了一下;如果將其改為52 ± 2 Ω,增強型失真則下降10 dBc,但隨后發生的變化則較小,最高為±10 Ω。似乎U1有一些預期極性的適度負載。理想(無負載)或額外的增強電流會導致失真增加。

最好是,U2與U1有相同的群組延遲,以使增強信號與輸出同時出現。U2的增益比U1高50%,因而閉環帶寬較少,這意味著增強輸出會使頻率范圍內的主要輸出延遲。通過跨接在U1輸入端的電阻,可將U1的帶寬降至與U2相同的水平。這樣可使U1的噪聲增益等于U2,從而實現相同的群組延遲。該模擬器在10 kHz頻率下沒有改善;U1提供最佳失真,無延遲均衡。您需要嘗試一下,才能了解在更高的頻率下是否也是這種情況。如果放大器為電流反饋類型,那么可以通過降低Rf1和Rg1使U2的帶寬升至U1的水平。

ppm級質量放大器推薦

表2顯示了一些建議的接近ppm線性度的放大器的重要規格。

紅色條目旨在提示讀者:該參數可能不符合ppm級失真。該組當中最易于使用的更好的產品為AD8597、ADA4807、ADA4898、LT1468、LT1678和LT6018。

有些放大器需要解決其輸入問題(同相放大應用可能存在問題),但仍能提供良好的失真:AD797、ADA4075、ADA4610、ADA4805、ADA4899和LTC6228。

圖13.增強型放大器和常規放大器的失真頻譜

結論

遺憾的是,商用型ppm精度放大器難以找到(如果可以找到)。市場上存在ppm線性放大器,但必須注意這些放大器的輸入電流,它們可能會通過電路中的應用阻抗產生失真。這些阻抗可以降低,但在反饋中驅動它們會導致運算放大器輸入端產生失真的風險。在特別低的輸入電流和變動環境下使用運算放大器,可以通過調整電路中的應用阻抗以使運算放大器獲得最佳失真,但這樣會增加系統噪聲。要達到ppm級線性度和噪聲,需要認真挑選運算放大器并優化應用電路。

作者簡介

Barry Harvey曾擔任模擬IC設計人員,負責設計高速運算放大器、基準電壓源、混合信號電路、視頻電路、DSL線路驅動器、DAC、采樣保持放大器、倍增器等。他擁有斯坦福大學的電氣工程碩士學位。他擁有20多項專利,發表過許多文章和論文。Barry喜歡維修用過的測試設備、彈吉他以及研究Arduino相關項目。作者:Barry Harvey ADI公司

電子發燒友App

電子發燒友App

評論