1、CS5361的主要特性

CS5361是CRYSTAL公司推出的114dB、192kHz數據輸出率的24位Δ-Σ結構音頻AD轉換器,其主要特性如下:

●采用多位Δ-Σ結構;

●具有24位轉換精度;

●114 dB動態范圍;

●總諧波失真+噪聲優于-105 dB;

●系統采樣率高達192kHz;

●功耗小于150mW?

●內部帶有高通濾波電路或直流失調電壓標定電路;

●內帶線性相移數字抗混濾波器;

●支持5V到2.5V邏輯電平;

●采用差動輸入結構;

●具有溢出檢測功能;

●采用24腳SOIC或TSSOP封裝形式。

CS5361是供數字音頻系統使用的完整的模數轉換器,可完成采樣、模數轉換、抗混濾波等功能,并最終產生以串行模式輸出的、對應于左右兩個輸入通道信號的24位采樣數據,而且其最高數據輸出率可高達192kHz。

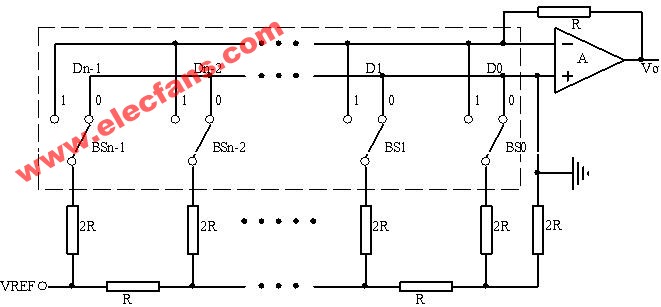

CS5361芯片采用具有優良噪聲抑制能力的差動輸入結構,并采用5階多位Δ-Σ調制器,同時帶有數字濾波器和抽樣器,從而避免了需要外部抗混濾波器的麻煩。

2、CS5361的引腳排列及功能

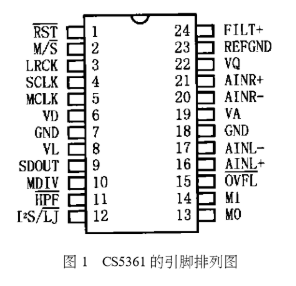

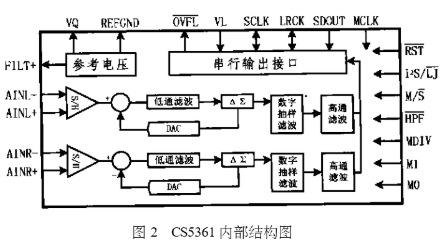

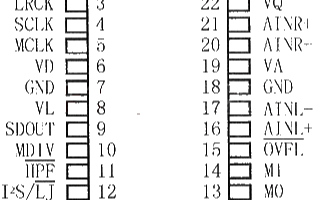

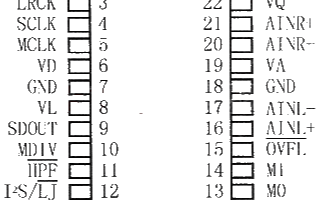

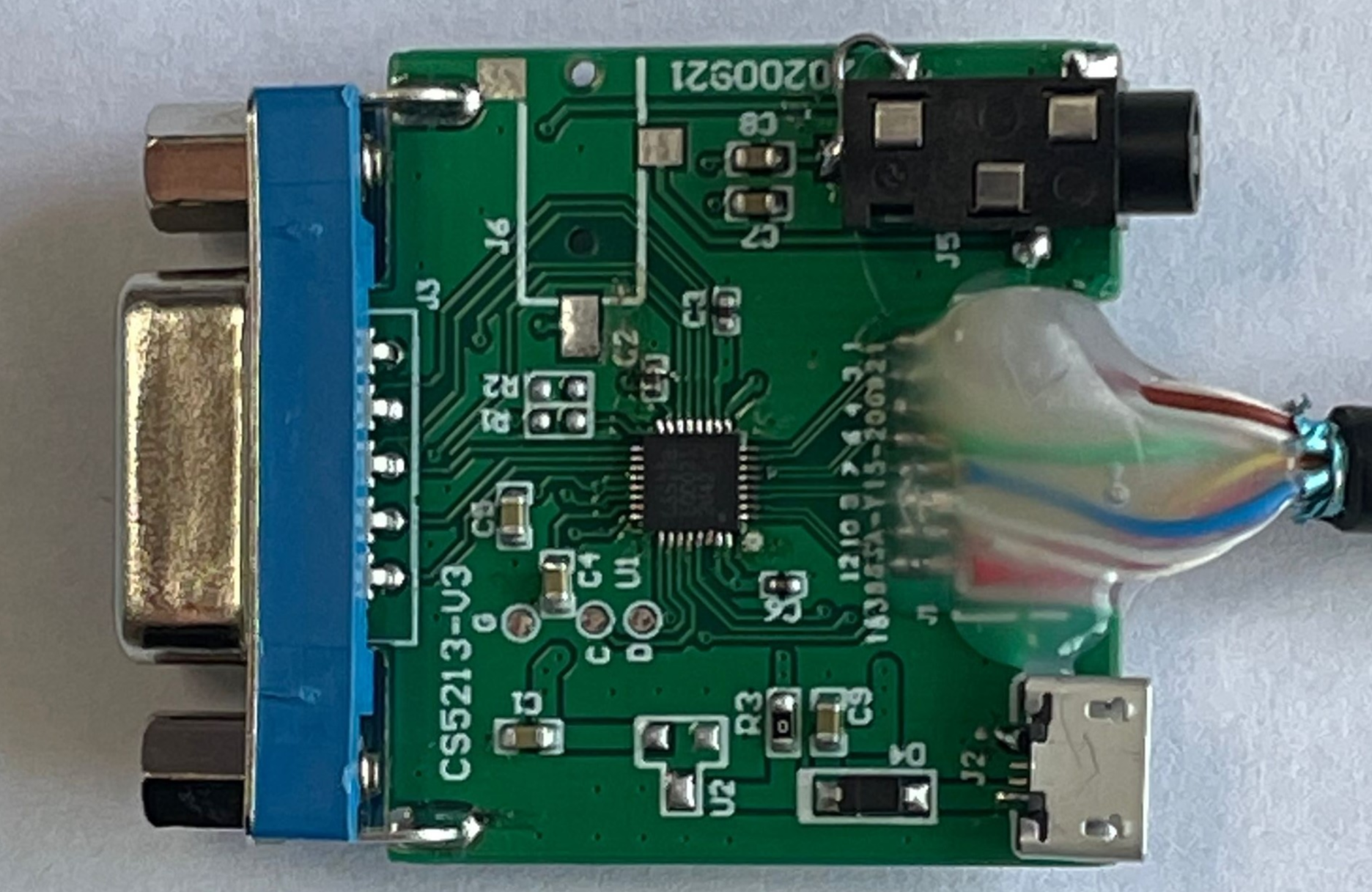

CS5361采用24腳SOIC或TSSOP封裝,引腳排列圖如圖1所示。芯片內部結構圖如圖2所示。各引腳的功能如下:

RST:低功耗模式選擇端,低電平有效;

M/ S:主、從模式選擇引腳,該腳為低電平時,芯片為從工作模式;

LRCK:該端可用于決定當前串行數據屬于左通道還是右通道;

MCLK:調制器和數字濾波器的時鐘源;

VD:芯片數字電源;

GND:地參考,必須與模擬地相連;

VL:數字輸入輸出部分電源;

SDOUT:串行數據信號輸出端;

MDIV:時鐘分頻端,該腳為高電平時,主時鐘被2分頻;

HPF:高通濾波器允許端,該腳為低電平時,高通濾波器工作;

I2S/LJ:數據輸出格式選擇端,該腳為高電平時,輸出格式為I2S,否則為左對齊輸出格式;

M0、M1:操作模式選擇端;

OVFL:左右通道溢出指示腳;

AINL+,AINL-,AINR+,AINR-:分別為左右通道模擬信號的+、-輸入端;

VA:+5V模擬電源輸入端;

VQ:內部靜態參考電壓,使用時應連接濾波器;

REFGND:內部采樣電路參考地;

FILT+:內部采樣電路參考電壓。

3、基本工作原理

CS5361轉換器工作時,應根據工作的具體需要確定工作模式、操作模式、輸出格式、高通濾波模式等工作參數,下面分別介紹這些參數的意義及設置方式。

3.1 操作模式及采樣率范圍選擇

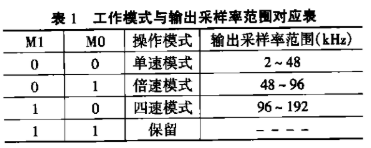

CS5361轉換器的M1、M0引腳狀態可用于決定芯片的操作模式,通過設置適當的操作模式,可使CS5361的輸出采樣率(FS)在2kHz到192kHz之間進行選擇。每種操作模式對應的采樣率范圍如表1所列。

對于每種操作模式,芯片的性能可能略有差異,例如,工作在單速模式時,CS5361的數字濾波器的通帶為0~0.47FS,阻帶大于0.58FS,阻帶衰減優于95dB,濾波器群延時為12/FS(S);工作在倍速模式時,CS5361的數字濾波器的通帶為0~0.45FS,阻帶大于0.68FS,阻帶衰減優于92dB,濾波器群延時為9/FS(S);工作在四速模式時,CS5361的數字濾波器的通帶為0~0.24FS,阻帶大于0.78FS,阻帶衰減優于97dB,濾波器群延時為5/FS(S),因此,應根據實際需要適當選擇CS5361的操作模式。

3.2 系統時鐘MCLK和MDIV狀態

當CS5361的操作模式確定后,系統時鐘和MDIV的狀態將決定具體的輸出采樣率(FS)、左右通道時鐘LRCK和串行移數時鐘頻率(SCLK)。

對于單速模式,其采樣率范圍為2~48kHz,因此,當MDIV為0時, MCLK的范圍應為512kHz~12288kHz;而當MDIV為1時, MCLK的范圍應為1024kHz~24576kHz;

對于倍速模式,采樣率范圍為48~96kHz,故在MDIV為0時, MCLK的范圍應為6144kHz~12288kHz;為1時MCLK的范圍應為12288kHz~24576kHz;

對于四速模式,由于其采樣率范圍為96~192kHz?因此,當MDIV為0時,MCLK的范圍應為6144 kHz~12288kHz;而當MDIV為1時, MCLK的范圍則應為12288kHz~24576kHz。

3.3 主從模式設置

通過設置芯片的第2腳為高電平可使CS5361進入主模式,反之進入從模式。主從模式的區別在于進入主模式時,LRCK、SCLK為輸出信號?而在從模式時,LRCK、SCLK為輸入信號,并應保證LRCK、SCLK與MCLK同步,同時應使LRCK=FS、SCLK=64FS,否則將影響器件性能的發揮。設計主從模式的目的在于,多片ADC同步工作時,可以使其中的一片工作于主模式,其它工作于從模式,從模式ADC的LRCK、SCLK來自于主模式的ADC,這樣可保證多片ADC的同步工作。

3.4 高通濾波器和直流偏移標定

由于CS5361轉換器內部集成有數字高通濾波器。因此,可通過控制該芯片HPF引腳的狀態來控制高通濾波器的工作狀況,具體的方法是:當HPF為0時,內部高通濾波器將連續記錄通道內的低頻信號,并從抽樣濾波器中濾除低于轉折頻率的低頻信號,從而實現高通濾波功能。此時高通濾波器的轉折頻率為1Hz,高通濾波器的建立時間為105/FS(s);而當HPF為1時,高通濾波器記錄的低頻信號被凍結,并連續地從抽樣濾波器中被扣除,從而實現直流偏移校正功能。與CS5361相連的模擬通道在工作時,可能會產生小的直流偏移,從而影響CS5361性能的發揮。因此,可以利用CS5361內部集成的數字高通濾波器將直流偏移校正掉,現將其工作過程說明如下:

(1) 開通高通濾波器,等待至少105/FS秒的時間以建立高通濾波功能;

(2) 高通濾波器建立后,禁止高通濾波器工作,凍結直流偏移值,此時芯片的輸出即為去掉直流偏移后的數據。

應當說明的是:在此過程中,應始終保持CS5361處在正常工作狀態。如果CS5361進入低功耗模式,那么高通濾波器中凍結的直流偏移值將被復位,此時若想實現直流偏移校正功能,則必須重復上述過程。

3.5 數據輸出格式控制

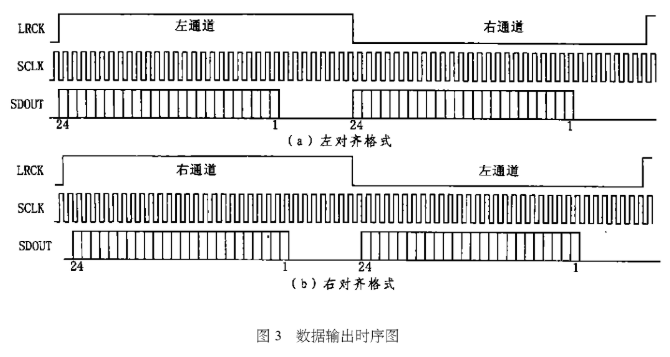

CS5361的數據輸出格式有左對齊格式和I2S格式。通過控制I2S/LJ腳的狀態可以選擇數據的輸出格式。

當I2S/LJ為0時,數據輸出格式為左對齊格式;當I2S/LJ為1時,數據輸出格式為I2S格式。兩種格式的時序圖如圖3所示。

4、應用

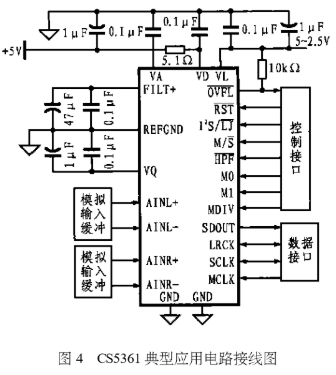

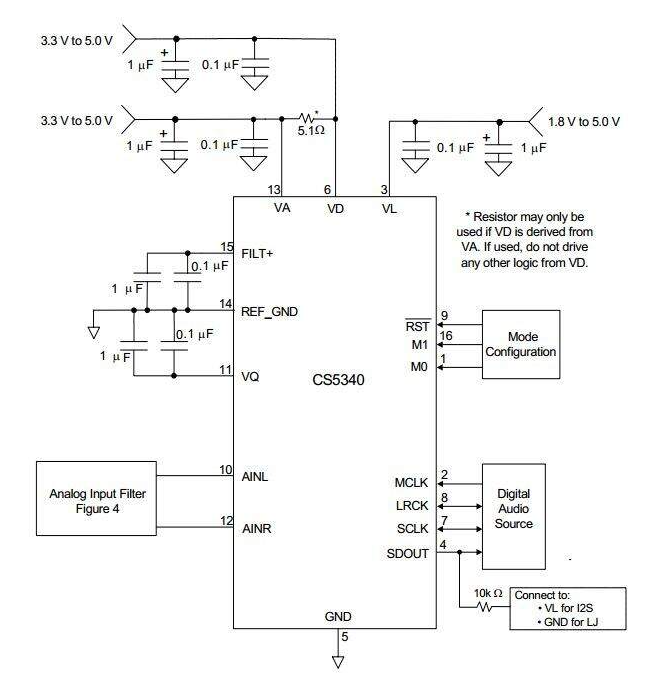

同其它高精度AD轉換器一樣,CS5361在實際應用時,也應特別注意地線和電源線的布線。設計時必須為VA和VL提供干凈的電源,當用VD給CS5361內部的數字濾波器供電時,可以通過一個電阻從VA上獲取,也可以直接與系統的邏輯電源相連。而如果VD從VA上獲取,則必須保證VD不再給其它數字電路供電。電源退耦電容必須盡可能靠近CS5361,而且應使小容量的電容更靠近ADC。所有信號,特別是時鐘信號必須遠離FILT+和VQ引腳,接在FILT+和VQ上的退耦電容必須放在與REFGND最近的位置。為了減小數字信號干擾,ADC的數字輸出應該只驅動CMOS輸入端。圖4是CS5361的典型應用電路連接圖。

由于ADC只以有限頻率采樣模擬信號,因此,高于一定頻率的信號可能會引起假頻信號。另外,由于ADC的輸入阻抗有限,因此,在輸入端還應加一定帶寬的阻抗匹配電路,以改善ADC的性能。

由于ADC參考電壓的源阻抗以及外部濾波電容的影響,系統上電后,必須經過一段時間,參考電壓才能穩定,因此,必須等待一段時間后才能得到準確的測量結果。另外在實際使用CS5361時,還有以下幾點需要注意:

(1)CS5361內部的數字濾波器為線性相移濾波器,因此應根據這一特點對不同頻率信號的相位作出校正;

(2)CS5361在開始工作時,由于要等待濾波器穩定,因此在濾波器穩定前可輸出2000個左右的無效數據,無效數據的具體個數與操作模式有關,此點應注意;

(3)CS5361從MCLK穩定到第一個數據出現,有一定的延時,延時大小與操作模式有關;

(4)CS5361轉換器的四速模式和倍速模式時的信號帶寬幾乎完全一樣,所不同的是四速模式時的輸出采樣率更高一些,濾波器的通頻帶也更寬一些,因此在滿足采樣率要求的前提下,應盡量采用低速操作模式,實際使用發現:CS5361在低速模式時的性能優于高速模式。

(5)利用CS5361的高通濾波器進行直流偏移校正時,它只是去除了做直流標定前通道所產生的直流偏移,而對于在采樣進行中產生的偏移,此功能不起作用。

(6)CS5361的數據接口時序在左對齊格式和I2S格式時有很大的差別,這一點在使用時應引起足夠的重視。

(7)CS5361通常以2的補碼格式交替連續輸出兩個通道的24位采樣數據,其信號滿偏電壓有效值為2V,這一點對格式變換十分有用。

(8)CS5361的兩個通道數據雖然是交替分時輸出,但同一組數據的采樣時刻卻是同步的,它們分別代表同一時刻的兩個通道模擬信號的值。

責任編輯:gt

電子發燒友App

電子發燒友App

評論