1、概述

ADS1202是一種高精度、80dB動態范圍的Δ-∑調節器,其工作電源為+5V。該芯片的差分輸入端可直接與傳感器或低電平信號相連,并具有合適的數字濾波器和調制速率,可以完成16-bit模數變換(A/D),而且不會遺漏代碼。在調節速率為10MHz、數字濾波器帶寬為10kHz情況下,該器件可保持12bit的有效分辨率。ADS1202適合用于中等分辨率的測量,其應用領域包括:電機電樞電流測量、通用電流測量、精密轉換測量、工業過程控制、重量測量、印刷和便攜儀器、壓力傳感器測量等。

2、主要特性及內部結構

ADS1202是單通道、2階、CMOS模擬調節器,主要特性如下:

*具有16bit分辨率;

*具有13bit線性度;

*具有分辨率/速度交替切換功能:10bit有效分辨率時具有20μs的信號延遲;12bit有效分辨率時具有77μs的信號延遲;

*使用5V單電源是的輸入范圍為±250mV;

*增益誤差為2%;

*具有四種不同方式的串行接口;

*可由分解相位或曼徹斯特譯碼實現成對的二進制譯碼,適用于一線接口連接。

ADS1202采用8腳TSSOP封裝,其外形和管腳排列圖1所示,各管腳的功能如表1所列,由于ESD可能造成器件損壞,故在使用時要采取適當的防范措施。

表1 管腳功能

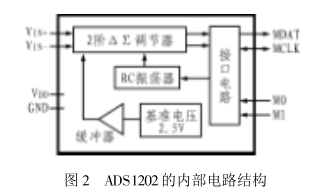

ADS1202的內部電路結構如圖2所示,從圖中可以看出:該芯片由2階Δ-∑調節器、20MHz的RC振蕩器、接口電路、2.5基準電壓源以及一個緩沖器組成。應用時,芯片的工作電壓不允許超過6V,數字輸入電壓范圍:GND-0.3V~VDD+0.3V,模擬輸入電壓范圍:GND-0.4V~VDD+0.3V,芯片的功耗為0.25W。

3、工作原理

ADS1202用一個用關電容電路來完成差分模擬輸入,這個開關電容可實現2階調節過程,它可將輸入信號數字經為一個1-bit數字流。取樣時鐘信號(MCLK)提供開關電流網絡,而調帛時鐘信號用于A/D變換過程,也作為輸出的數據幀時鐘,時鐘源可位于芯片內部也可位于芯片外部。時鐘的差頻允許隨著解決方案和信號帶寬變化。模擬輸入信號被調節器連續取樣并與內部基準電壓進行比較。數字流出現在變換器的輸出端,它精確地表示了模擬輸入電壓隨時間的變化情況。

3.1 模擬輸入

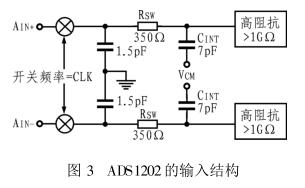

ADS1202的模擬輸入完成基于微分調節器結構。這個輸入級可實現低系統噪音、高共模抑帛比(90dB)和極佳的電源抑制比。模擬輸入端的輸入阻抗由輸入電容和調節器的時鐘頻率決定,調節器的時鐘頻率也是調節器的取樣頻率。ADS1202的基本輸入結構如圖3所示,輸入阻抗和調節器時鐘頻率之間的關系是:

AIN(Ω)=10 12/7fMCLK(MHz)

設計中應考慮輸入阻抗的影響,由于輸入級的源極阻抗很高。因此,信號經過這個外部源極阻抗時將有一部分損失。對ADS1202的模擬輸入信號有兩個限制,一是決不允許進出模擬輸入端的電流超過10mA。二是絕對輸入電壓要保持在規定的范圍內,如果輸入電壓超過了此限制,變換器前端的保護二極管將導通。此外,把加到任一輸入端上的電壓維持在規定的-320mV~+320mV范圍內時,可確保器件的線性度。

3.2 調節器

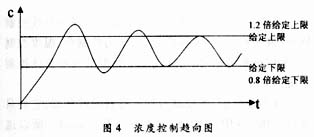

在以方式3工作時,調節器的取樣頻率(CLK)范圍在幾MHz~12MHz之間。根據時鐘應用的要求可以減小MCLK頻率,但外部的MCLK必需為調節器頻率的兩倍。調帛技術基于2階、充電平衡A/D變換器,其設計構想如圖4所示。1bit數據變換器(DAC)的模擬輸入電壓和輸出電壓被積分后,在X2和X3處提供了一個模擬電壓。這一模擬電壓出現在他們各自的積分器上,這些積分的輸出以正或負方向變化。當X4處的信號值等于比較器的基準電壓時,比較器的輸出從負變為正或從正變為負由它的初始狀態決定。當比較器的輸出值從高變為低時,1bit DAC對下一個時鐘脈沖的響應由X6處的模擬輸出電壓充電決定,促使積分相應的方向進行。調節器對積分器前端的反饋將迫使積分器輸出端的值去跟蹤輸入的平均值。

3.3 數字輸出

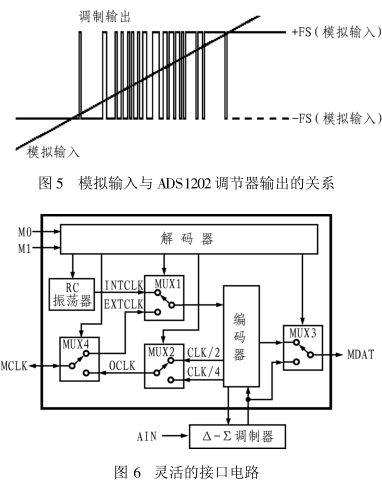

當一個外部時鐘提供給MCLK時,它被用來作為芯片的系統時鐘,也可作為數據輸出的幀時鐘。調節器輸出端的數據是一個串行流,可通過MDAT管腳在MCLK的下降沿讀取。理論上,0V的輸入差分信號將產生一連串1和0,其中50%的時間是高電平,50%的時間是低電平。而256mV的差分輸入信號將產生一連串1和0,其中80%的時間是高電平;相應的,-256mV的差分輸入信號以及產生的一串1和0中,有20%的時間是高電平,輸入電壓與輸出調制信號的關系如圖5所示。

3.4 數字接口電路

使用加到調節器的時鐘信號(CLK)對與Δ-∑調節器輸入端相連的模擬信號進行變換,以從Δ-∑調節器輸出數據。大多數應用中,將Δ-∑調節器和DSP或單片機直接相連以提供兩個標準信號。MDAT和MCLK信號提供了最簡易的連接方法,如果要減少連線的數量,兩個信號有時不是最理想的解決辦法。

在精確取樣瞬間,接收器、DSP或其它控制設備必須對來自調節器的輸出數據信號進行取樣。要做到這一點,必須對接收器的時鐘信號進行取樣,以便與發送器的時鐘信號同步。而Δ-∑調節器時鐘信號、接收器、濾波器、以及時鐘必須同步。可用三種方式來獲得這種同步:第一種方式是用Δ-∑調節器和濾波器接收來自主時鐘的時鐘信號;第二種方式是由Δ-∑調節器發送與數字信號在一起時鐘信號;第三種方式是用濾波器獲得來自接收波形本身的時鐘信號。最佳的解決方案是使用帶有靈活接口的Δ-∑調節器ADS1202,它在輸出線MCLK和MDAT上可能提供靈活的輸出形式,因此適用于不同的工作方式。可用控制信號管腳M0和M1來選擇提供的信號類型。

3.5 靈活的接口電路

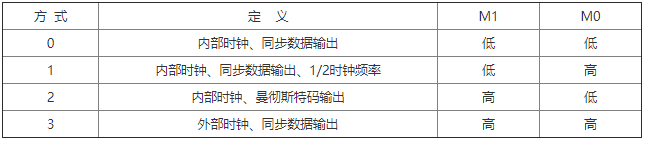

ADS1202靈活的接口電路如圖6所示。控制信號M0和M1進入解調器,解調輸入碼并選擇所需的工作方式。來自解碼器的五個解碼信號分別控制RC振蕩器、多路復用器MUX1、MUX2、MUX3以有MUX4。當使用內部RC振蕩器時,來自解碼器的控制信號可控制RC振蕩器。同時,MUX1用INTCLK信號作MUX1輸出信號的信號源,被送至編碼產生器。如果使用外部時鐘,則來自解碼器的控制信號將使內部的RC振蕩器禁用,并確定MUX1的位置。以便于EXTCLK提供MUX1的輸出信號作為編碼產生器的輸入。

MUX2可用于選擇輸出時鐘OCLK。設計時,可使用來自解碼器的控制信號控制輸出時鐘。本設計中的兩個信號均來自編碼產生器,其中一個是一半的時鐘頻率(CLK/2),另一個是四分之一的時鐘頻率(CLK/4),這兩個時鐘即可用作MUX2的輸入時鐘信號。在OCLK信號上,根據CLK/2或CLK/4入時鐘信號。在OCLK信號上,根據CLK/2和CLK/4控制信號將選擇兩種不同的輸出方式。編碼產生器接收來自MUX1的時鐘信號并把產生的Δ-∑調制時鐘分成CLK/2和CLK/4時鐘。同時,來自Δ-∑調節器的連續的數據串被編碼器精心處理,以產生成對的二進制碼,然后由編碼器輸出到MUX3。

MUX3用于選擇輸出bit連續數據MDAT的來自。來自解碼器的控制信號控制MDAT的來源。進入MUX3的兩個信號一個直接來自于Δ-∑調節器,另一個來自于編碼器。

解碼器的控制信號可以對MDAT信號選擇兩種不同的輸出方式:即Δ-∑調帛器的一位連續數據,或相同信號的成對二進制碼。來自解碼器的最后一個控制信號用于控制MUX4,MUX2則用于選擇輸入或輸出時鐘、MCLK信號。解碼器的控制信號控制著時鐘的方向,從MUX2進入MUX4的一個信號作為時鐘信號OCLK,另一個信號離開MUX4,并提供一個輸入給MUX1作為外部時鐘EXTCLK。來自解碼器的控制信號MCLK的方式,有兩種:可以選擇兩種不同的方式,一種是內部時鐘信號的輸出,另一種是外部時鐘信號的輸入。使用五個控制信號的解碼電路,可通過多路復用器設定理想的工作方式。

3.6 工作方式的設置

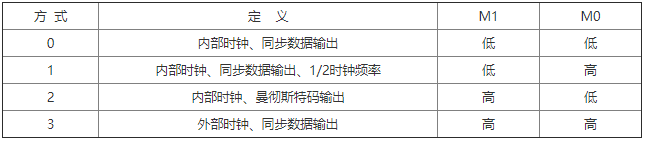

ADS1202有四種工作方式可供選擇,具體選哪一種由管腳M0和M1來決定,其選擇方式如表2所示。

表2 工作方式的選擇

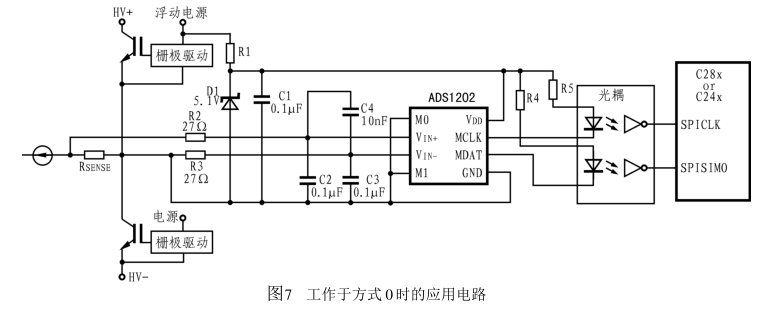

4、用設計實例

ADS1202以方式0工作時的典型應用電路如圖7所示。該電路通過分流電阻RSENSE來測量電機的電樞電流。為了得到更好的性能,信號先要被濾波。R2和C2用于濾除同相輸入端上的噪聲,R3和C3用于濾除后相輸入端上的噪聲,而C4與R2、R3相結合則可用來濾除共模輸入噪聲。在這個電路中,分流電阻經三條線與ADS1202相連。

芯片的工作電源取自于IGBT上面的驅動電源,為了對電源濾波,建議連接一個0.1μF的去耦電容,如要更好的濾波,可以另外再加一個1μ~10μF的電解電容。ADS1202的工作方式控制管腳M0和M1都要接低電平。兩個輸出信號MCLK和MDAT都要直接與光電耦合器相連,因為輸出級有能力去提供和吸入相同的電流,所以連接光電耦合器可以傳輸正向或反向信號,而不需要給光耦二極管并聯放電電阻,原因是輸入驅動器有能力保持LED二極管輸出放電。數字信號處理芯片(DSP)C28X或C24X可以直接連到光耦的兩個通道的輸出端,在這個電路中,到達C28X或C24X的信號是標準的Δ-∑調制信號,并直接與SPICLK和SPISMO引腳相連。Δ-∑變換器不需要有串行數據的字同步。

當需要減少元件時,ADS1202以方式2工作時的電路如圖8所示。圖中,管腳M1為高電平,而M0為低電平,僅同相輸入信號要被濾波,R2和C2用于濾除同相輸入端上的噪聲,反相輸入端直接與GND管腳相連。來自ADS1202的輸出信號是曼徹斯特碼,在這種情況下僅傳輸一路信號,因此可用一個光電耦合器通道來代替兩個通道。

5 、設計印刷電路板時應注意的問題

5.1 工作電源

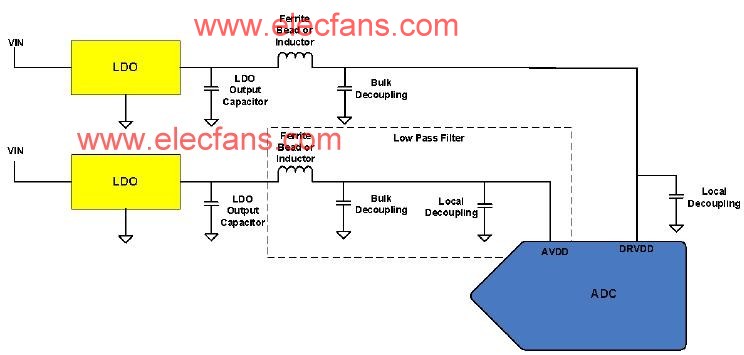

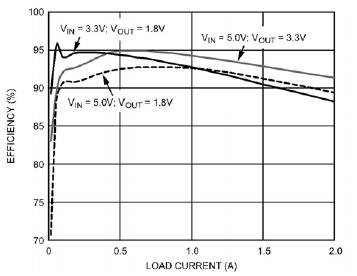

在設計印刷電路板時,通常僅需要VDD一個電源,如果在線路板上有分開的模擬和數字電源,那么將ADS1202電源同模擬電源相連較為適宜。控制噪音的另一種方法是在ADS1202電源上連接一個10Ω電阻。在ADS1202的電源管腳上連接一個電阻和去耦電容可獲得更好的濾波效果。使用的模擬電源必須穩定性好、噪聲低。對ADS1202來說,更高的分辨率及電源抑制比將是十分必要的。數字電源含有高頻噪聲,有可能耦合到ADS1202的模擬部分。這種噪音可能來自于開關電源、單片機或數字信號處理芯片。通常,外部的數字濾波器能以MCLK的整倍數抑制高頻噪音。僅僅這些頻率以下和以上的噪音將混入數字濾波器的傳輸頻帶,從而影響變換結果。例如:在接通電源后,ADS1202的輸入、VIN+、VIN-和MCLK還不出現,這種情況將引起鎖存。在接通電源之后如果這些信號出現,串連電阻將被用來限制輸入電流。要確定ADS1202和不同電源之間的適當連接,實驗是最好的方法。

5.2 接地

設計時把模擬和數字電路部分必須小心清楚的分開,每一部分都要有它們自己的地線,并且不能重迭。變換器下面不要連接地線,但應把兩者用適當的信號線相連。對于多個變換器,連接的兩上地線要盡可能靠近所有變換器的一個中心區域。在某些情況下,要找到把兩個地線連到一起的最佳點,必須通過實驗。

5.3 電路的去耦

在ADS1202的電路設計中,一定要用好去耦元件,所有的支耦電容,特別是0.1μF的陶恣電容一定要盡可能地安放在靠近去耦管腳。為對VDD至GND去耦,必須將1μF和10μF電容器與0.1μF電容并聯在一起。對VDD至GND去耦至少要用一個0.1μF的陶瓷電容,另外,加到每一個數字元件上的電源也應如此。

責任編輯:gt

電子發燒友App

電子發燒友App

評論