在數(shù)字電路中,凡是任一時刻的穩(wěn)定輸出不僅決定于該時刻的輸入,而且還和電路原來狀態(tài)有關者都叫時序邏輯電路。時序邏輯電路結(jié)構(gòu)示意圖如圖2-41所示。時序邏輯電路的狀態(tài)是靠具有存儲功能的觸發(fā)器所組成的存儲電路來記憶和表征的。

2018-01-31 09:27:23 53525

53525

D觸發(fā)器實現(xiàn)二分頻電路(D觸發(fā)器構(gòu)成的2分頻電路)

2020-03-02 11:05:49

D觸發(fā)器組成的_2N_1_2分頻電路,幾種奇數(shù)分頻電路設計

2012-05-23 19:34:41

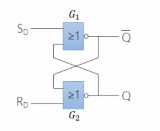

觸發(fā)器PPT電子教案:觸發(fā)器是構(gòu)成時序邏輯電路的基本邏輯部件。? 它有兩個穩(wěn)定的狀態(tài):0狀態(tài)和1狀態(tài);? 在不同的輸入情況下,它可以被置成0狀態(tài)或1狀態(tài);? 當輸入信號消失后,所置成的狀態(tài)能夠保持

2009-09-16 16:06:45

觸發(fā)器輸入電路二極管D的作用是只把負的尖脈沖輸入觸發(fā)器,還可用來組成加速電路。

2009-09-22 08:28:30

的時序邏輯電路主要有觸發(fā)器、計數(shù)器、寄存器和順序脈沖發(fā)生器等。 時序邏輯電路的輸出值由輸人值和記憶元件的狀態(tài)值共同決定。也就是說,時序邏輯電路中過去的輸人所形成并保留下來的狀態(tài)對當前的輸出具有影響。這種

2020-12-23 17:25:49

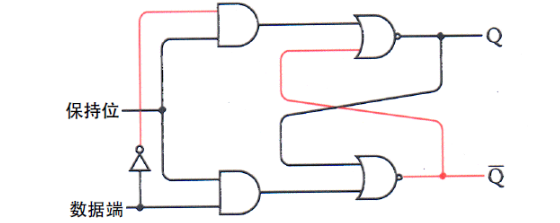

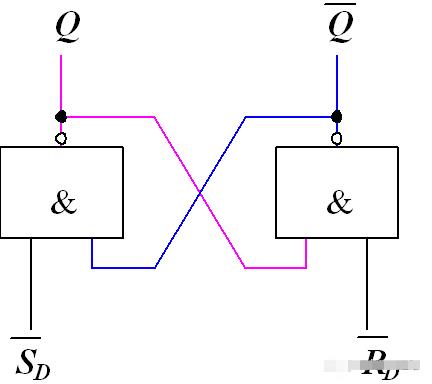

、復位端的電平觸發(fā)的SR觸發(fā)器的工作原理? 為了能適應單端輸入信號的需要,在一些集成電路產(chǎn)品中,將電平觸發(fā)的SR觸發(fā)器經(jīng)過修改,得到了電平觸發(fā)的D觸發(fā)器,也稱D型鎖存器。 圖5:電平觸發(fā)的D

2023-02-22 17:00:37

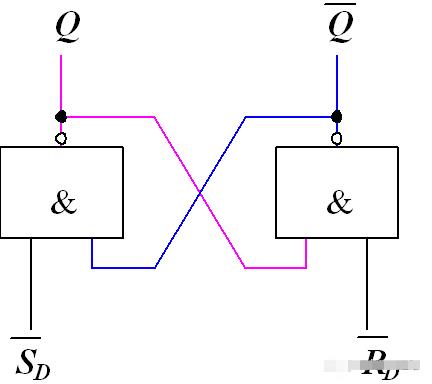

基本的SR NAND觸發(fā)器電路具有許多優(yōu)點,并在順序邏輯電路中使用,但是它存在兩個基本的開關問題。1.必須始終避免設置= 0和復位= 0條件(S = R = 0)2.如果在啟用(EN)輸入為高時設置

2021-02-01 09:15:31

時序邏輯電路應用很廣泛,根據(jù)所要求的邏輯功能不同進行劃分,它的種類也比較繁多。在具體的授課環(huán)節(jié)中,主要選取了應用較廣、具有典型時序邏輯電路特征的三種邏輯器件進行比較詳細地介紹 。1.計數(shù)器一般來說

2016-10-25 23:03:31

在實際的數(shù)字系統(tǒng)中,通常把能夠用來存儲一組二進制代碼的同步時序邏輯電路稱為寄存器.由于觸發(fā)器內(nèi)有記憶功能,因此利用觸發(fā)器可以方便地構(gòu)成寄存器。由于一個觸發(fā)器能夠存儲一位二進制碼,所以把n個觸發(fā)器

2018-10-27 22:38:21

寄存器,由寄存器又可以組成存儲器。觸發(fā)器是由基本邏輯門電路構(gòu)成的,它有兩種輸出穩(wěn)定狀態(tài),稱作為“1”狀態(tài)和“0”狀態(tài),分別代表它所寄存的代碼為“1”和“0”;它有兩個輸入端,用于接收代碼“1”和“0

2019-12-25 17:09:20

決定了接下來什么時候發(fā)生。簡單的時序邏輯電路可以由標準的雙穩(wěn)態(tài)電路構(gòu)成,例如:觸發(fā)器,鎖存器和計數(shù)器,它們本身可以通過以特定組合方式將通用與非門和/或或非門簡單地連接在一起以產(chǎn)生所需的時序電路而制成

2021-01-29 09:19:07

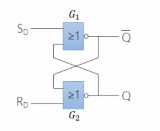

邏輯可構(gòu)成時序邏輯電路,簡稱時序電路。現(xiàn)在討論實現(xiàn)存儲功能的兩種邏輯單元電路,即鎖存器和觸發(fā)器。雙穩(wěn)態(tài):電子電路中。其雙穩(wěn)態(tài)電路的特點是:在沒有外來觸發(fā)信號的作用下,電路始終處于原來的穩(wěn)定狀態(tài)。在外

2016-05-21 06:50:08

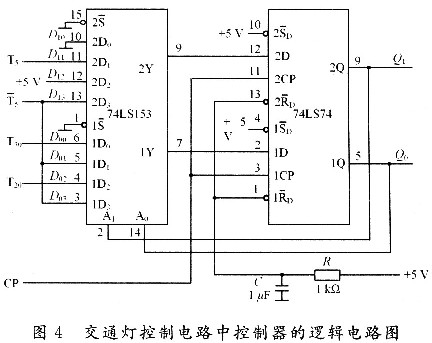

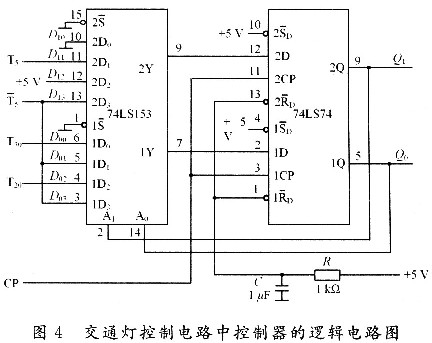

題時構(gòu)思了兩種方案:一種是用以AT89C2051為核心的單片機控制方案;另一種是用以74LS112雙JK觸發(fā)器構(gòu)成的數(shù)字邏輯電路控制方案。考慮到單片機方案原理復雜,而且調(diào)試較為繁瑣,所以本文采用后一種方案。 總體方框圖 鍵盤輸入、密碼修改、密碼檢測、開鎖、執(zhí)行電路圖 報警電路圖 報警次數(shù)檢測及鎖定電路圖

2017-01-20 17:47:36

華為 邏輯電路設計規(guī)范自己選擇下載閱讀!

2015-08-04 14:46:14

雙D型觸發(fā)器構(gòu)成的振蕩器電路實致上是一個可以靈活控制的波形信號發(fā)生器,其結(jié)構(gòu)為圖1所示的一個由雙D型觸發(fā)器構(gòu)成的振蕩器。該振蕩器的起振、停止可以控制,輸出波形的相位和占空比也可以調(diào)節(jié),其工作波形如圖2所示。圖2 波形發(fā)生器工作邏輯圖

2009-05-25 00:41:49

觸發(fā)器敏感的SR鎖存器,如圖所示,現(xiàn)在S = D而R =不是D。D型觸發(fā)器電路我們記得,一個簡單的SR觸發(fā)器需要兩個輸入,一個用于“設置”輸出,一個用于“復位”輸出。通過將反相器(NOT門)連接到SR

2021-02-03 08:00:00

1、在FPGA中使用門級結(jié)構(gòu)設計D觸發(fā)器的思路一個邏輯電路是由許多邏輯門和開關組成的,因此用基本邏輯門的模型來描述邏輯電路結(jié)構(gòu)是最直觀的。本實驗設計使用結(jié)構(gòu)描述語句實現(xiàn)D觸發(fā)器功能,采用帶異步置位

2022-07-04 16:01:57

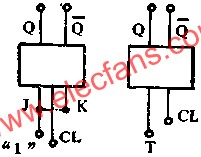

新課第五章 觸發(fā)器5.1 概述1、觸發(fā)器具有“記憶”功能,它是構(gòu)成時序邏輯電路的基本單元。本章首先介紹基本RS觸發(fā)器的組成原理、特點和邏輯功能。然后引出能夠防止“空翻”現(xiàn)象的主從觸發(fā)器和邊沿觸發(fā)器。同時,較詳細地討論RS觸發(fā)器、JK觸發(fā)器、D觸發(fā)器、T觸發(fā)器、T'觸發(fā)器的邏輯功能及其描述方法。

2009-04-02 11:58:41

本帖最后由 gk320830 于 2015-3-5 20:47 編輯

如何用JK觸發(fā)器構(gòu)成D觸發(fā)器 電路圖來人給個圖吧..

2011-11-14 15:21:03

復雜,它也可看成是數(shù)字邏輯電路中的元件。目前也已有集成化產(chǎn)品可供選用。常用的觸發(fā)器有 D 觸發(fā)器和 J—K 觸發(fā)器。 D 觸發(fā)器有一個輸入端 D 和一個時鐘信號輸入端 CP ,為了區(qū)別在 CP 端

2011-07-22 09:23:16

如何采用D型和E型金剛石型MOSFET開發(fā)邏輯電路?

2021-06-15 07:20:40

嵌入式硬件(三)數(shù)字邏輯電路一、組合邏輯電路1.非門2.與門3.與非門4.或門5.或非門6.異或門7.三態(tài)門二、時序邏輯電路1.觸發(fā)器(flip-flop)(1)RS觸發(fā)器(2)D觸發(fā)器2.鎖存器

2021-07-26 08:02:44

單片機內(nèi)部有大量寄存器, 寄存器是一種能夠存儲數(shù)據(jù)的電路, 由觸發(fā)器構(gòu)成。1.觸發(fā)器觸發(fā)器是一種具有記憶存儲功能的電路, 由門電路組成。 常見的觸發(fā)器包括: RS 觸發(fā)器、 D 觸發(fā)器和 JK觸發(fā)器

2022-01-20 07:13:51

;nbsp; 組合邏輯電路設計中應注意的問題 3.2 算術運算電路 3.2.1 半加器電路

2008-05-15 21:57:28

時序邏輯電路一、實驗目的 1.掌握D、JK觸發(fā)器的邏輯功能和使用 2.掌握中規(guī)模集成計數(shù)器74LS161

2009-09-16 15:08:37

的對象就是觸發(fā)器。 描述時序電路時通常使用狀態(tài)表和狀態(tài)圖,我們分析時序電路的方法通常是比較相鄰的兩種狀態(tài)(即現(xiàn)態(tài)和次態(tài))。 例 1:列出下表所示時序電路的邏輯表達式、狀態(tài)表和狀態(tài)圖邏輯表達式為:Qn+1

2018-08-23 10:36:20

時序邏輯電路設計6.1 基本D觸發(fā)器的設計6.2 JK觸發(fā)器6.3 帶異步復位/置位端的使能T觸發(fā)器6.4 基本計數(shù)器的設計6.5 同步清零的計數(shù)器6.6 同步清零的可逆計數(shù)器6.7 同步預置數(shù)的計數(shù)器

2009-03-20 10:04:53

觸發(fā)器(Flip-Flop,簡寫為 FF),也叫雙穩(wěn)態(tài)門,又稱雙穩(wěn)態(tài)觸發(fā)器。是一種可以在兩種狀態(tài)下運行的數(shù)字邏輯電路。觸發(fā)器一直保持它們的狀態(tài),直到它們收到輸入脈沖,又稱為觸發(fā)。當收到輸入脈沖

2019-06-20 04:20:50

用CD4013雙D觸發(fā)器做的脈沖4分頻器

2021-05-13 07:25:00

電后,與非門的1腳為低電平,故U1A輸出端第3腳為高電平,3腳與與非門的12腳相連,故12腳也為高電平。 2、電路剛上電時,D觸發(fā)器的RD引腳通過電容C1,電阻R2上電復位,使D觸發(fā)器的輸出Q=D

2023-03-20 15:33:48

的邏輯功能。時序邏輯電路對于時序邏輯電路,分析電路的最終目的是什么?實際情況往往是:已知時序電路圖,要求找出該電路的功能。時序邏輯電路一般分析方法1、驅(qū)動方程:按組合邏輯電路的分析方法,寫出觸發(fā)器輸入

2021-11-18 06:30:00

D觸發(fā)器結(jié)構(gòu)的五分頻器邏輯電路

2019-09-11 11:29:19

怎樣去設計一個基于數(shù)字電路的D觸發(fā)器?如何對基于數(shù)字電路的D觸發(fā)器進行仿真?

2021-09-16 06:45:31

多輸入時序電路的基本原理是什么?基于數(shù)據(jù)選擇器和D觸發(fā)器的多輸入時序邏輯電路設計

2021-04-29 07:04:38

組合邏輯電路的基本模塊是什么?時序邏輯電路怎樣進行工作的?

2021-09-18 09:19:42

集成觸發(fā)器、集成計數(shù)器及譯碼顯示電路實驗目的1. 驗證基本RS、D、JK觸發(fā)器的邏輯功能。2. 了解十進制加法計數(shù)器和減法計數(shù)器的工作過程。3. 了解計數(shù)、譯碼、顯示電路的工作狀態(tài)。實驗原理在數(shù)字電路

2008-12-11 23:38:01

。4. 了解半加器、全加器的邏輯功能及三變量表決電路的邏輯功能。實驗原理說明門電路是組成邏輯電路的最基本單元,與非門是組成各種組合電路的基本的環(huán)節(jié),其他各種類型的電路通常是在與非門的基礎上派生而得的。1. 常用門電路的邏輯符號和邏輯函數(shù)表達式

2008-12-11 23:36:32

基本邏輯電路: 組合邏輯電路、&

2008-09-12 16:35:29 40

40 組合邏輯電路設計一、實驗目的1. 熟悉組合邏輯電路的基本設計方法;2. 練習用門電路、譯碼器、數(shù)據(jù)選擇器設計組合邏輯電路。二、實驗設備1.

2008-09-12 16:41:23 0

0 時序邏輯電路的輸出不但和當前輸入有關,還與系統(tǒng)的原先狀態(tài)有關,即時序電路的當前輸出由輸入變量與電路原先的狀態(tài)共同決定。為達到這一目的,時序邏輯電路從某一狀態(tài)

2009-03-18 22:13:04 71

71 用Protel 99實現(xiàn)邏輯電路設計:介紹可鳊程邏輯器件(PLD)應用和相應軟件的發(fā)展;使用EDA 工具Protel 99的PLD設計簡單邏輯電路的一般方法。關鍵詞Protel 99 PLD CUPL語言

眾所周知,

2009-11-01 10:13:34 0

0 提出了從狀態(tài)轉(zhuǎn)換圖中直接求得觸發(fā)器的置位和復位函數(shù),從而確定觸發(fā)器的驅(qū)動方程這樣一種設計同步時序邏輯電路的新方法.設計原理簡單,易于理解,適合于所有同步時序

2010-02-28 19:23:02 15

15 講述組合邏輯電路設計基礎

2010-05-06 10:29:15 0

0 數(shù)字邏輯電路設計課程

數(shù)字邏輯電路的設計包括兩個方面:基本邏輯功能電路設計和邏輯電路系統(tǒng)設計。關于基本邏輯功能電路設計一般在《數(shù)字電路技術基礎

2010-05-24 16:05:50 0

0 摘要:基于邏輯電路的設計中經(jīng)常涉及到用卡諾圖化簡邏輯函數(shù)的過程,給出了利用次態(tài)卡諾圖設計邏輯電路的方法及不同觸發(fā)器的狀態(tài)方程在次態(tài)卡諾圖上的表示,并舉例加以說

2010-05-25 09:41:28 13

13 數(shù)字邏輯電路按邏輯功能和電路組成的特點可分為組合邏輯電路和時序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 本章首先介紹能夠存儲1 位二值信號的基本單元電路鎖存器和觸發(fā)器。著重介紹各種鎖存器和觸發(fā)器的電路結(jié)構(gòu)、工作原理、邏輯功能、特性及其描述方法。接著介紹時序邏輯電

2010-08-10 11:55:44 0

0 觸發(fā)器是時序邏輯電路中完成記憶功能的電路,是最基本的時序邏輯電路。

2010-08-12 16:20:24 0

0 一、基本要求1、理解R-S觸發(fā)器、J-K觸發(fā)器和D觸發(fā)器的邏輯功能;2、掌握觸發(fā)器構(gòu)成的時序電路的分析,并了解其設計方法;3、理解計數(shù)器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 組合電路和時序電路是數(shù)字電路的兩大類。門電路是組合電路的基本單元;觸發(fā)器是時序電路的基本單元。

2010-08-29 11:29:04 67

67

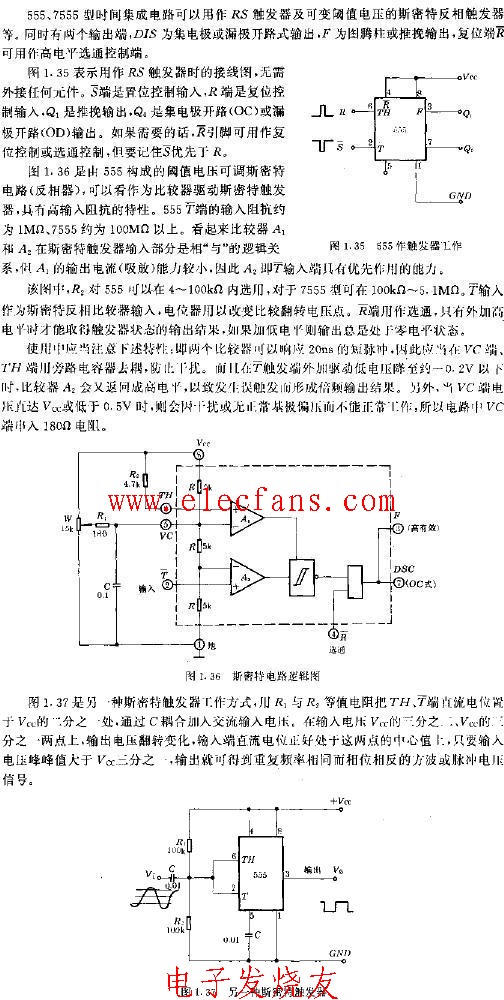

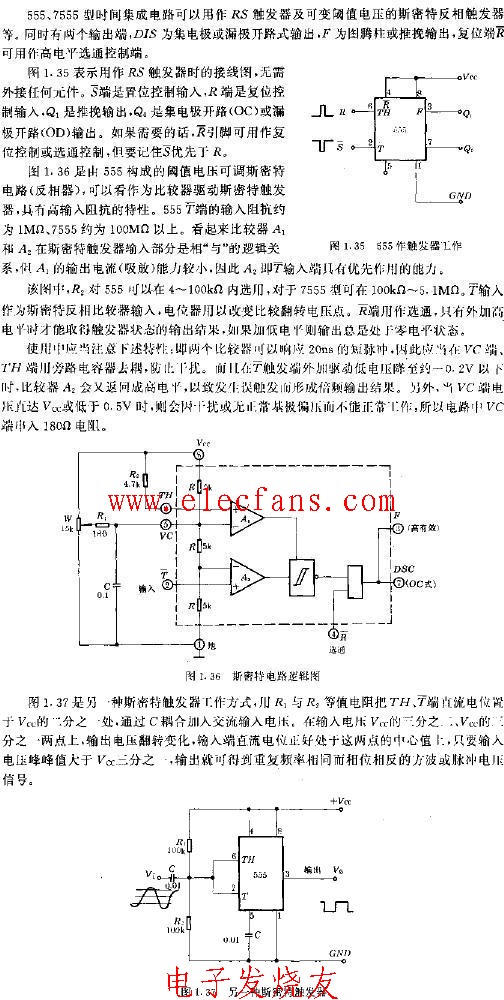

555做斯密特觸發(fā)器電路邏輯圖

是一種斯密特觸發(fā)器工作方式,用R1與R2等值電阻把TH,T端直流電位置于VCC的三分之一處,通過C耦合加入交流輸入電壓。

2008-05-19 23:04:21 2627

2627

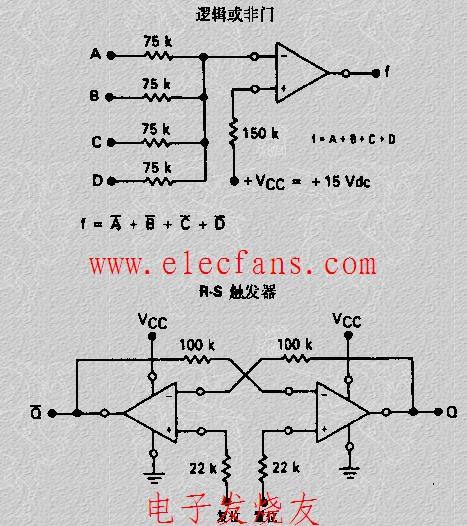

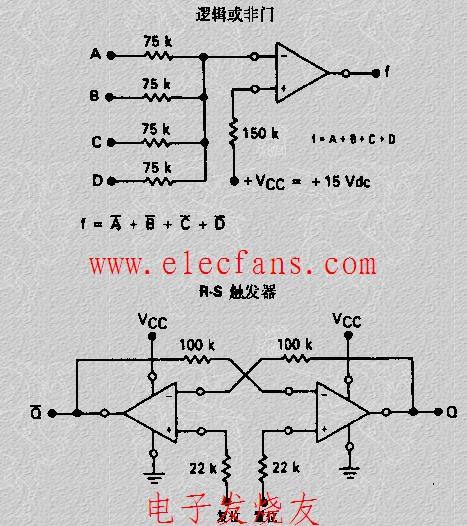

邏輯或非門-RS觸發(fā)器電路

2008-06-12 23:24:00 2313

2313

D觸發(fā)器

同步式D觸發(fā)器邏輯電路圖

D觸發(fā)器功能

2008-10-20 09:57:54 2222

2222

同步式D觸發(fā)器邏輯電路圖

2008-10-20 09:58:19 8302

8302

第二十七講 同步時序邏輯電路的設計

7.5 同步時序邏輯電路的設計用SSI觸發(fā)器16進制以內(nèi)7.5.1 同步時序邏輯電路的設計方法

2009-03-30 16:31:56 3438

3438

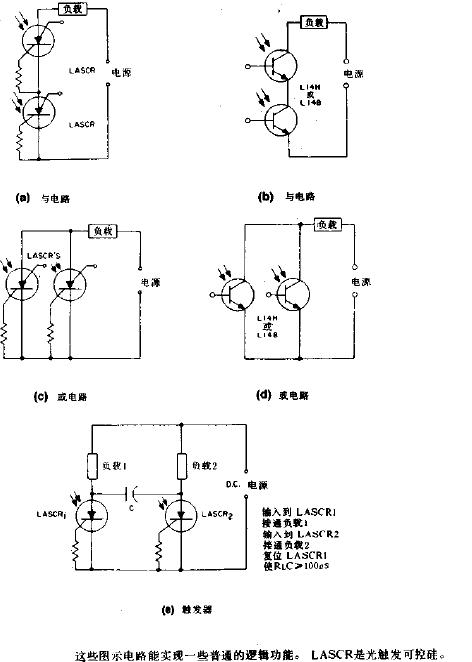

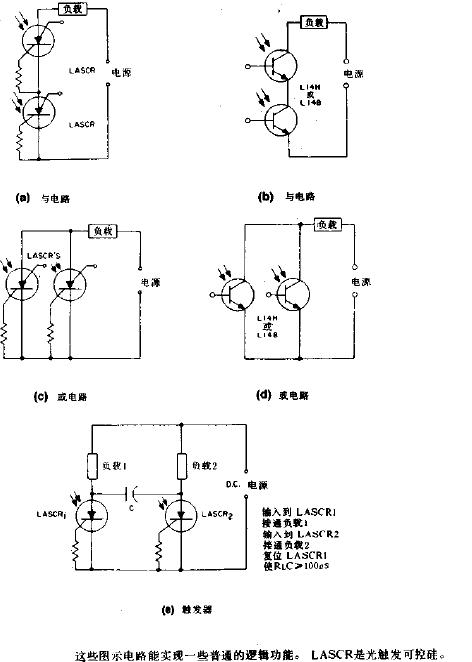

光觸發(fā)邏輯電路圖

2009-04-02 09:20:41 770

770

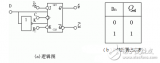

維持阻塞D觸發(fā)器

(a) 邏輯電路 &

2009-09-30 18:23:59 18683

18683

Verilog HDL語言實現(xiàn)時序邏輯電路

在Verilog HDL語言中,時序邏輯電路使用always語句塊來實現(xiàn)。例如,實現(xiàn)一個帶有異步復位信號的D觸發(fā)器

2010-02-08 11:46:43 4468

4468 時序邏輯電路實例解析

一、觸發(fā)器 1、電位觸發(fā)方式觸發(fā)器

2010-04-15 13:46:25 5041

5041 在SSI時序邏輯電路設計中,遵循的設計準則是:在保證所設計的時序邏輯電路具有正確功能的前提下,觸發(fā)器的激勵函數(shù)應最小化,從而簡化電路結(jié)構(gòu)。用卡諾圖法或公式法

2010-08-13 09:22:23 2860

2860

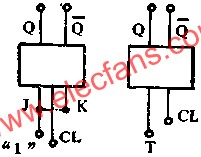

圖中所示是用J-K觸發(fā)器組成的D觸發(fā)器電路。

從J-K觸發(fā)器的邏輯圖已知在D觸發(fā)器端增

2010-09-24 00:21:27 6900

6900

圖中所示是J-K觸發(fā)器組成T觸發(fā)器的電路和邏輯符號。將J端和K端連接,作為T端,它的功能是當T=“1”,即J,K

2010-09-24 00:26:06 8546

8546

數(shù)字邏輯電路設計實踐_電工電子實驗中心實驗報告。

2015-10-29 16:25:13 0

0 定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計

2015-12-17 18:18:50 0

0 數(shù)字電子鐘邏輯電路設計,我自己編寫的,里面有橫多實用的東西

2016-06-22 16:12:01 54

54 一種帶RS觸發(fā)器的預充電鑒相電路設計及分析

2017-02-07 16:14:56 22

22 觸發(fā)器是一個具有記憶功能的,具有兩個穩(wěn)定狀態(tài)的信息存儲器件,是構(gòu)成多種時序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。在數(shù)字系統(tǒng)和計算機中有著廣泛的應用。觸發(fā)器具有兩個穩(wěn)定狀態(tài),即“0”和“1”,在一定的外界信號作用下,可以從一個穩(wěn)定狀態(tài)翻轉(zhuǎn)到另一個穩(wěn)定狀態(tài)。

2017-08-19 09:21:00 11043

11043

觸發(fā)器是一個具有記憶功能的二進制信息存儲器件,是構(gòu)成多種時序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。在數(shù)字系統(tǒng)和計算機中有著廣泛的應用。觸發(fā)器具有兩個穩(wěn)定狀態(tài),即“0”和“1”,,在一定的外界信號作用下,可以從一個穩(wěn)定狀態(tài)翻轉(zhuǎn)到另一個穩(wěn)定狀態(tài)。

2017-11-02 10:20:40 96979

96979

時序邏輯電路其任一時刻的輸出不僅取決于該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發(fā)器、計數(shù)器、寄存器等。由于時序邏輯電路具有存儲或記憶的功能,檢修起來就比較復雜。

2018-04-09 16:00:00 5673

5673

組合邏輯電路的設計與分析過程相反,本文小編主要跟大家介紹一下關于組合邏輯電路的設計步驟,順便回顧一下組合邏輯電路的分析方法。

2018-01-30 16:46:31 119435

119435

時序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時序邏輯電路有觸發(fā)器、 寄存器和計數(shù)器等。

2019-02-26 15:25:01 49628

49628 將驅(qū)動方程代入相應觸發(fā)器的特性方程中,便得到該觸發(fā)器的次態(tài)方程。時序邏輯電路的狀態(tài)方程由各觸發(fā)器次態(tài)的邏輯表達式組成。

2019-02-28 14:06:14 23502

23502 數(shù)字電路根據(jù)邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-05-16 18:32:37 7636

7636

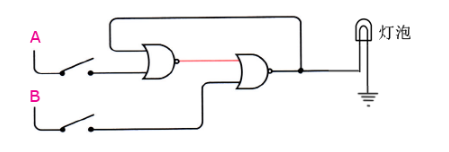

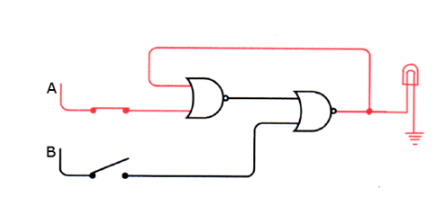

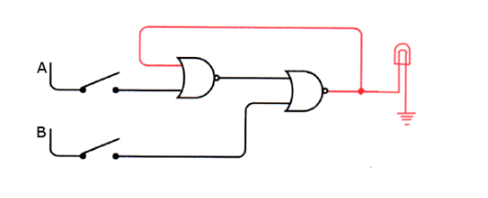

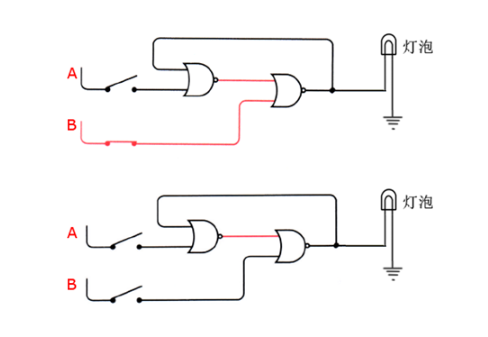

本文檔的主要內(nèi)容詳細介紹的是4人搶答邏輯電路的Multisim仿真資料免費下載。

主要運用了帶異步清零端的D觸發(fā)器和一些簡單的邏輯門電路。

2019-06-11 08:00:00 8

8 CP=1時,門。。打開,門。。被封鎖,從觸發(fā)器保持原來狀態(tài)不變,D信號進入主觸發(fā)器。但是要特別注意,這時主觸發(fā)器只跟隨而不鎖存,即。。跟隨D變化,D怎么變。。也隨之怎么變。

2019-07-15 08:57:32 45036

45036

掌握時序邏輯電路的設計方法及調(diào)試技巧,熟練掌握觸發(fā)器的功能及應用,熟練掌握常用MSI時序邏輯芯片的功能及應用

2020-05-20 08:00:00 20

20 本文檔的主要內(nèi)容詳細介紹的是組合邏輯電路和時序邏輯電路的學習課件免費下載包括了:任務一 組合邏輯電路,任務二 編碼器,任務三 譯碼器,任務四 集成觸發(fā)器,任務五 寄存器,任務六 計數(shù)器。

2020-10-27 15:58:24 31

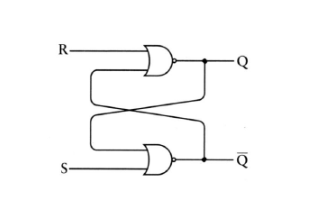

31 什么是RS觸發(fā)器 其中R、S分別是英文復位Reset和置位Set的縮寫,作為最簡單的一種觸發(fā)器,是構(gòu)成各種復雜觸發(fā)器的基礎。RS觸發(fā)器的邏輯電路圖如下圖所示。 RS觸發(fā)器可以用與非門實現(xiàn)或者用或非門

2021-03-10 16:22:37 18039

18039

基于555定時器的施密特觸發(fā)器電路設計

2021-08-05 16:03:11 19

19 這是一個系列文章,從最簡單的門電路介紹,從基礎的鎖存器、觸發(fā)器、編碼器、譯碼器等一系列數(shù)字邏輯電路開始,最終構(gòu)造一個簡易版的CPU實物

2021-11-06 09:20:58 16

16 可規(guī)劃邏輯電路設計與實習報告

2021-12-23 17:28:52 5

5 什么是RS觸發(fā)器 其中R、S分別是英文復位 Reset 和置位 Set 的縮寫,作為最簡單的一種觸發(fā)器,是構(gòu)成各種復雜觸發(fā)器的基礎。RS觸發(fā)器的邏輯電路圖如下圖所示。 RS觸發(fā)器可以用與非門實現(xiàn)或者

2022-10-19 17:49:59 7624

7624

組合邏輯電路的特點是輸入的變化直接反映了輸出的變化,其輸出的狀態(tài)僅取決于輸入的當前狀態(tài),與輸入、輸出的原始狀態(tài)無關。如果從電路結(jié)構(gòu)上來講,組合邏輯電路是沒有觸發(fā)器組件的電路。

2022-10-24 16:02:32 965

965 避免常見的邏輯電路設計問題

2022-11-04 09:50:16 0

0 觸發(fā)器也是單個寄存器,當一個寄存器設計有多個觸發(fā)器時,可以存儲一位,可以容納更多位數(shù)據(jù)。最后,移位寄存器是一種用于存儲或傳輸數(shù)據(jù)的邏輯電路。

2023-01-06 14:22:09 1067

1067 其中R、S分別是英文復位Reset和置位Set的縮寫,作為最簡單的一種觸發(fā)器,是構(gòu)成各種復雜觸發(fā)器的基礎。RS觸發(fā)器的邏輯電路圖如下圖所示。

2023-02-08 09:19:45 4113

4113 觸發(fā)器是構(gòu)成時序邏輯電路的基本單元。它是一種具有記憶功能,能儲存1位二進制信息的邏輯電路。在之前的文章中已經(jīng)介紹過觸發(fā)器了,這里再介紹一下其他類型的觸發(fā)器。

2023-03-23 15:13:26 9263

9263

本文旨在總結(jié)近期復習的數(shù)字電路D觸發(fā)器(邊沿觸發(fā))的內(nèi)容。

2023-05-22 16:54:29 9071

9071

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發(fā)器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發(fā)器功能,尤其是各種觸發(fā)器的特征方程與觸發(fā)模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 1983

1983

D觸發(fā)器,是時序邏輯電路中必備的一個基本單元,學好 D 觸發(fā)器,是學好時序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構(gòu)成數(shù)字電路組合、時序邏輯的基礎。

2023-10-09 17:26:57 1230

1230

時序邏輯電路 一 : 觸發(fā)器 1:D 觸發(fā)器 : 時序邏輯電路最小單元 。 (1):D 觸發(fā)器工作原理 忽略清零端情況下 : 當使能條件 ( 往往為時鐘的觸發(fā)沿 : 上升沿 / 下降沿 ) 滿足

2023-11-02 12:00:01 308

308

邏輯表達式是描述邏輯關系的符號表示,可以用于定義和描述各種電路和邏輯操作。在邏輯電路中,RS觸發(fā)器是一種基本的存儲器元件,也被稱為鎖存器。 RS觸發(fā)器是由兩個與門組成的,其輸出互相連接,形成一個反饋

2024-01-12 14:09:48 345

345 RS觸發(fā)器與SR觸發(fā)器都是基本的數(shù)字邏輯電路元件,常用于存儲、控制和時序電路中。

2024-01-29 14:15:08 459

459 當邏輯電路由多個邏輯門組成且不含存儲電路,對于給定的輸入變量組合將產(chǎn)生確定的輸出,則這種邏輯電路稱為組合邏輯電路。

2024-02-04 11:46:36 320

320

產(chǎn)生相應的輸出信號。本文將詳細介紹時序邏輯電路的分類、基本原理、設計方法以及與組合邏輯電路的區(qū)別。 一、時序邏輯電路的分類 時序邏輯電路主要分為三類:鎖存器、觸發(fā)器和計數(shù)器。 鎖存器(Latch): 鎖存器是一種用于存

2024-02-06 11:18:34 499

499 D觸發(fā)器是一種常見的數(shù)字邏輯電路,它在數(shù)字系統(tǒng)和計算機中扮演著重要的角色。本文將詳細探討D觸發(fā)器的邏輯功能、工作原理以及RD(Reset-D)觸發(fā)器和SD(Set-D)觸發(fā)器的作用。 首先,我們先來

2024-02-06 13:52:14 541

541

電子發(fā)燒友App

電子發(fā)燒友App

評論