1.引言

MAX547是MAXIM公司生產(chǎn)的8通道、13位輸入、電壓輸出的D/A轉(zhuǎn)換器。其轉(zhuǎn)換是通過倒置的“R-2R”梯形網(wǎng)絡(luò)實現(xiàn)的。片內(nèi)精確輸出放大器可提供電壓輸出。在不需要外部元器件的前提下,MAX547的電壓擺幅達(dá)-4.5V~+4.5V為雙極性電壓輸出。MAX547內(nèi)含帶有13位并行數(shù)據(jù)總線的雙緩沖接口邏輯電路。所有邏輯輸入均與微機和TTL/CMOS電平兼容。另外,它的輸出建立時間短,輸出電壓與輸入數(shù)字量的線性好。MAX547可用于工業(yè)過程的自動控制、設(shè)備的自動檢測、數(shù)字補償/增益調(diào)整的隨機函數(shù)發(fā)生器等。

2.MAX547的特點及引腳功能

MAX547具有如下特點:

·不需調(diào)整,滿13位有效;

·片內(nèi)有8通道的D/A轉(zhuǎn)換器;

·具有緩沖輸出;

·出廠時線性已校準(zhǔn);

·輸出與輸入一一對應(yīng);

·單極性或雙極性輸出的電壓擺幅達(dá)±4.5V;

·輸出建立時間短(5μs±1/2LSB);

·具有雙緩沖輸入鎖存器;

·數(shù)字輸入非同步裝載,一次裝載一對DAC鎖存器;

·具有非同步的清除輸入信號,可將DAC鎖存器內(nèi)容同時復(fù)位到模擬地電平;

·與微處理機和TTL/CMOS電平兼容。

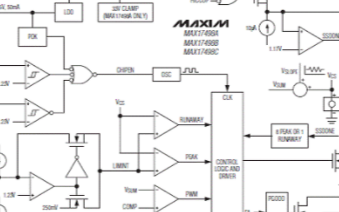

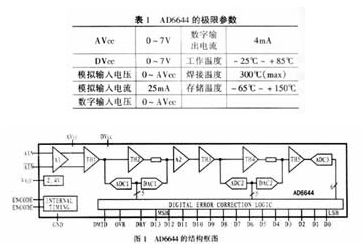

MAX547有PLCC和塑料FP兩種封裝形式,塑料扁平封裝的MAX547管腳排列如圖1所示,管腳功能

3.工作原理

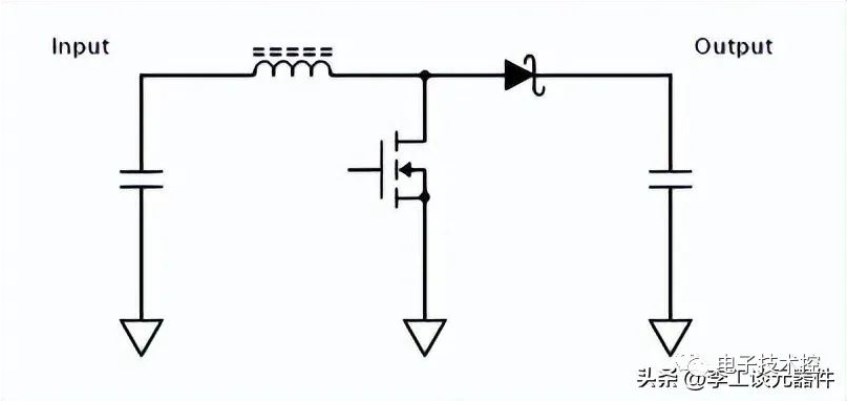

3.1D/A轉(zhuǎn)換的實現(xiàn)

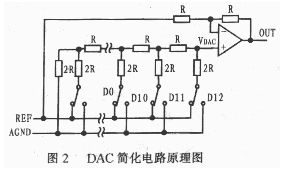

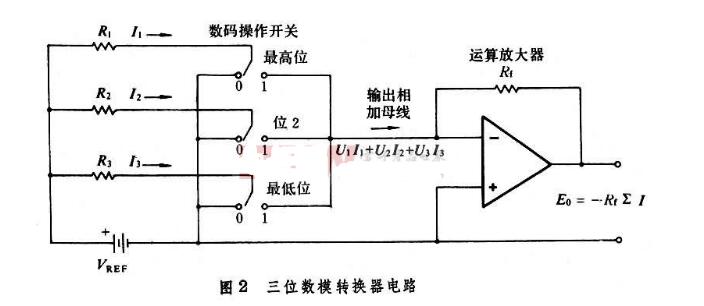

MAX547的D/A轉(zhuǎn)換是通過倒置的“R-2R”梯形網(wǎng)絡(luò)實現(xiàn)的,這些網(wǎng)絡(luò)可將13位數(shù)字輸入量轉(zhuǎn)換為相應(yīng)的模擬輸出電壓。輸出電壓的大小與輸入的基準(zhǔn)電壓大小成正比。MAX547芯片中每兩個通道DAC共用一個基準(zhǔn)電壓輸入端(REF)和一個模擬地輸入端(AGND)。每個REF輸入信號決定其所控制通道的滿量程輸出電壓。每個AGND輸入信號決定其所控制通道的偏置電壓。圖2所示是MAX547通過倒置的“R-2R”梯形網(wǎng)絡(luò)實現(xiàn)D/A轉(zhuǎn)化的簡化電路原理圖。

圖2中,DAC梯形網(wǎng)絡(luò)的輸出由增益為2的運算放大器緩沖。所有緩沖放大器的反相結(jié)點連接各自的基準(zhǔn)電壓輸入端REF。這樣雙極性電壓輸出范圍可以-REF~+REF(4095/4096)。

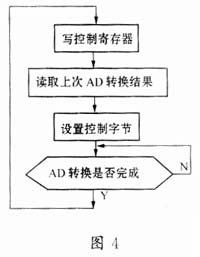

3.2MAX547工作時序

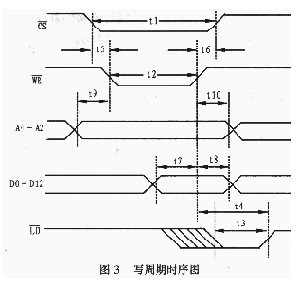

驅(qū)動MAX547的異步輸入LD信號可將數(shù)據(jù)從輸入鎖存器傳送到DAC鎖存器。DAC鎖存器的數(shù)據(jù)用來設(shè)置輸出電壓。所有輸入端的控制邏輯均通過電平觸發(fā)實現(xiàn)。數(shù)據(jù)可以鎖存也可以直接傳送給DAC鎖存器。由CS和WR信號共同控制輸入鎖存器。LD信號用于控制數(shù)據(jù)從輸入鎖存器傳送到DAC鎖存器。當(dāng)CS和WR信號同時為邏輯低電平時,輸入鎖存器打開;當(dāng)LD信號為邏輯低電平時,DAC鎖存器打開,在CS和WR為低電平期間,地址線A0,A1,A2必須有效,如圖3所示。否則,數(shù)據(jù)會被寫進(jìn)錯誤的DAC。當(dāng)CS和WR兩信號中有一個為邏輯高電平時,數(shù)據(jù)將鎖存在輸入鎖存器,在LD信號翻傳至邏輯高電平的瞬間,MAX547再把數(shù)據(jù)鎖存至DAC鎖存器。若CS和WR信號為邏輯低電平,LD信號出被置為邏輯低電平,要實現(xiàn)數(shù)據(jù)正確傳送,LD信號必須在CS和WR信號失效后持續(xù)t3或更長時間的邏輯低電平,如圖3所示。驅(qū)異步CLR信號至邏輯低電平可使所有DAC的輸出端復(fù)位到模似地電平,而與此時CS、WR、LD端輸入信號的狀態(tài)無關(guān)。在CLR信號翻轉(zhuǎn)至邏輯高電平的瞬間,數(shù)據(jù)1000H都被鎖存至所有的輸入鎖存器和DAC鎖存器中。

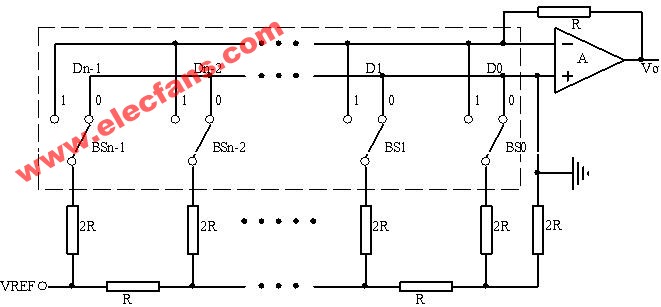

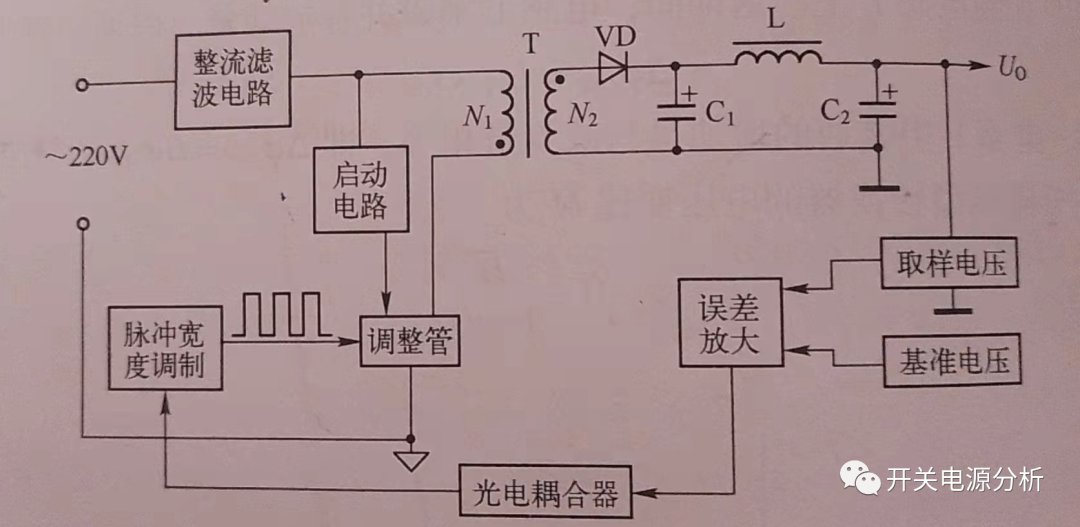

4.與MCS8051單片機的接口電路

MAX547與8051單片機的接口電路如圖4所示。由于MAX547有13位輸入位,而8051單片機只有8根數(shù)據(jù)線,所以單片機需分兩次發(fā)送要轉(zhuǎn)換的某一數(shù)據(jù),因此,電路中選用了74LS377作為數(shù)據(jù)鎖存器。它的相關(guān)指令如下:

假設(shè)選擇0通道(A2A1A0=000B),轉(zhuǎn)換數(shù)暫存R1(高5位)和R0(低8位)中,則程序如下:

MOV DPTR,#8000H

MOV A,R0

MOVX A,@DPTR ;選中鎖存器74LS377,并鎖存低8位。

CLR P1.0;DAC A的鎖存器透明。

MOV DPTR,#0000H

MOV A,R1

MOVX A,@DPTR ;選中MAX547及0通道,轉(zhuǎn)換數(shù)送入DACA的輸入鎖存器

NOP

SETB P1.0 ;轉(zhuǎn)換數(shù)送入DAC A鎖存器,同時輸出結(jié)果。

如果要獲得±2.5V的滿量程輸出電壓擺幅,可以選用MAX873作基準(zhǔn),它可以同時驅(qū)動全部4個基準(zhǔn)輸入端。若想獲得一個±4.096V的輸出電壓擺幅(1LSB=1mV),可以選用MAX676,它在+5V電源下足以驅(qū)動2個基準(zhǔn)輸入端。

用一個運算放大器可以緩沖基準(zhǔn)輸入以獲取較高精度并可以使用具有極低驅(qū)動能力的基準(zhǔn)輸入端。圖4中運算放大器的負(fù)結(jié)點直接接MAX547的基準(zhǔn)終點,并直接從基準(zhǔn)輸入端用低電流導(dǎo)線檢測電壓,以消除電路板引線阻抗的影響。而把反饋電阻加到各個基準(zhǔn)緩沖放大器是為了能通過單個基準(zhǔn)產(chǎn)生不同的基準(zhǔn)電壓。每一個基準(zhǔn)輸入端用一個0.1μF/50V的鉭電容接地,可以降低系統(tǒng)噪聲對轉(zhuǎn)換精度的影響。

AGND端接REF/2能獲得正單極性輸出。調(diào)節(jié)R2,則AGND可被偏置到電源電壓范圍內(nèi)的任何電壓,但要確保所用運算放大器有足夠的吸收電流能力以吸收模擬地端的電流。雙極性輸出時,用一個帶有未斷開模擬地的多層印制板電路作模擬地可獲得最優(yōu)的工作表現(xiàn)。在正常工作情況下,當(dāng)所有AGND管腳電勢相等時,把4個AGND管腳連接到同一點并同時作為數(shù)字系統(tǒng)的接地點,可最大限度地消除地線噪聲對轉(zhuǎn)換精度的影響。

另外一種接地設(shè)計方法是數(shù)字式偏置AG-ND。即把一個DAC的輸出連接到一個或多個AGND的輸入端。用這種方法時,不要把一個DAC的輸出與它自己的AGDN輸入端相連。

另外,在開啟電源時應(yīng)保證進(jìn)入任何基準(zhǔn)電壓輸入腳的電流不超過10mA。圖4中在VSS和GND間連接了一個肖特基管,以確保VSS電位不超過地電位300mV以上。在VSS與GND,VDD與GND之間接1μF的獨石旁路電容可濾除電源和地之間的高頻干擾。在電源穩(wěn)定之前,為避免電源干擾信號影響轉(zhuǎn)換精度,其邏輯輸入端不能有電流輸入。數(shù)字線可能驅(qū)動超過10mA的電流,因此應(yīng)在邏輯管腳設(shè)置限流電阻(如470Ω)。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論