1引 言

AD7714是適用于低頻測(cè)量應(yīng)用的完整模擬前端。器件直接從傳感器接受低電平信號(hào)并輸出串行數(shù)字。它使用和 -差(Σ-Δ)轉(zhuǎn)換技術(shù)以實(shí)現(xiàn)高達(dá)24位的無誤碼性能。輸入信號(hào)加至專有的基于模擬調(diào)制器、具有可編程增益的前端。調(diào)制器的輸出由片內(nèi)數(shù)字濾波器處理 。通過片內(nèi)控制寄存器可對(duì)此數(shù)字濾波器的第一個(gè)凹口編程,允許調(diào)整濾波器的截止頻率和穩(wěn)定時(shí)間。AD7714具有3個(gè)差分模擬輸入(它也可以配置為5個(gè)準(zhǔn)差分模擬輸入)以及差分基準(zhǔn)輸入,可以對(duì)多達(dá)5個(gè)通道的系統(tǒng)實(shí)現(xiàn)信號(hào)調(diào)理和轉(zhuǎn)換。

2引腳定義及功能

DIP封裝的AD7714如圖1。各引腳定義如下:

圖1 AD7714的封裝及其引腳

引腳1 SCLK:串行時(shí)鐘。邏輯輸入端,外部串行時(shí)鐘加 至此端以存取來自AD7714的串行數(shù)據(jù)。

引腳2 MCLKIN:器件的主時(shí)鐘信號(hào)。可以用晶振或外部 時(shí)鐘提供。器件規(guī)定的時(shí)鐘輸入頻率為1MHz和2.4576MHz。

引腳3 MCLKOUT:配合MCLKIN使用,當(dāng)器件的主時(shí)鐘是晶振時(shí),晶振跨接在MCLKIN 和MCLKOUT引腳之間。

引腳4 POL:時(shí)鐘極性,邏輯輸入端。它決定了在與微控制器之間傳送數(shù)據(jù)時(shí),串行時(shí)鐘應(yīng)閑置為高電平還是低電平。POL為低,閑置為低,POL為高,閑置為高。

引腳5 SYNC:邏輯輸入端 ,當(dāng)使用多個(gè)AD7714時(shí),它用于數(shù)字濾波器和模擬調(diào)制器的同步。一般單個(gè)使用時(shí)都接高電平。

引腳6 RESET:邏輯輸入端,低電平有效輸入,它把器件的控制邏輯、接口邏輯、數(shù)字濾波器以及模擬調(diào)制復(fù)位到上電狀態(tài)。

引腳7(8) AIN1(AIN2):可編程模擬輸入通道1(2)。與AIN6一起用時(shí)作為準(zhǔn)差分輸入端;與AIN2(AIN1)一起用時(shí)作為差分輸入對(duì)的正(負(fù))輸入端。

引腳9(10) AIN3(AIN4):可編程模擬輸入通道3(4)。與AIN6一起用時(shí)作為準(zhǔn)差分輸入端;與AIN4(AIN3)一起用時(shí)作為差分輸入對(duì)的正(負(fù))輸入端。

引腳16 AIN5:可編程模擬輸入通道5。與AIN6一起用時(shí)作為差分輸入對(duì)的正輸入端。

引腳17 AIN6:模擬輸入通道6。它是準(zhǔn)差分模式下AIN1到AIN4的基準(zhǔn)點(diǎn);與AIN5一起用時(shí)作為差分輸入對(duì)的負(fù)輸入端。

引腳11 STANDBY:把此引腳置為低電平將關(guān)斷模擬和數(shù)字電路,電流消耗減至5 mA(典型值)。

引腳13 BUFFER:邏輯輸入端。低電平時(shí)AVDD線中流過的電流減至270 mA;高電平時(shí)使輸入端有較高的源阻抗。

引腳14 REFIN(-):差分基準(zhǔn)輸入的負(fù)輸入端,只要REFIN(+)大于REFIN(-)的條件下,則REFIN(-)可位于AVDD和AGND之間的任何值。

引腳15 REFIN(+):差分基準(zhǔn)輸入的正輸入端,在REFIN(+)必須大于REFIN(-)的條件下,基準(zhǔn)輸入是差分的。REFIN(+)可位于AV DD和AGND之間的任何值。

引腳19 CS:片選邏輯輸入端,低電平有效。

引腳20 DRDY:邏輯輸出端。它是AD7714的數(shù)據(jù)寄存器有新的數(shù)字可供使用的標(biāo)志。

引腳21 DOUT:AD7714的串行數(shù)據(jù)輸出端。通過它輸出片內(nèi)寄存器信息以及模擬轉(zhuǎn)換后的數(shù)據(jù)。

引腳22 DIN:AD7714的串行數(shù)據(jù)輸入端。通過它將串行數(shù)據(jù)輸入片內(nèi)寄存器(數(shù)據(jù)寄存器除外)。

引腳12 AVDD:為模擬正電源電壓。

引腳18 AGND:模擬電路的地基準(zhǔn)點(diǎn)。

引腳23 DVDD:數(shù)字正電源電壓。

引腳24 DGND:數(shù)字電路的地基準(zhǔn)點(diǎn)。

3AD7714的片內(nèi)寄存器剖析

AD7714包含8個(gè)片內(nèi)寄存器,它們可以通過器件的串行口訪問。

3.1通信寄存器

它控制通道的選擇。在上電和復(fù)位之后,器 件等待對(duì)其通信寄存器的寫操作。寫至寄存器的數(shù)據(jù)決定對(duì)器件的下一次操作是讀還是寫,并決 定對(duì)哪一個(gè)寄存器發(fā)生讀或?qū)懖僮鳌kS后對(duì)所選擇的寄存器的讀或?qū)懀ㄒ话銛?shù)據(jù)寄存器不進(jìn)行寫 操作 )操作。一旦完成后續(xù)的對(duì)所選擇寄存器的讀和寫操作,接口便返回到等待對(duì)通信寄存器寫 操作的狀態(tài)。因此,所有與器件的通信必須從對(duì)通信寄存器的寫操作開始。另外,通過讀通信寄 存器還可以獲取DRDY的狀態(tài)。該寄存器的格式為表1。

![]()

表中0/DRDY對(duì)于寫操作,必須把0寫入該 位,否則寫將無效。對(duì)于讀操作,該位將提供器件的DRDY標(biāo)志,它與芯片的DRDY輸出引腳相同。

RS2~RS0為寄存器選擇位,對(duì)該寄存器寫 時(shí),由這3位決定對(duì)8個(gè)片內(nèi)寄存器中哪一個(gè)發(fā)生下一次的讀或?qū)懖僮鳌S2為最高位,RS0為最 低位,RS2RS1RS0從000至111分別對(duì)應(yīng)通信寄存器,模式寄存器,濾波器高寄存器,濾波器低 寄存器,測(cè)試寄存器,數(shù)據(jù)寄存器,零刻度校準(zhǔn)寄存器,滿刻度校準(zhǔn)寄存器。

CH2~CH0為通道選擇。這3個(gè)位選擇用作轉(zhuǎn) 換或用作訪問校準(zhǔn)系數(shù)的通道,如表2。

3.2模式寄存器

它是8位寄存器,可從中讀出數(shù)據(jù)或把數(shù)據(jù)寫 入其中,寄存器格式如表3。

表3中MD2~MD0為AD7714的工作模式選擇位。MD2為最高位,MD0為最低位,MD2、MD1、MD0從000至111分別對(duì)應(yīng)正常模 式、自校準(zhǔn)、零刻度系統(tǒng)校準(zhǔn)、滿刻度系統(tǒng)校準(zhǔn)、系統(tǒng)失調(diào)校準(zhǔn)、背景校準(zhǔn)、零刻度自校準(zhǔn)、 滿刻度自校準(zhǔn);

G2~G0為增益設(shè)置。G2、G1、G0從000至111分別對(duì)應(yīng)的增益為1、2、4、8、16、32、 64、128。

BO為燒斷電流。上電或復(fù)位狀態(tài)為0。此位 為1時(shí)燒斷電流連接至所選的模擬輸入對(duì),一個(gè)連接到AIN(+)輸入端,一個(gè)連接到AIN( -)輸入端。

FSYNC為濾波器同步。此位為高電平時(shí),數(shù) 字濾波器的結(jié)點(diǎn)、濾波器控制邏輯、校準(zhǔn)控制邏輯以及模擬調(diào)制器均保持在其復(fù)位狀態(tài)。此位為 低電平時(shí),調(diào)制器和濾波器開始處理數(shù)據(jù)。

3.3濾波器寄存器

由濾波器高寄存器和濾波器低寄存器兩個(gè)8位 的寄存器構(gòu)成(格式分別為表4,表5),它們都可讀寫。

表4中B/U為雙極性/單極性工作模式。此位 為0選擇雙極性工作(上電或復(fù)位的缺省狀態(tài)),此位為1選擇單極性工作。

WL為字長(zhǎng)度。此位為零則當(dāng)從數(shù)據(jù)寄存器讀 出時(shí)選擇十六位字長(zhǎng),此位為1則選擇24位字長(zhǎng)。

BST為此位為0將減少模擬前端所取電流。為 了減少AVDD吸取的電流,當(dāng)器件在fCLKIN =1MHz或2.4576MHz、增益為1至4的情況下工作時(shí),此位應(yīng)當(dāng)為0;當(dāng)器件工作于f CLKIN=2.4576MHz、增益為8至128情況下時(shí),此位必須為1,以確保器 件正常工作。

CLKDIS 為主時(shí)鐘禁止位。此位為1將禁止主時(shí)鐘出現(xiàn)在MCLKOUT引腳。這樣就可以斷開 MCLKOUT與系統(tǒng)中其他器件間的時(shí)鐘信號(hào),以節(jié)省功率。

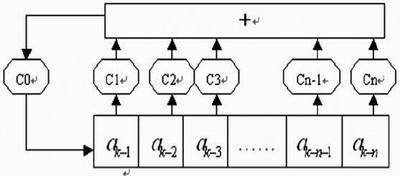

FS11~FS0為濾波器選擇。AD7714片內(nèi)提供 [sin(x)/ x ]3濾波器響應(yīng)。寫入濾波寄存器的這12位數(shù)據(jù)決定濾波器截止頻率、濾波器第一個(gè) 凹口的位置以及器件的數(shù)據(jù)輸出速率。與增益一起還決定器件的輸出噪聲和有效分辨率。濾波器 第1個(gè)凹口發(fā)生的頻率f=fCLKIN/128/ Num。其中Num是位FS0至FS11的十進(jìn)制等效值,其范圍為19~4000 [2]。

3.4測(cè)試寄存器

測(cè)試器件時(shí)使用。上電或復(fù)位時(shí)缺省為全0。 除測(cè)試外一般不用改變?cè)摷拇嫫鞯膬?nèi)容,否則器件將不能正常工作。

3.5數(shù)據(jù)寄存器

它是一個(gè)只讀寄存器,包含器件最近的轉(zhuǎn)換 結(jié)果。是否有新的的轉(zhuǎn)換結(jié)果由DRDY引腳是否變?yōu)榈碗娖經(jīng)Q定。通過寫濾波器高寄存器的WL 位,寄存器可編程為16位或24位寬度。

3.6零(滿)刻度校準(zhǔn)寄存器

AD7714包括3個(gè)零(滿)刻度校準(zhǔn)寄存器, 3個(gè)寄存器互相完全獨(dú)立,所以在全差分模式下,每一個(gè)輸入通道都有一個(gè)零(滿)刻度寄存器, 這些寄存器的每一個(gè)均為24位讀/寫寄存器,當(dāng)寫這些寄存器時(shí),必須寫入24位,否則將沒有數(shù)據(jù) 被送至寄存器。它與相應(yīng)的滿(零)刻度寄存器一起使用以組成寄存器對(duì),分別與各輸入通道相聯(lián)系。

4 AD7714的校準(zhǔn)分析

AD7714提供許多校準(zhǔn)選項(xiàng),它們可通過模式 寄存器的MD2、MD1、MD0位來編程。校準(zhǔn)周期可以在任何時(shí)刻通過寫模式寄存器的這些位來開 始。當(dāng)環(huán)境工作溫度或電源電壓有變化時(shí),應(yīng)該在器件上啟動(dòng)校準(zhǔn)程序。如果在所選的增益、濾 波器凹口或雙極性/單極性輸入范圍方面有變化,也應(yīng)當(dāng)啟動(dòng)校準(zhǔn)。

4.1自校準(zhǔn)

通過把0,0,1寫入模式寄存器的MD2、MD1、MD0位,就可以開始器件的自校準(zhǔn)。它自動(dòng)完成零刻度自校準(zhǔn)和滿刻度自校準(zhǔn)兩種校準(zhǔn)操 作。器件也可以分別進(jìn)行零刻度自校準(zhǔn)和滿刻度自校準(zhǔn)。但進(jìn)行滿刻度校準(zhǔn)前必須保證器件已包 含有效的零刻度系數(shù)。分別進(jìn)行校準(zhǔn)的意義在于:在完全的自校準(zhǔn)時(shí)序完成后,可由它本身實(shí) 現(xiàn)另外的失調(diào)或增益校準(zhǔn),從而調(diào)整器件的零點(diǎn)或增益。例如校準(zhǔn)參數(shù)中的一個(gè)(或是失調(diào)或是 增益),將不會(huì)影響另一個(gè)參數(shù)。

4.2系統(tǒng)校準(zhǔn)

該校準(zhǔn)能補(bǔ)償增益和失調(diào)誤差以及它自己的內(nèi) 部誤差,也可用于消除模擬輸入端源阻抗的任何誤差。完成系統(tǒng)校準(zhǔn)必須分為兩步。即零刻度系 統(tǒng)校準(zhǔn)和滿刻度系統(tǒng)校準(zhǔn)。將零(滿)刻度點(diǎn)加至模擬輸入端,而后通過把0,1,0(0,1, 1)寫入模式寄存器的MD2、MD1、MD0來開始零(滿)刻度系統(tǒng)校準(zhǔn)。注意,零刻度系統(tǒng) 校準(zhǔn)必須先于滿刻度系統(tǒng)校準(zhǔn)。

4.3背景校準(zhǔn)

該校準(zhǔn)模式把其校準(zhǔn)步驟與正常轉(zhuǎn)換時(shí)序相交錯(cuò),即它提供連續(xù)的零刻度自校準(zhǔn)。背景校準(zhǔn)不提供任何滿刻度校準(zhǔn),因此在進(jìn)行該校準(zhǔn)前應(yīng)當(dāng) 完成自校準(zhǔn)。器件在該校準(zhǔn)模式下消除了失調(diào)漂移。應(yīng)當(dāng)注意,器件在此模式下不應(yīng)使用SYNC 輸入端或FSYNC位。

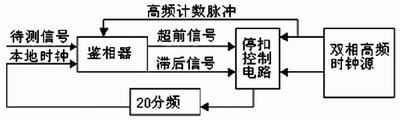

5 AD7714的工作時(shí)序及接口范例

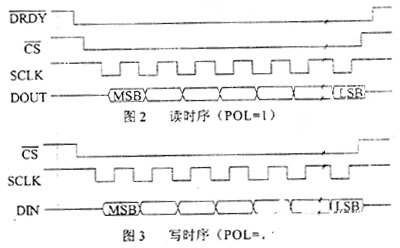

AD7714和AT89C52的接口可以通過兩種方式 實(shí)現(xiàn),一種是用AT89C52的RXD(P3.0)與AD7714的DATAIN和DATAOUT進(jìn)行數(shù)據(jù)傳送, 并利用AT89C52的TXD自帶的時(shí)鐘信號(hào)提供給AD7714的SCLK;一種是用AT89C52的某一端 口位(如P1.0)與AD7714的DATAIN和DATAOUT進(jìn)行數(shù)據(jù)傳送,對(duì)另一端口位(如 P1.1)編程產(chǎn)生時(shí)鐘信號(hào)以提供給AD7714的SCLK。圖中給出了第一種連接方式,并通過監(jiān)視 通信寄存器的DRDY位以確定數(shù)據(jù)寄存器何時(shí)有新數(shù)據(jù),當(dāng)然也可以用AT89C52的一個(gè)端口位與 AD7714的DRDY引腳相連,以輪詢的方式來確定,另外還可以以中斷方式來實(shí)現(xiàn)。AD7714的 讀/寫時(shí)序圖見圖2和圖3。

與AT89C52的典型接口電路與設(shè)計(jì)程序的流 程如圖4和圖5。

圖4 AD7714與89C52的接口電路

圖5 AD7714程序設(shè)計(jì)的主要流程圖

6 結(jié)束語

AD7714以其靈活多樣的操作方式和簡(jiǎn)單的接 口方法深受用戶的喜愛,但也必須注意以下幾點(diǎn):

(1)頻率的設(shè)置與器件轉(zhuǎn)換的有效數(shù)據(jù)密切相 關(guān),要實(shí)現(xiàn)24位無誤碼,必須保證濾波器的第一個(gè)凹口頻率小于60Hz。

(2)AD7714的輸出噪聲、分辨率、增益和第 一個(gè)凹口頻率是緊密相關(guān)的;

(3)AD7714數(shù)據(jù)輸出(寫入)的位次序與 AT89C52數(shù)據(jù)讀入(輸出)的位次序剛好相反,因此程序中必須安排位顛倒程序。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論