(文章來源:世界產(chǎn)品與技術(shù),作者:Rob Reeder , Mark Looney , Jim Hand )

就像兔子誘惑狗賽跑一樣,兔子必須要比狗跑的快,要求最嚴(yán)格的數(shù)據(jù)采集系統(tǒng)的性能自然要高于民用模數(shù)轉(zhuǎn)換器(ADC)。這些極嚴(yán)格的要求推動(dòng)IC制造商及其用戶的發(fā)展,出現(xiàn)許多滿足高端數(shù)據(jù)采集系統(tǒng)需求的“增強(qiáng)性能”的創(chuàng)新方法。

其中一種方法是通過采用多通道ADC填充轉(zhuǎn)換器的“時(shí)隙”來大幅度增加采樣速率、降低噪聲或擴(kuò)展動(dòng)態(tài)范圍。隨著給定帶寬和分辨率下的單個(gè)ADC的成本、尺寸和功耗的降低,并且隨著多個(gè)轉(zhuǎn)換器(通常封裝在一起)的應(yīng)用越來越多,該方法變得越來越切實(shí)可行。

本文將討論兩種多通道方法:信號(hào)平均--保證采樣速率不變,增加分辨率;時(shí)間交織——保證分辨率不變,提高采樣速率。采用這兩種方法的產(chǎn)品已經(jīng)誕生,例如ADI公司的AD10678(16 bit,80 MSPS ADC)和AD12500(12 bit,500 MSPS ADC)。

信號(hào)平均

信噪比(SNR,以 dB為單位),是成像和雷達(dá)等應(yīng)用中的關(guān)鍵性能指標(biāo)。這些系統(tǒng)中使用的ADC可能會(huì)受到許多外部噪聲源的影響,包括時(shí)鐘噪聲、電源噪聲和布線引入的耦合數(shù)字噪聲。只要不相關(guān)噪聲源的平方和的平方根(RSS)小于ADC固有量化噪聲,輸出平均就會(huì)有效地降低總體本底噪聲。

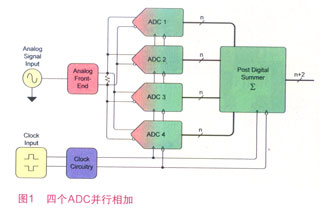

那些需要較高SNR的系統(tǒng)通常使用數(shù)字后處理器將多個(gè)ADC通道的輸出加和。信號(hào)直接相加,而來自單獨(dú)ADC(假設(shè)不相關(guān))的噪聲采用RSS加和,因此輸出加和提高了總體SNR。四個(gè)ADC輸出的加和會(huì)提高6 dB SNR,即1 LSB。AD6645 14 bit 80 MSPS ADC規(guī)定有效位數(shù)(ENOB)為12。圖1示出四個(gè)AD6645的輸出加和增加了2 bit分辨率和1 bit性能。

每個(gè)ADC的輸入包含一個(gè)信號(hào)項(xiàng)(VS)和一個(gè)噪聲項(xiàng)(VN)。對(duì)四個(gè)噪聲電壓求和得到的總電壓VT等于四個(gè)信號(hào)電壓的線性和加上四個(gè)噪聲電壓的RSS值,即:

![]()

由于VS1=VS2=VS3=VS4,等效于信號(hào)被放大了四倍,而ADC的噪聲(RMS值)只放大了兩倍,從而使信噪比增大兩倍,即增加6.02 dB。因此,四路信號(hào)求和所獲得的6.02 dB增量(?SNR)使有效分辨率提升了1bit。因?yàn)镾NR(dB)=6.02N+1.76,N為位數(shù),所以,

![]()

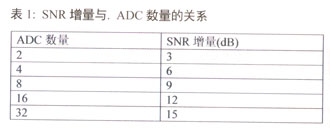

表1 中示出了多個(gè)ADC輸出加和所獲得的SNR增量。從簡(jiǎn)單性考慮,四個(gè)ADC加和是顯然的選擇。某些重要應(yīng)用也會(huì)考慮更多的ADC加和,但應(yīng)取決于其它系統(tǒng)指標(biāo)要求(包括成本)和可提供的印制電路板(PCB)尺寸。

14 bit ADC理想的SNR為(6.02 × 14) + 1.76 = 86.04 dB。然而,AD6645的技術(shù)資料中提供的SNR的典型值僅為74 dB,所以其ENOB僅為12 bit。

因此,四路轉(zhuǎn)換器輸出求和可以補(bǔ)償額外的1 bit分辨率,加上原來系統(tǒng)級(jí)ENOB可到達(dá)13 bit(80 dB) 。

當(dāng)然,這樣的系統(tǒng)需要付出一些設(shè)計(jì)努力,以及一些系統(tǒng)原型設(shè)計(jì)、鑒定和測(cè)試開發(fā)的代價(jià)。但是,AD10678集成了4個(gè)AD6645,一個(gè)時(shí)鐘分配系統(tǒng),以及一個(gè)已配置好的復(fù)雜可編程邏輯器件(CPLD)以提供高速加法運(yùn)算。現(xiàn)在可提供的AD10678以低成本和占用2.2 × 2.8英寸PCB面積的封裝,通過測(cè)試完全達(dá)到規(guī)定技術(shù)指標(biāo)。圖2所示的快速傅立葉變換(FFT)結(jié)果證明了ADC的優(yōu)良性能,在80 MSPS時(shí)鐘和10 MHz模擬輸入條件下能夠提供80.22 dB SNR。

除了提高SNR,這種體系結(jié)構(gòu)還提高了DC精度。四個(gè)ADC的失調(diào)和增益誤差是不相關(guān)的,因此采用降低噪聲一樣的方法來降低系統(tǒng)失調(diào)和增益誤差。但是在線性誤差方面上沒有改善,實(shí)際上無雜散動(dòng)態(tài)范圍(SFDR)取決于最差的ADC。

但是這種方案需要占用較大的PCB面積和4倍的功耗,但與以4倍采樣速率工作的單ADC的輸出平均方案相比,采用這種方法仍然具有優(yōu)勢(shì)。盡管以提高采樣速率增加采樣點(diǎn)數(shù)也會(huì)降低輸入信號(hào)中的常模噪聲。隨著制造工藝的改進(jìn),新的設(shè)計(jì)使ADC的內(nèi)核功耗進(jìn)一步降低;另外可提供的4通道和8通道ADC的出現(xiàn)使多ADC系統(tǒng)更容易實(shí)現(xiàn),并且減小了封裝尺寸。例如,AD9259 4 通道14 bit, 50 MSPS ADC采用 48引線LFCSP (7 mm × 7 mm) 封裝,其每通道功耗僅為100 mW。

雖然用提高輸入電壓的標(biāo)準(zhǔn)化做法來提高規(guī)定的SNR是可行的,但這會(huì)增加驅(qū)動(dòng)放大器的設(shè)計(jì)壓力,并且由于信號(hào)和噪聲一起被放大,所以會(huì)降低系統(tǒng)SNR。加和體系結(jié)構(gòu)的另一個(gè)微妙優(yōu)點(diǎn)是,滿度模擬輸入不需要大于使用單ADC時(shí)的輸入。

比較硬件和軟件成本,信號(hào)平均的方法本身要比數(shù)字濾波有優(yōu)勢(shì),但對(duì)于要提供經(jīng)濟(jì)有效的硬件處理和軟件濾波的總體系統(tǒng)考慮所要求的數(shù)字濾波,軟件常常使工作更容易。

時(shí)間交織

M個(gè)ADC的時(shí)間交織可以使采樣速率提高到M倍。通過合理地配置每個(gè)ADC時(shí)鐘信號(hào)的相位,任何一款標(biāo)準(zhǔn)ADC IC的最大采樣速率可乘以系統(tǒng)內(nèi)ADC的數(shù)量。每個(gè)ADC所需的合適的時(shí)鐘相位可以按下式計(jì)算:

![]()

M表示ADC的數(shù)量

m表示具體ADC的序號(hào),即1≤m≤M

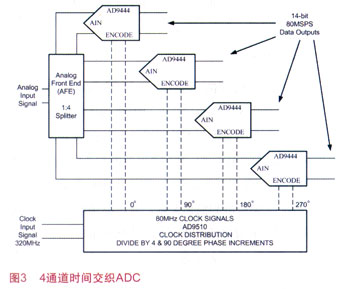

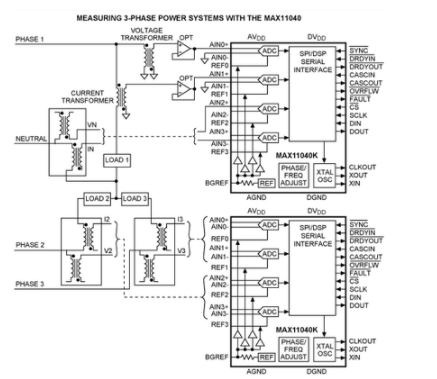

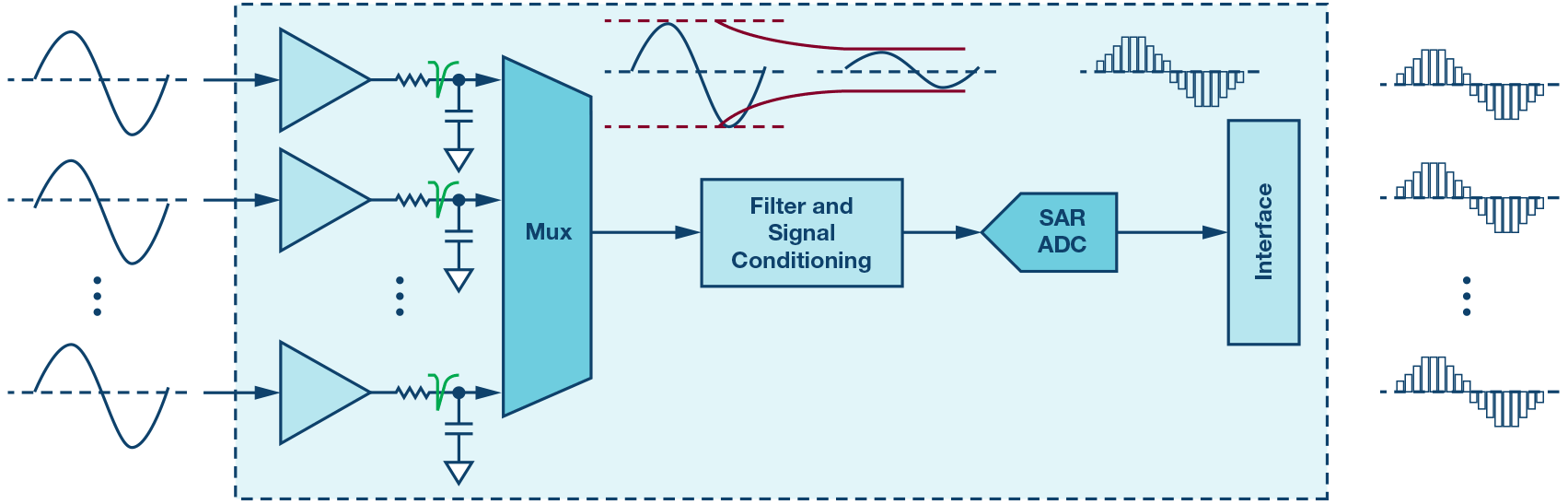

例如,一個(gè)采用AD9444 14 bit, 80 MSPS ADC組成的4通道系統(tǒng),當(dāng)每路時(shí)鐘相位以90°(π/2)間隔適當(dāng)遞增時(shí),將會(huì)產(chǎn)生14 bit,320 MSPS的效果。圖3示出這類系統(tǒng)的基本框圖。在AD12400/AD12500系列產(chǎn)品中已經(jīng)采用了12 bit集成解決方案的時(shí)間交織方法。圖4示出了AD12500框圖,其中包括ADC、時(shí)鐘管理、電源和數(shù)字后處理所有必需的功能。

增加ADC系統(tǒng)的采樣速率最明顯的好處是增加模擬采樣帶寬,又稱作奈奎斯特頻帶。增加數(shù)字化儀器系統(tǒng)中奈奎斯特頻帶可以提供很多好處:數(shù)字示波器可以擴(kuò)展模擬輸入帶寬;軟件定義無線電系統(tǒng)可以增加信道數(shù);雷達(dá)系統(tǒng)可以提高空間分辨率。圖5示出14 bit,320 MSPS ADC系統(tǒng)對(duì)22 MHz頻率信號(hào)采樣的仿真FFT圖。

該ADC系統(tǒng)的FFT頻譜擁有160 MHz奈奎斯特頻帶。為了討論方便,160 MHz奈奎斯特帶寬被分為4個(gè)獨(dú)立的40 MHz頻帶,每個(gè)頻帶代表著采樣速率為80 MSPS的單個(gè)AD9444的奈奎斯特頻帶。22 MHz基頻位于頻帶1。在圖5可以觀察到,除了基頻,還可以觀察到兩種類型的非諧波失真分量--失調(diào)雜散和鏡像雜散。對(duì)于單頻輸入信號(hào)引起的失真分量位置可以通過以下關(guān)系式來確定:

![]()

這些失真分量的出現(xiàn)是與時(shí)間交織有關(guān)的主要挑戰(zhàn)。它們直接影響通道之間的增益、相位和失調(diào)匹配誤差。實(shí)際上,這些雜散信號(hào)的幅度直接與誤差幅度成正比1,2。例如,一個(gè)通道上1%的增益誤差會(huì)造成52 dBc的鏡像雜散幅度。當(dāng)系統(tǒng)頻率規(guī)劃涉及到位于失真邊帶的頻帶時(shí),這些雜散信號(hào)均會(huì)成為問題。在這種情況下,在開發(fā)過程中必須謹(jǐn)慎地管理通道之間的匹配特性。如果系統(tǒng)性能目標(biāo)是10 bit ENOB,而且鏡像雜散信號(hào)是主要因素,那么增益匹配誤差必須優(yōu)于0.1%,相位匹配誤差必須優(yōu)于0.07°(2ps @100 MHz)!為達(dá)到這個(gè)性能等級(jí),從實(shí)現(xiàn)的角度考慮,必須減少或消除許多不同的誤差源。

每個(gè)ADC的模擬輸入和時(shí)鐘輸入的印制線尺寸必須匹配以保證傳播時(shí)延在預(yù)算等級(jí)之內(nèi)。雖然時(shí)鐘電路功能很簡(jiǎn)單,但它也會(huì)引入影響系統(tǒng)性能的誤差。與現(xiàn)有的ECL制造工藝相比,先進(jìn)的工藝,例如硅鍺RSECL(低擺幅ECL)工藝能夠在信號(hào)上升、下降時(shí)和傳播時(shí)延方面提供很大改進(jìn)。根據(jù)輸入頻率,還可采取手工線路長(zhǎng)度調(diào)整以克服孔徑延時(shí)誤差。

由于電源性能水平之間的差異,所以需要使用允許誤差小的電源,例如靠近ADC安裝的線性穩(wěn)壓器。另外,與溫度相關(guān)的性能也需要通過機(jī)械設(shè)計(jì)保證與ADC的溫度特性嚴(yán)格匹配。挑選ADC時(shí)還需要考慮以下一項(xiàng)或所有指標(biāo)的匹配:增益、失調(diào)、孔徑延遲和輸入電容。顯然,挑選四個(gè)獨(dú)立的所有關(guān)鍵性能指標(biāo)的允許誤差嚴(yán)格匹配的ADC非常困難和昂貴!必須謹(jǐn)慎權(quán)衡對(duì)系統(tǒng)設(shè)計(jì)的開發(fā)和元件成本所增加的復(fù)雜性和風(fēng)險(xiǎn)。

采用模擬調(diào)整處理方案可以在很窄的工作條件設(shè)置下與時(shí)間交織系統(tǒng)中的ADC通道之間相匹配。然而采用數(shù)字后處理方法能夠在很寬的工作條件設(shè)置下實(shí)現(xiàn)嚴(yán)格的通道匹配。高速、可配置數(shù)字平臺(tái),例如現(xiàn)場(chǎng)可編程門陣列(FPGA),為集成先進(jìn)的后處理方法——例如AFB先進(jìn)的濾波器組 ,提供了方便的工具。

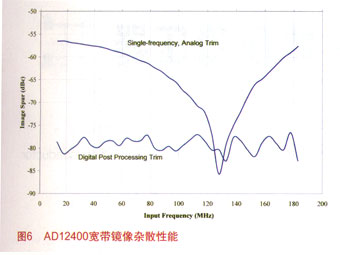

AD12400 12 bit, 400 MSPS ADC包含兩個(gè)高速ADC,并且采用時(shí)間交織方法和AFB濾波器組達(dá)到采用單個(gè)民用ADC所無法實(shí)現(xiàn)的性能(到本文寫作之日)。圖6示出寬帶動(dòng)態(tài)性能數(shù)據(jù),并且對(duì)模擬和數(shù)字調(diào)整方法做了比較。采用“手動(dòng)調(diào)整”每個(gè)通道在128 MHz處的增益和相位可達(dá)到14bit的匹配程度(86 dBc),但性能下降得非常快:12 bit(74 dBc)性能的帶寬僅為20 MHz。另一方面,采用數(shù)字調(diào)整方法,在170 MHz整個(gè)測(cè)試范圍內(nèi)能保持優(yōu)于12 bit性能--精心設(shè)計(jì)的數(shù)字后處理方法帶來的明顯性能優(yōu)勢(shì)。

因此,當(dāng)系統(tǒng)設(shè)計(jì)要求采樣速率高于市場(chǎng)上可提供的單個(gè)ADC的采樣速率時(shí),考慮采用時(shí)間交織方法是很有價(jià)值的。如果在整個(gè)奈奎斯特頻帶內(nèi)都需要保持10~12 bit性能,那么集成解決方案,例如AD12400 和AD12500,由于成功地克服了與嚴(yán)格通道匹配要求有關(guān)的困難而發(fā)揮了時(shí)間交織方法的優(yōu)勢(shì)。

信號(hào)平均 與 時(shí)間交織

這里我們已經(jīng)總結(jié)了能夠超越當(dāng)前可提供的單個(gè)ADC具備性能的兩種方法。我們已經(jīng)給出了使用這兩種方法實(shí)現(xiàn)的可提供高性能多芯片產(chǎn)品實(shí)例。事實(shí)上,這類標(biāo)準(zhǔn)的產(chǎn)品已經(jīng)面市--解決了設(shè)計(jì)問題并且提供了標(biāo)準(zhǔn)技術(shù)規(guī)范--足夠滿足許多客戶的需求。但是,下面的解釋對(duì)想進(jìn)一步研究使用標(biāo)準(zhǔn)的單個(gè)ADC或多通道非配置ADC提高性能應(yīng)用領(lǐng)域的用戶有所裨益。

比較拓?fù)浣Y(jié)構(gòu)的常用衡量指標(biāo)是SNR。假設(shè)選擇的ADC是AD9444,系統(tǒng)設(shè)計(jì)需要40 MHz帶寬和79 dB典型值SNR,那么我們可以考慮信號(hào)平均和時(shí)間交織。兩種方法都需要使用四個(gè)AD9444,以便比AD944固有的SNR提高5~6 dB。因?yàn)閮煞N方法在降噪方面作用相當(dāng),因此需要進(jìn)一步權(quán)衡以體現(xiàn)典型設(shè)計(jì)的市場(chǎng)空間。

首先,信號(hào)平均方法沒有時(shí)間交織方法實(shí)現(xiàn)起來那么復(fù)雜。信號(hào)平均電路中四個(gè)ADC所需要的時(shí)鐘可以從一個(gè)阻性分配器、一個(gè)磁性分配器或是一個(gè)簡(jiǎn)單的1:4扇出的時(shí)鐘分配IC獲得。時(shí)間交織的方法需要使用至少兩個(gè)D觸發(fā)器來實(shí)現(xiàn)4分頻和90°間隔相序功能。在某些情況下,可能還需要四個(gè)附加觸發(fā)器緩沖定時(shí)信號(hào),以保持嚴(yán)格的時(shí)序。為了實(shí)現(xiàn)提高預(yù)期的6 dB SNR目標(biāo),時(shí)間交織方法可能需要使用數(shù)字濾波器,它要求實(shí)時(shí)乘法器和加法器(如果用于系統(tǒng)設(shè)計(jì),或者還需要一些處理時(shí)間)。然而信號(hào)平均的方法只需要一個(gè)實(shí)時(shí)加法器,從而真正減少了數(shù)字邏輯電路。

每一種降噪方法的有效性也必須仔細(xì)考慮。特別是必須了解每個(gè)通道的相關(guān)噪聲和帶寬水平。因?yàn)殡S著通道間相關(guān)噪聲增加,信號(hào)平均方法的有效性會(huì)越來越低。在抖動(dòng)和相位噪聲是主要噪聲源的系統(tǒng)中,存在相關(guān)噪聲的風(fēng)險(xiǎn)會(huì)影響SNR的提高。

時(shí)間交織方法實(shí)際上是在4倍帶寬范圍內(nèi)散布噪聲,然后濾除無用的120 MHz。在這種情況下,必須研究和掌握噪聲頻譜的寬帶特性。如果通道的噪聲頻譜內(nèi)容平均分布在整個(gè)160 MHz奈奎斯特頻帶,那么這種方法可以提高6 dB SNR。但是,如果噪聲分布主要集中在有用的40 MHz帶寬之內(nèi),那么提高6 dB SNR的目標(biāo)可能無法實(shí)現(xiàn)。

比較這兩種方法的另一個(gè)重要考慮因素是頻率規(guī)劃。如果使用一種單頻系統(tǒng),并且其輸入頻率在單ADC采樣速率(例如20 MHz)的1/4以上,則第2、第3、第4、第5、第6次諧波落在40 MHz有用頻帶之外。因此,這些高次諧波會(huì)被數(shù)字噪聲濾波器削減或?yàn)V除。此外,前面討論的鏡像雜散信號(hào)也會(huì)落在有用頻帶之外,從而被濾除。在多頻系統(tǒng)中,一些諧波成分也會(huì)落在有用帶寬之外,從而會(huì)減小系統(tǒng)的總諧波失真。

總之,信號(hào)平均方法提供了一種提高6 dB SNR的簡(jiǎn)單方法,而時(shí)間交織方法為開發(fā)系統(tǒng)體系結(jié)構(gòu)提供了一些值得考慮的好處。

多通道ADC系統(tǒng)的使用

多通道ADC在提高數(shù)字采集系統(tǒng)方面已經(jīng)起到了重要作用。成像系統(tǒng)通過對(duì)多路ADC進(jìn)行加和來優(yōu)化信號(hào)以提高清晰度。數(shù)字示波器制造商已經(jīng)開發(fā)了ADC時(shí)間交織方法以滿足高采樣速率的要求。其它使用頻分多址(FDMA)的接收系統(tǒng)也采用了多個(gè)ADC 通道對(duì)頻帶進(jìn)行劃分--減低對(duì)每個(gè)ADC輸入帶寬的需求,從而進(jìn)一步增大動(dòng)態(tài)范圍。為了節(jié)省功耗和尺寸,采用4通道ADC和8通道ADC 多通道IC封裝的ADC越來越多,正在利用它們開發(fā)多通道系統(tǒng)體系結(jié)構(gòu)以提供前所未有的功能和性能。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論