一般而言,用來驅動現今高分辨率類比/數碼轉換器的電源都是擁有數百歐姆或以上的AC或DC負載。因此,一個具備有高輸入阻抗(數百萬歐姆)和低輸出阻抗的運算放大器便成為ADC驅動器輸入的最佳選擇。ADC驅動器可作為緩沖器和低通濾波器之應用,以減低系統的整體雜訊。

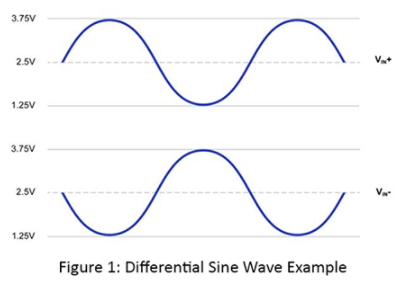

隨著訊號在電路板的布線和冗長電纜上傳送,系統雜訊會積聚在訊號里,而一個差動ADC會拒絕任何看來像共模電壓的訊號雜訊。相比起單端的訊號,采用差動訊號有好幾個優點。首先,差動訊號可將ADC的動態范圍增大一倍。其次,它可提供更佳的諧波失真效能。現今有幾個方法可從一個雙重運算放大器配置產生出差動訊號。其中一種方法是采用單端/差動轉換技術,而另一種則需動用差動輸入源。為了利用完全的ADC的動態范圍,ADC的輸入必須被驅動至滿刻度的輸入電壓。

本文將會討論三種不同的ADC驅動器架構:單到單、單端到差動和差動到差動。主要目的是希望能扼要地提供一切用ADC介接高效能運算放大器的資料。

訊號路徑的必要組件

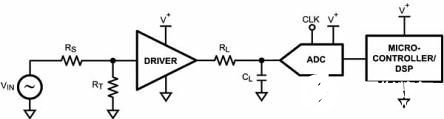

以下會把訊號路徑中的類比前端設計之幾個組成部份一起討論。典型訊號路徑的類比前端包括有一個用來驅動ADC的運算放大器、一個RC濾波器、ADC和微控制器或數碼訊號處理器(DSP)。

圖1:典型訊號路徑的類比前端方塊圖

現實世界中的輸入源會帶有不理想的阻抗,因此需依賴一個很低輸出阻抗的緩沖放大器來驅動ADC的輸入。然而,外置的RL-CL濾波器會作用為一個抗疊頻濾波器,以幫助減低ADC驅動器的雜訊頻寬,以及緩沖由ADC取樣和保持電路所引致的充電瞬時。為了盡量減低輸入電壓的跌降,外置的并列電容(CL)必須比ADC的內置輸入電容大10倍,而同時外置的串行電容(RL)亦必須夠大以固定發生在運算放大器輸出的相位延遲,從而維持電路的穩定性。對于大部份的應用而言,在運算放大器輸出和ADC輸入之間用一個串行隔離電阻來連接,都可以帶來益處,因為這個串行電阻可有助限制運算放大器的輸出電流,而為這個串行電阻選定數值是一項非常重要的工作。

一個比較高的電阻值將會增加運算放大器的負載阻抗,從而改善運算放大器的整體諧波失真(THD)效能。可是,ADC通常都較喜歡以一個低阻抗的源來驅動。因此,必須為這個串行電阻找出最佳的數值,才能一同為運算放大器和ADC帶來最佳的THD、SNR和SFDR效能。當把ADC連接到一個運算放大器時,最重要是了解將會影響到效能的規格。現今的ADC規格,例如是THD、SNR、設置時間和SFDR等,它們均對濾波、測量、視頻和重現應用很關鍵。高效能運算放大器的設置時間、THD和雜訊效能必須比被驅動的ADC的效能更好,以確保系統的精確度以及將錯誤減至最低或甚至消除。

在本文中, LMH6611或LMH6618單一運算放大器會被用來驅動單通道的ADC121S101 類比/數碼轉換器,而另一方面,LMH6612或LMH6619雙重運算放大器會被用來驅動差動輸入的ADC121S625或ADC121S705類比/數碼轉換器。這些放大器的應用范圍相當廣泛,特別適用于要求高速、低供電電流、低雜訊,以及需要驅動復雜ADC和視頻負載的應用。

運算放大器和ADC的重要規格

在現實中,有些系統應用會要求低THD、低SFDR和寬闊動態范圍(SNR),而另一些則可能要求高SNR,并且可能會犧牲THD和SFDR的效能來換取更佳的雜訊效能。

對于運算放大器和ADC而言,雜訊都是一項很重要的規格。這里有三個主要影響ADC整體效能的雜訊來源:量化雜訊--是由ADC本身所產生的雜訊(尤其在較高的頻率下),以及由應用電路所產生的雜訊。輸入源的阻抗可影響運算放大器的雜訊效能。理論上,ADC的訊號與雜訊的比例(SNR)可用下列算式計算出來:

![]()

算式中的N是ADC的分辨率。例如根據這條算式,一個12位的ADC便擁有74dB的SNR。可是,實際的SNR數值會大約是72dB。為獲得更佳的SNR,ADC驅動器雜訊應該愈小愈好。LMH6611/LMH6612/LMH6618/LMH6619的低電壓雜訊僅為10 nV/ 。

運算放大器和ADC的整體設置時間必須在1 LSB之內,而LMH6618/LMH6619和LMH6611/LMH6612的0.01%設置時間分別為120ns和100ns。

此外,ADC驅動器的THD必須低于ADC。LMH6618/LMH6619在2VPP輸出和100 KHz輸入頻率時的SFDR為100dBc,而LMH6611/LMH6612在2VPP輸出和1 MHz 輸入頻率時的SFDR則為90dBc。

訊號/雜訊比和失真(SINAD)是一個參數,它結合了SNR和THD這兩個規格。SINAD是指輸出訊號的RMS值與所有其它低于時鐘頻率一半的光譜成份之RMS值之比例,這包括諧波但不包括DC,以及可憑下列算式從SNR和THR中計算出來:

由于SINAD是將輸入頻率與所有不良頻率成份作比較,所以它其實是ADC動態效能的一個整體性測量。以下的部份將會詳細討論三種不同的ADC驅動器架構。

1. 單到單ADC驅動器

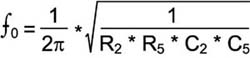

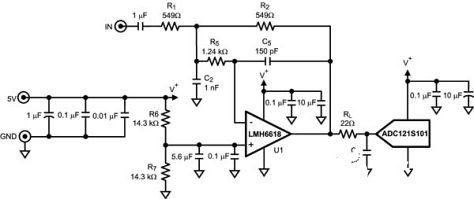

這個架構有一個單端式輸入源接駁到運算放大器的輸入,然后此運算放大器的單端式輸出會再接駁到ADC的單端式輸入。僅僅10 nV/ 的低雜訊和130 MHz的寬闊頻寬促使LMH6618成為驅動12位ADC121S101 500KSPS至1MSPS 類比/數碼轉換器的首選,這個ADC擁有一個具備內置取樣和保持電路的逐次逼近架構(successive approximation architecture)。圖2所示為一個驅動ADC121S101的LMH6618之原理圖,所用的是具備有增益-1(反相)的二階多重反饋配置。圖中的反相配置比起非反相的為佳,原因是反相配置可提供更多的線性輸出回應。表1列出LMH6611或LMH6618與ADC121S101組合后的效能資料。圖3表示出在f = 200 KHz時的LMH6611和ADC121S101組合之FET繪圖。ADC驅動器的500 KHz截止頻率可從下列算式計算出來:

運算放大器的增益由下列算式設定:

![]()

圖2:單到單ADC驅動器

圖3:單到單ADC驅動器的FET繪圖

表1:LMH6611/LMH6618與ADC121S101組合后的效能

2. 單端到差動ADC驅動器

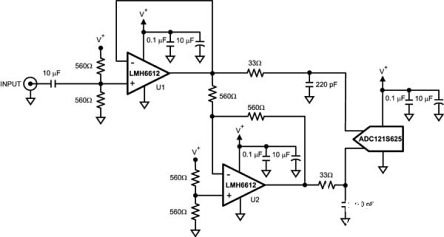

圖4中的單端到差動ADC驅動器采用了LMH6612雙重運算放大器來緩沖一個單端源,以便驅動一個具備有差動輸入的ADC。其中一個運算放大器會被配置成一個單位增益緩沖器,并負責驅動運算放大器U2的反相(IN-)輸入和ADC121S625的非反相(IN+)輸入。U2把輸入訊號倒向并驅動ADC121S625的反相輸入。U2的增益配置為+2,因此可在無需犧牲THD效能下減低雜訊。至于2.5V的共模電壓會同時設立在兩個運算放大器U1和U2的非反相輸入。

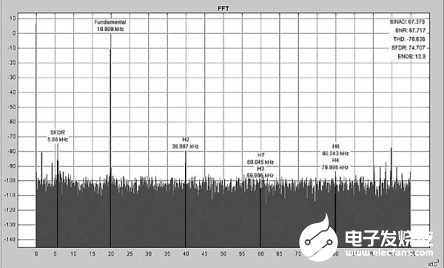

當0至VREF的單端輸入訊號被AC耦合到運算放大器的非反相終端時,以及當每一個運算放大器的非反相終端在中標量2.5V下被偏壓時,這種配置便可產生2.5Vpp的差動輸出訊號。此外,兩個輸出RC抗疊頻濾波器會同時使用在U1和U2的輸出與ADC121S625的輸入之間,以減輕來自輸入源的不良高頻雜訊之影響。每一個RC濾波器均具備有約22 MHz.的截止頻率。圖5表示出在f = 20 KHz時LMH6612和ADC121S625組合的FET繪圖。

圖4:單端到差動ADC驅動器

圖5:單端到差動ADC驅動器的FET繪圖

表2:LMH6612/LMH6619與ADC121S625兩個組合的效能資料

3. 差動到差動ADC驅動器

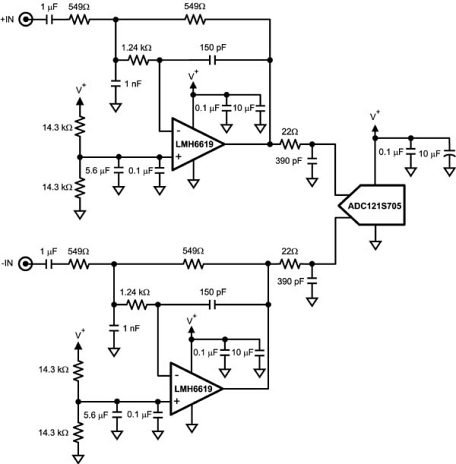

LMH6619雙重運算放大器可以被配置成一個差動到差動的ADC驅動器,以便用來將一個差動源緩沖到一個差動輸入ADC,正如圖6所示。該差動到差動ADC驅動器可用兩個單到單ADC驅動器組成。這些驅動器的每一個輸出會接駁到差動ADC的個別輸入。在這里每一個單到單ADC驅動器都采用相同的組件,并且配置成增益-1(反相)。

圖6:差動到差動ADC驅動器

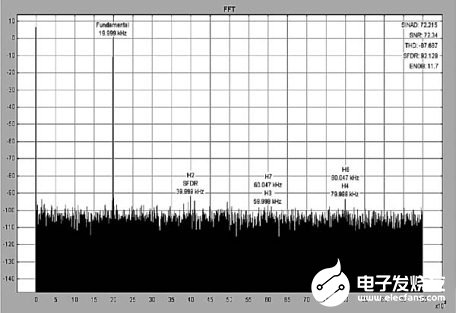

下表分別總結出LMH6612和LMH6619與ADC121S625和ADC121S705這四個組合的效能。表中同時包括有LMH6612和LMH6619分別在2個不同的頻率下連接到兩個ADC的資料。為了用盡ADC的整個動態范圍,25VPP的最高輸入會施加到ADC的輸入。圖7表示出在f = 20 KHz時LMH6612和ADC121S625組合的FET繪圖。

表3:LMH6612和LMH6619分別連接到ADC121S625和ADC121S70后的效能

圖7:差動到差動 ADC驅動器的FET繪圖

接地和電路板布局考慮

將輸入源接地連接到電源接地是非常重要的。對于上述每一個的ADC驅動器配置,當建立電阻器網絡以確保差動輸出擁有相同增益時,必須同時考慮訊號源的阻抗。例如,一個音頻精確訊號產生器擁有22Ω的源阻抗,而電路板則有一個50Ω的終端,因此設計人員必須調節增益和輸入,以便能在運算放大器的輸出處獲取所需的訊號。

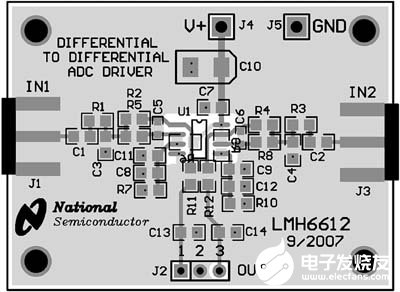

為了獲得最佳的高頻效能,以下是一些電路板布局的建議:

·將ADC和放大器放置得愈接近愈好

·將供電旁路電容器盡量放近裝置(距離少于1英寸)

·采用表面黏著而非穿孔式組件,以及采用接地和電源層

·盡量減少布線的長度

·為冗長布線采用終端式傳輸線

圖8:差動到差動ADC驅動器的電路板布局

LMH6612/LMH6619只消耗僅6.5mA/2.5Ma的電流,相比起市面上大部份的全差動放大器少了超過20mA。采用LMH6611/LMH6612/LMH6618/LMH6619的主要優點是低功率和低成本。當中,LMH6611和LMH6612最適合使用在那些在奈奎斯特(Nyquist)頻率20 KHz至2 MHz下運行的應用,而LMH6618和LMH6619則最適合使用在那些在奈奎斯特頻率20 KHz至500 MHz下運行的應用。

總括而言,本文涵蓋了所有重要的考慮因素,包括外置RL-CL網絡的選擇以及運算放大器的關鍵參數:象是THD、設置時間和雜訊,這些都是在把高效能運算放大器連接到ADC時所必須考慮的參數。此外,本文還詳細討論了三種不同的ADC驅動器配置,并且在實驗室進行了嚴謹的測試。最后,本文亦論及接地和電路板布局時需要注意的地方,從而改善系統的效能。

責任編輯:gt

電子發燒友App

電子發燒友App

評論