有大神知道12位ADC采樣保持器里面的電容量級是多少嗎?因為設計電路的時候要使用抗混疊濾波器,需要考慮采樣保持器電容與抗混疊濾波電容的大小關系

2023-11-02 06:27:44

LTM9002采用15mmx 11.25mmLGA 封裝,該器件運用一種集成系統級封裝(SIP)技術,包括一個雙通道高速14位A/D轉換器、匹配網絡、抗混疊濾波器和兩個低噪聲、差分放大器。它專為

2021-04-16 06:17:10

簡介當模數轉換器(ADC)的模擬輸入被驅動至額定滿量程輸入電壓時,ADC提供最佳性能。但在許多應用中,最大可用信號與額定電壓不同,可能需要調整。用于滿足這一要求的器件之一是可變增益放大器(VGA

2018-10-23 11:43:54

和放大器噪聲都會增加,結果會降低轉換器的性能。要維持性能不變,就需要采用基于高損耗阻性元件的高階抗混疊濾波器。

在設計轉換器前端時,一定要考慮噪聲頻譜密度(NSD)。噪聲頻譜密度通常以nV/√Hz

2023-12-19 06:18:48

針對此問題的解決方案:那就是抗混疊濾波器。抗混疊濾波器大多數ADC之前都會有一個抗混疊濾波器,而這個濾波器與衰減信號(超過了所需帶寬)的低通濾波器沒有什么不同。如圖4所示,一個理想抗混疊濾波器的響應

2018-09-06 16:00:00

提升信噪比,二是可以放寬對位于ADC之前的抗混疊模擬濾波器的要求。抗混疊濾波器:分區困境理想情況下,與ADC相關的濾波器,特別是那些負責解決頻譜混疊問題的濾波器,相比其精度,其幅度響應帶寬必須盡可能

2021-08-04 07:00:00

你的抗混疊濾波器截止頻率。方程式1計算出單極、低通濾波器的截止頻率為-3dB:圖2.ADC輸入上的單極、低通濾波器有時候,一個單極、低通濾波器也許還不夠。諸如振動感測等應用也許是用更少的過采樣來分析

2018-09-05 14:52:59

相當高的采樣率,即那些可以方便地集成到微控制器中的ADC 。因此,我可能必須放寬對衰減的要求,或者我可以考慮對抗混疊濾波器使用二階拓撲。結論顧名思義,抗混疊濾波器可減少對信號采樣時發生的混疊量。他們

2020-09-18 10:12:55

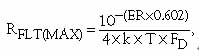

的俠士們介紹下如何在多個常用IF頻率下采用諧振法將采樣保持阻抗變換為可預測性的負載,從而更精確地設計抗混疊濾波器。 開關電容ADC為了降低功耗,開關電容ADC省掉了ADC前端中的緩沖。 ADC采樣保持

2019-01-08 11:17:19

`摘要在任何一個設計人員的工具箱里,集成電路放大器都是最基本的構件模塊之一,它是目前市面上最全能的產品之一。放大器具有多項功能,如驅動ADC,驅動多個視頻負載,作為視頻或其它類型濾波器,驅動高速儀器

2011-08-04 09:30:32

最后兩個步驟:配置輸入網絡以實現最大輸入信號和抗混疊,設計輸出網絡以實現阻抗轉換。 AD8338 輸入網絡對于該設計,差分輸出幅度為±1.0 V。在工廠默認設置、內部 500 Ω電阻和最大增益條件下

2020-07-18 07:00:00

前有個工具能精調您的選擇會怎么樣?模擬濾波器向導就是這樣一種用于現實運算放大器的實用設計工具。這款工具讓您不必再苦尋濾波器建議,助您設計出具備所需特性的低通、高通或帶通濾波器,且準備時間更短(圖1

2018-10-26 11:25:35

,作為高頻信號采樣系統中的抗混疊濾波器使

在信號輸入端設置一個高頻變壓器將單端信號轉換為差分信號; 其輸出信號將流入差分放大器ADL5565 ( 其增益為6 dB、12 dB、15.5 dB 可選

2023-11-23 06:01:47

HiADS1675 ,內部有2種濾波器 ,delta-sigma (ΔΣ) 是用做抗混疊濾波器嗎?或者還用作其他? 有沒有相關的詳細文章介紹?

2019-05-22 06:17:18

喜 我有幾個問題。 1. Acc的順序抗混疊濾波器是什么? 2.陀螺的順序抗混疊濾波器是什么? 3.如果截止頻率高于nyquist頻率,DLPF1濾波器如何幫助我? 謝謝, 阿米爾

2018-09-11 16:41:19

DSP的ADC前端除了有抗混疊濾波器還有什么??

2012-10-14 21:02:50

不同的方法,其工作方式與開關模式電源非常相似(圖 2)。圖 2:D 類放大器將模擬輸入轉換為 PWM 波形,以完全打開或關閉 FET 開關。輸出低通濾波器可恢復揚聲器的模擬波形。(圖片來源

2018-12-21 10:28:21

內部抗混疊濾波器的Bode圖?編輯:antony_css于2015年2月17日8:26 PM編輯:antony_css于2015年2月17日下午8:27 以上來自于谷歌翻譯 以下為原文I am

2018-10-24 11:28:42

你好,我正在使用 LIS2DTW12,但我不太了解截止頻率是多少。我很困惑,抗混疊濾波器已切斷固定為 400 Hz 的頻率:那么在這張表中,LPF1 和 LPF2 之后的截止頻率似乎是 ODR/2

2022-12-27 08:10:16

放大器,抗混疊濾波器,ADC驅動電路,模擬開關以及高精密電壓基準等,并且能在單電源供電環境下提供±10V/ ±5V/ ±2.5V等可編程輸入范圍。高集成度的設計使得這種ADC更像一塊電壓采集器,大大

2019-08-06 04:45:15

我的同事Ryan Andrews在其關于抗混疊濾波器的博文中解釋道,Σ-Δ ADC中的數字濾波器具有另外一項抽取功能。這些濾波器以低很多的速率(fDR)通過被稱為過采樣率(OSR)的因子抽取調制器采樣頻率

2018-08-30 15:05:47

各位好!想請教如下問題:在資料中,看到說△-∑型ADC采用過采樣技術,因此大部分情況下可以用一個簡單地RC低通濾波器來進行抗混疊濾波。我想請教的是:用RC低通濾波的話,轉折頻率是可以滿足,但是RC

2019-05-17 13:30:09

`內容簡介 《測量電子電路設計:濾波器篇(從濾波器設計到鎖相放大器的應用)》是“圖解實用電子技術叢書”之一,也是《測量電子電路設計——模擬篇》的姊妹篇,主要介紹如何從放大了的信號中除去有害噪聲,提取

2017-07-05 18:20:01

主要特性。由于鎖相放大器的目的是從高噪聲環境中恢復信號,因此在設計實驗時最重要的一點就是測試裝置中的噪聲。因此,我們還將在本文中回顧可能的噪聲源。最后,我們將介紹市場上一些鎖相放大器。抗混疊濾波器:將采樣

2020-09-18 14:05:33

AD7606簡介:AD7606/AD7606-6/AD7606-4為16位同步采樣模數數據采集系統(DAS),分別有 8、6、4個采集通道。片上集成模擬輸入箝位保護、二階抗混疊濾波器、跟蹤保持放大器

2018-11-01 09:25:42

較高頻率(超出Nyquist頻率),減少或消除混疊效應。在放大器輸入之前,抗混疊濾波必須是純模擬濾波。通常一個簡單的RC濾波器就足夠了,如圖13所示。無需復雜的濾波器架構。不要將放大器配置為有源濾波器

2020-01-08 07:00:00

在第二個奈奎斯特區域中,SFDR > 69 dBFs,SNR > 67 dBFS交流和直流耦合接口的示例展示抗混疊濾波器設計和性能增益討論了為實現最佳性能而需考慮的放大器電源設計注意事項`

2015-05-11 10:33:40

奎斯特區域中,SFDR > 69 dBFs,SNR > 67 dBFS交流和直流耦合接口的示例展示抗混疊濾波器設計和性能增益討論了為實現最佳性能而需考慮的放大器電源設計注意事項

2018-08-09 08:38:52

,如減少電阻和電容的面積技術。這對于適當地集成到空間受限的應用中,同時不影響靜態功率是至關重要的。權衡:THD+N 與 Iq在許多設計中,D 類音頻放大器通常采用使用環路濾波器、PWM和開關功率級

2022-12-23 09:26:57

一般在ADC前端都會加抗混疊濾波器。但是,如果不加抗混疊濾波器的話,ADC采集到的信號頻譜是不是由無限寬的頻譜疊加得到的?比如我拿一個50MHz的ADC采集空中信號,是不是3GHz的信號也會混疊到我采集到的信號中?希望有大神能解答一下,謝謝啦~

2016-11-17 15:22:15

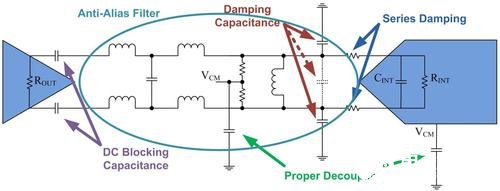

`集成放大器和AAF的ADC模擬輸入網絡`

2021-04-06 09:32:04

不同濾波器頻率響應的比較通用的A/D轉換器有:用于中等速率的SAR (逐次逼近) ADC;用于高速到超高速率的閃速ADC;用于低速系統的Σ-Δ ADC。它們都需要抗混疊濾波器,對濾波器的要求取決于轉換

2019-01-02 19:03:43

在使用AD9625的開發板時,還需不需要在前端加驅動電路或者驅動放大器?還有有沒有合適的抗混疊濾波器適合AD9625開發板的,可以推薦一下嗎?

2023-12-11 08:29:10

通常需要比 LPF1 更寬的帶寬。該濾波器還有助于將緩沖器的噪聲貢獻降至最低。如何使用LTspice模擬 SAR ADC 模擬輸入?圖 1. 模擬放大器和 ADC 之間的接口有助于確定噪聲和建立時間之間的權衡。

2022-04-12 17:45:54

LTC1569簡介LTC1569的引腳功能LTC1569的工作模式利用LTC1569實現抗混疊濾波應用LTC1569設計低通濾波器的注意事項

2021-04-07 06:33:38

AFAIK IIS2DH 沒有模擬抗混疊濾波器。如果我使用低 ODR 設置并且輸入信號頻率高于 ODR/2,是否會出現混疊?因為在我們的測試中,我們經常在信號輸出信號中出現尖峰。如果是這種情況,我們只能提高采樣率嗎?

2022-12-16 06:38:27

(SNR)。 例如,請思考圖1 所示低通濾波器實施。電阻傳感器通過一個低通濾波器網絡差動連接至一個高阻抗儀表放大器,而低通濾波器網絡由 RSX 和 CCM 組成。理想情況下,如果每條輸入支線的 CCM

2018-09-19 14:21:21

)=(1/4)* 2.02 /(s + 2.02)第二階段僅考慮運算放大器((2.2uF // 150kOhms)/(150kOhms)比率):G1(s)= 3.03 /(s + 3.03)考慮RC濾波器的輸出級:G2 = 1 /(sRC + 1)= 45.45 /(s + 45.45)

2018-08-16 22:33:12

傳統的窄帶無線接收機,DVGA+抗混疊濾波器+ADC 鏈路的設計中,我們默認ADC 為高阻態,在仿真抗混疊濾波器的時候忽略ADC 內阻帶來的影響。但隨著無線技術的日新月異,所需支持的信號帶寬越來越寬,相應的信號頻率也越來越高,在這樣的情況下ADC 隨頻率變化的內阻將無法被忽視。

2019-08-20 07:30:05

我想用AD9467進行射頻信號的欠采樣處理,如何設計前端的調理電路來保證其抗混疊和阻抗匹配呢?前端射頻信號是500MHz±5MHz的信號,經過500±6MHz的帶通濾波器和射頻放大器對信號進行濾波

2023-12-11 06:14:17

濾波器的設計方法有多種,頻域采樣的設計方法可對局部頻譜進行整形,適合幅頻均衡的應用。【關鍵詞】:抗混疊濾波器,設計方法,均衡方案,幅頻響應,離散時間系統,離散時間濾波器,方案選擇,數字,實現問題,功放

2010-05-06 08:53:58

用欠采樣,混疊使得AD系統作為混頻器工作。 本應用筆記討論數據采樣系統的不同濾波要求,介紹混疊以及用于抗混疊的不同類型濾波器。濾波是一種我們往往視為當然的常見過程。我們在打電話時,接收器濾除其它所有信道

2019-07-30 06:11:02

輸入85MHZ中頻,帶寬20MHZ(起始頻率:75MHZ;截止頻率:95MHZ)的中頻信號給AD9649;想設計一個無源抗混疊濾波器;請高手給予指點!

2015-04-23 15:19:28

我想把一個0~100mv電壓信號放大到0~5v 用什么型號運算放大器比較好,之后連接濾波器并且輸入到ad轉換器上需要的低通濾波器怎么選擇呢?

2017-06-20 17:24:46

本文對有源抗混疊濾波電路對驅動運放的要求,進行了分析,分別從高頻參數單位增益帶寬和高速參數建立時間,壓擺率以及運放的電流驅動能力,分析了系統對驅動放大器的要求。

2021-04-07 06:09:16

(ADC)前面有一個抗鋸齒(低通)濾波器,或者在數模轉換器(DAC)后面有一個抗鏡像(低通)濾波器。這種模擬濾波還可以在信號到達ADC之前或者離開DAC之后,消除疊加在信號上面的高頻噪聲。如果ADC的輸入

2019-08-20 07:46:51

模擬濾波器在電子信號合成系統中應用廣泛,可為ADC提供抗混疊和降噪,為DAC提供信號重建濾波1。不同的設計要求需要使用不同的濾波器架構,常用的濾波器有貝塞爾、巴特沃思以及橢圓濾波器。

2019-08-14 06:14:56

高性能模式下使用 3.3kHz ODR,模擬抗混疊濾波器帶寬設置為 1.5kHz,數字濾波器設置為 ODR/2。在生成的頻譜圖中,頻率掃描信號在多次穿過 ODR/2、ODR 和 1.5*ODR 后混疊

2022-12-15 08:14:24

DN16- 用于抗混疊應用的開關電容低通濾波器

2019-07-08 09:21:14

Electronics)在此電路中,使用反向放大器配置是一項優勢,因為放大器輸入級的共模電壓將保持固定的 2.5 V。緊跟 ADA4622-1 放大器的是一個 250 kHz 的 1 階濾波器。該

2018-11-29 17:52:59

"ADC 用抗混疊濾波器設計"。EDN,2006 年。Walsh, Alan。 精密SAR 型模數轉換器的前端放大器和RC 濾 波器設計。Analog Dialogue,第46 卷

2018-10-16 18:45:40

和C的值。圖1顯示了一個典型的放大器、單極點RC濾波器和ADC。ADC輸入構成驅動電路的開關電容負載。其10 MHz輸入帶寬意味著需要在寬帶寬內保證低噪聲以獲得良好的信噪比(SNR)。RC網絡限制輸入

2019-12-08 08:00:00

最初,視頻濾波器是一個無源的LC電路,現在,將放大器與RC濾波器結合起來,可以獲得尺寸更小、更高效的設計。此外,二十世紀60年代發展起來的靈敏度分析與預失真方法也克服了早期濾波器性能較差的弱點

2021-05-14 07:55:00

無源抗混疊濾波器的驅動有源抗混疊濾波器的驅動

2021-04-21 06:53:00

濾波器用作抗混疊濾波器。通過衰減較高頻率(超出Nyquist頻率),減少或消除混疊效應。 在放大器輸入之前,抗混疊濾波必須是純模擬濾波。通常一個簡單的RC濾波器就足夠了,如圖13所示。無需復雜的濾波器

2019-09-26 08:30:00

頻譜分析,僅僅是簡單中值濾波或者FIR濾波后用做控制律的運算輸入,那ADC前端的濾波器的截止頻率還有必要設到fs/2嗎?換句話說,抗混疊濾波器,什么時候可以不用?

2018-10-09 16:08:19

在使用AD9625的開發板時,還需不需要在前端加驅動電路或者驅動放大器?還有有沒有合適的抗混疊濾波器適合AD9625開發板的,可以推薦一下嗎?

2018-08-03 08:00:18

如何利用開關電容濾波器實現抗混疊濾波?

2021-04-23 06:12:02

再設計電路時,差分信號在介入差分ADC時,需要在AINN和AINP輸入引腳前加入一階抗混疊濾波器,濾除高頻干擾,請問專家應該如何設計,或則有什么參考資料,第一次設計抗混疊濾波器!謝謝

2018-11-14 11:07:35

運算放大器構成的帶通濾波器

2019-09-30 05:35:51

小弟在連接放大器和低通濾波器的時候輸出波形失真了,輸入信號5uv 50Hz的正弦信號。濾波器帶寬在100Hz,增益7db。用理想100Hz帶寬的理想濾波器時就不會失真,趕緊問題出在阻抗匹配

2021-06-24 06:15:09

ADC電路需要在前端設計專用的多階有源濾波器,濾掉頻率超過fs/2的信號。(注:Σ-Δ型ADC理論上也需要抗混疊濾波器,但是由于其過采樣特性及內部數字濾波器的帶外衰減特性,其對抗混疊濾波器的設計要求要低

2022-11-07 06:09:13

高精度SAR模數轉換器的抗混疊濾波考慮因素

2021-01-11 07:53:43

連接,這就會引起失真。務必將AAF的阻帶區間規定為平坦的,因為寬帶噪聲仍有可能折回帶內(見圖8)。

圖8. 抗混疊濾波器

多數轉換器具有很寬的模擬輸入帶寬。如果不使用AAF,混疊會降低動態范圍。AAF

2023-12-18 07:42:00

ADC的全部額定帶寬內,輸入阻抗都是恒定的。 設計抗混疊濾波器(AAF)時應當注意,過多的元件可能會導致容差不匹配,進而產生偶數階失真。電感并非特性相同,不同電感的響應可能大不相同。廉價、低質量的電感一般

2018-01-23 16:01:44

良好的焊接連接,這就會引起失真。務必將AAF的阻帶區間規定為平坦的,因為寬帶噪聲仍有可能折回帶內(見圖8)。圖8. 抗混疊濾波器 多數轉換器具有很寬的模擬輸入帶寬。如果不使用AAF,混疊會降低動態范圍

2018-09-17 15:38:24

連接,這就會引起失真。務必將AAF的阻帶區間規定為平坦的,因為寬帶噪聲仍有可能折回帶內(見圖8)。圖8. 抗混疊濾波器多數轉換器具有很寬的模擬輸入帶寬。如果不使用AAF,混疊會降低動態范圍。AAF應按照等于

2018-10-18 11:23:57

第二個奈奎斯特區域中,SFDR > 80 dBFs,SNR > 68 dBFS交流和直流耦合接口的示例展示抗混疊濾波器設計和性能增益討論了為實現最佳性能而需考慮的放大器電源設計注意事項

2018-08-03 06:00:28

后的平滑濾波;以及在語音識別的研究中,為提取語音頻譜而設置的帶通濾波器組等。理想的濾波器是難以實現的,通常只能以物理可實現的高階濾波網絡逼近其特性,如巴特沃斯和切比雪夫等逼近。隨著集成電路技術的發展

2009-12-05 09:08:06

低電壓CMOS模擬集成運算放大器輸入級的研究摘 要:對于低電壓CMOS模擬集成運算放大器輸入級所面臨的問題,我們提出了三種解決的方法,其中包括輸出為Rail—

2010-05-15 17:51:27 23

23 模擬濾波器注入噪聲原理及設計

有時候,事情根本沒有意義!例如,您 Δ-Σ ADC 輸入端 RC 濾波器或放大器的低通濾波器會產生更大噪聲的數字輸出

2010-03-19 17:00:33 1323

1323

如何使用模擬濾波器注入噪聲

例如,您 Δ-Σ ADC 輸入端 RC 濾波器或放大器的低通濾波器會產生更大噪聲的數字輸出。難道您沒有設計過降低噪聲的

2010-03-23 08:57:02 749

749 ,將模擬信號轉換為數字信號,在開關上以高頻進行開關,由此實現對輸入信號的放大。 D類放大器的組成主要包括輸入級(輸入濾波器)、開關電路、輸出濾波器和反饋電路等部分。 輸入級:輸入級主要用于濾除輸入信號中的高頻成分,并對信

2024-02-01 10:58:38 235

235

電子發燒友App

電子發燒友App

評論