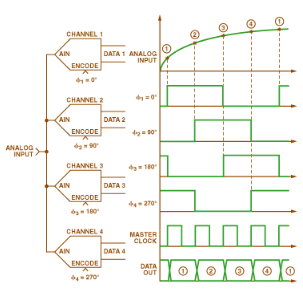

運(yùn)用時(shí)序交錯(cuò)式類(lèi)比數(shù)位轉(zhuǎn)換器(timeinterleavedADC)在每秒高達(dá)數(shù)十億次的同步取樣類(lèi)比訊號(hào)是一個(gè)技術(shù)上的挑戰(zhàn),除此之外,對(duì)於混合訊號(hào)電路的設(shè)計(jì)也需要非常謹(jǐn)慎小心。基本上,時(shí)序交錯(cuò)的目標(biāo)是利用轉(zhuǎn)換器數(shù)目與取樣頻率相乘而不影響解析度以及動(dòng)態(tài)的效能。

本文將探討運(yùn)用時(shí)序交錯(cuò)式類(lèi)比數(shù)位轉(zhuǎn)換器時(shí)所出現(xiàn)的技術(shù)挑戰(zhàn),并對(duì)此提供實(shí)用的系統(tǒng)設(shè)計(jì)解決方案。本文也將說(shuō)明可以解決目前已知問(wèn)題的創(chuàng)新元件的特色及設(shè)計(jì)技術(shù)。同時(shí)利用快速傅立葉轉(zhuǎn)換(FFT)計(jì)算法算出7GSPS速率及兩個(gè)轉(zhuǎn)換器晶片在「交錯(cuò)解決方案」下的結(jié)果。最後將說(shuō)明為達(dá)成高效能所需的時(shí)脈源及驅(qū)動(dòng)放大器之支援電路圖應(yīng)用。

需要更高的取樣速度

何時(shí)以及為何增加取樣的頻率是具有優(yōu)勢(shì)的呢?有多個(gè)答案可以回答這個(gè)問(wèn)題。基本上,類(lèi)比數(shù)位轉(zhuǎn)換器的取樣速度會(huì)直接影響到瞬間頻寬,因?yàn)樗查g頻寬會(huì)在取樣的瞬間被數(shù)位化。根據(jù)Nyquist與Shannon的取樣定理表示,最大允許的取樣頻寬(BW)等於取樣頻率(FS)的一半。我們可以用以下的方程式表示:

BW=FS/2

速率為3GSPS的類(lèi)比數(shù)位轉(zhuǎn)換器能在一個(gè)取樣周期內(nèi)取樣15億赫茲的類(lèi)比訊號(hào)頻譜。讓取樣速度加倍的同時(shí)也會(huì)讓Nyquist頻寬加倍成為30億赫茲。藉由時(shí)序交錯(cuò)使取樣頻寬產(chǎn)生增加的結(jié)果對(duì)於很多應(yīng)用提供相當(dāng)?shù)闹妗Ee例來(lái)說(shuō),應(yīng)用時(shí)序交錯(cuò)的無(wú)線電收發(fā)機(jī)架構(gòu)就可以增加資訊訊號(hào)載波的數(shù)目,使得系統(tǒng)資料處理能力得到提升。增加取樣頻率同時(shí)也可以改善LiDAR測(cè)量系統(tǒng)(LiDAR系統(tǒng)依循飛行時(shí)間(TOF)原理而運(yùn)作)的解析度。基本上,飛行時(shí)間測(cè)量的不準(zhǔn)確度可以經(jīng)由減少有效取樣時(shí)脈周期的方式而降低。

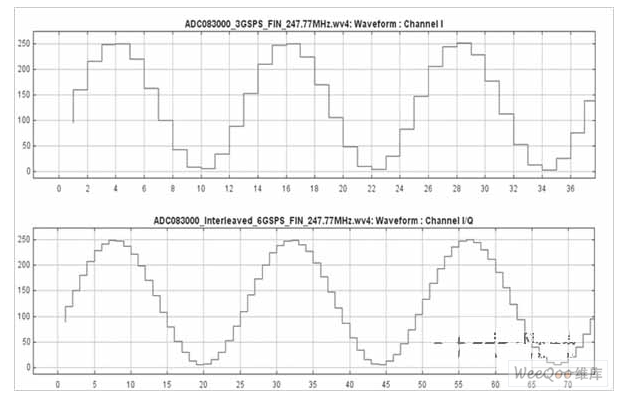

數(shù)位示波器也需要較高的取樣頻率對(duì)輸入頻率(FIN)的比值,才能更精準(zhǔn)的獲得復(fù)合式類(lèi)比或數(shù)位訊號(hào)。取樣頻率必須是FIN的最大值的數(shù)倍以上才能得到FIN的調(diào)和成分。舉例來(lái)說(shuō),如果在示波器取樣頻率不夠高的情況下,若較高位階的調(diào)和頻率在類(lèi)比數(shù)位轉(zhuǎn)換器Nyquist頻寬的范圍之外,那麼原本的方波將會(huì)變成正弦波的形式。

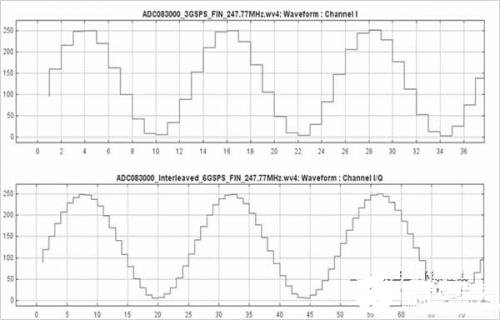

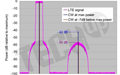

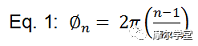

圖1:在速率3GSPS及速率6GSPS時(shí)針對(duì)247.77百萬(wàn)赫茲訊號(hào)取樣的時(shí)域測(cè)量波形圖。

圖1所示為示波器前端加倍取樣頻率所產(chǎn)生的優(yōu)勢(shì)。取樣類(lèi)比輸入訊號(hào)中速率6GSPS的取樣波形將得以更精準(zhǔn)地呈現(xiàn)出來(lái)。許多其他的測(cè)試儀器系統(tǒng),比方像是質(zhì)譜儀以及伽瑪射線望遠(yuǎn)鏡都是依賴(lài)較高的過(guò)度取樣與輸入頻率的比例來(lái)達(dá)成脈沖形狀的測(cè)量。

增加取樣頻率還可以獲得其它的優(yōu)點(diǎn)。過(guò)度取樣的訊號(hào)也能對(duì)數(shù)位濾波的過(guò)程中得到增益有所助益。基本上,類(lèi)比數(shù)位轉(zhuǎn)換器的雜訊底部擴(kuò)散涵蓋大部分的輸出頻寬。對(duì)一個(gè)固定的輸入頻寬采用兩倍的取樣頻率進(jìn)行取樣,能在動(dòng)態(tài)范圍中獲得3dB的改善。而每一次對(duì)取樣頻率進(jìn)行加倍也都能讓動(dòng)態(tài)范圍額外獲得3dB的改善。

時(shí)序交錯(cuò)所面臨的挑戰(zhàn)

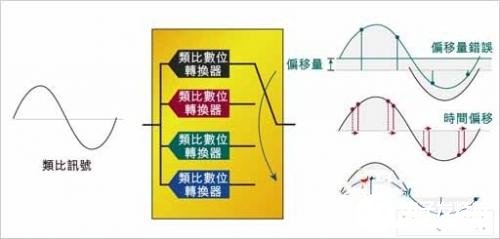

時(shí)序交錯(cuò)主要面臨的挑戰(zhàn)為頻道間做取樣時(shí)脈邊緣的精確相位校準(zhǔn),以及在積體電路之間與生俱來(lái)的制造變數(shù)補(bǔ)償?shù)膯?wèn)題。為了能精確的與增益匹配,各個(gè)分別類(lèi)比數(shù)位轉(zhuǎn)換器間的偏移量與時(shí)脈相位都將十分重要,特別是與頻率有關(guān)的參數(shù)更顯重要。除非這些參數(shù)能夠達(dá)到精確匹配,才能使動(dòng)態(tài)效能與解析度得以降低。圖2所示為三個(gè)主要的錯(cuò)誤來(lái)源。

圖2:交錯(cuò)是類(lèi)比數(shù)位轉(zhuǎn)換器在增益、偏移量、時(shí)序上的錯(cuò)誤。

一般而言,雙通道交錯(cuò)轉(zhuǎn)換器的系統(tǒng)需要類(lèi)比數(shù)位轉(zhuǎn)換器的輸入端取樣時(shí)脈產(chǎn)生1/2個(gè)時(shí)脈周期的時(shí)間平移。然而ADC083000類(lèi)比數(shù)位轉(zhuǎn)換器的架構(gòu)則使用晶片本身具備的交錯(cuò)技術(shù),并以時(shí)脈頻率相當(dāng)於取樣率一半的數(shù)值進(jìn)行運(yùn)作,也就是說(shuō)使用1.5GHZ的頻率來(lái)對(duì)應(yīng)3GSPS的速率。因此對(duì)於采用兩組ADC083000類(lèi)比數(shù)位轉(zhuǎn)換器的雙通道系統(tǒng)而言,類(lèi)比數(shù)位轉(zhuǎn)換器輸入取樣時(shí)脈邊緣必須是1/4個(gè)時(shí)脈周期的時(shí)間平移或是與其他邊緣產(chǎn)生90°的角度平移。對(duì)於頻率1.5GHZ時(shí)脈而言,相符合的數(shù)值為166.67ps.

時(shí)脈訊號(hào)的線路長(zhǎng)度可以經(jīng)由計(jì)算方式精確地得到1/4個(gè)時(shí)脈周期的相位平移。在FR-4的印刷電路板材料中,訊號(hào)可以20cm/ns的速率來(lái)傳遞,即每50ps傳遞1公分的距離。舉例來(lái)說(shuō),如果到一組類(lèi)比數(shù)位轉(zhuǎn)換器的時(shí)脈路徑比另一組長(zhǎng)3公分以上,那麼將會(huì)產(chǎn)生150ps的相位平移。要如何精確地達(dá)到額外16.67ps的時(shí)間平移將會(huì)是要面臨到的挑戰(zhàn)。

ADC083000類(lèi)比數(shù)位轉(zhuǎn)換器具有一個(gè)整合型的時(shí)脈相位校準(zhǔn)功能,這個(gè)功能可以讓使用者在輸入取樣時(shí)脈中加入一個(gè)延遲來(lái)平移其相位以便與另外一個(gè)類(lèi)比數(shù)位轉(zhuǎn)換器取樣時(shí)脈建立關(guān)聯(lián)性。類(lèi)比數(shù)位轉(zhuǎn)換器的時(shí)脈相位可以經(jīng)由內(nèi)建的兩組暫存器透過(guò)SPI匯流排進(jìn)行手動(dòng)校準(zhǔn)。其中的相位平移只可能發(fā)生在一個(gè)方向上來(lái)增加延遲現(xiàn)象。設(shè)計(jì)人員需要來(lái)決定這兩組分離的類(lèi)比數(shù)位轉(zhuǎn)換器中的哪一組是「在前方的」,并校準(zhǔn)其相位使取樣邊緣與另一組類(lèi)比數(shù)位轉(zhuǎn)換器的取樣邊緣端間產(chǎn)生90°的角度差。以提供Sub-picosecond等級(jí)的校準(zhǔn)解析度。

通道對(duì)通道的增益與偏移量匹配

在一個(gè)具備雙轉(zhuǎn)換器的交錯(cuò)系統(tǒng)中,假設(shè)輸入訊號(hào)在第一Nyquist范圍內(nèi)時(shí),因?yàn)橥ǖ涝鲆娌黄ヅ渌a(chǎn)生的錯(cuò)誤電壓值會(huì)造成在FS/2–FIN與FS/4+/-FIN位置上的影像突波。一組8位元的轉(zhuǎn)換器擁有28或256個(gè)編碼。假使轉(zhuǎn)換器的完整輸入范圍是1V的峰值對(duì)峰值,LSB的大小會(huì)等於1V/256=3.9mV的數(shù)值。而我們也能精準(zhǔn)的計(jì)算出對(duì)於1/2LSB所需的增益匹配值為0.2%.

ADC083000類(lèi)比數(shù)位轉(zhuǎn)換器的輸入端完整電壓值或增益能用9位元資料值來(lái)進(jìn)行線性及單調(diào)的校準(zhǔn)。700mVp-p的差異值可校準(zhǔn)的范圍為±20%,也就是說(shuō)可校準(zhǔn)的范圍在560mVp-p到840mVp-p之間。

840mV–560mV=280mV

29=512steps.280mV/512=546.88uV

微調(diào)校準(zhǔn)的角度可允許超過(guò)上述的0.2%增益匹配范圍。

在相鄰?fù)ǖ篱g的偏移量不匹配會(huì)產(chǎn)生一個(gè)錯(cuò)誤的電壓值,這將會(huì)造成在FS/2位置上的偏移量突波。由於偏移量突波是發(fā)生位於Nyquist帶的邊緣,因此雙通道系統(tǒng)的設(shè)計(jì)人員通常要規(guī)畫(huà)他們所需的系統(tǒng)頻率并將更大的心力著重於增益與相位匹配上。

然而,讓我們假設(shè)所需要的偏移量匹配也等於1/2的LSB基本標(biāo)準(zhǔn)值時(shí),ADC083000類(lèi)比數(shù)位轉(zhuǎn)換器的輸入端偏移量能透過(guò)線性及單調(diào)的校準(zhǔn),在9位元解析度中使0偏移量增加到45mV的偏移量。因此每一組編碼位階都提供了0.176mV的偏移量,同時(shí)9位元的解析度可以協(xié)助達(dá)成1/2LSB基本標(biāo)準(zhǔn)值的精確性。

數(shù)位輸出的同步

將兩組類(lèi)比數(shù)位轉(zhuǎn)換器的輸出資料串進(jìn)行同步有助於實(shí)現(xiàn)混合的取樣速度與頻寬。換句話說(shuō),如果在兩個(gè)獨(dú)立的轉(zhuǎn)換器之間發(fā)生同步損失的話,那麼我們將無(wú)法獲得有意義的資料。數(shù)以十億計(jì)的取樣類(lèi)比數(shù)位轉(zhuǎn)換器「解多工」輸出資料來(lái)降低數(shù)位輸出資料的速率。使用者可以依據(jù)所采用的FPGA技術(shù)對(duì)於資料處理的能力來(lái)選擇用2或4的資料速率來(lái)「解多工」。

輸出擷取時(shí)脈(DCLK)也可以被分割并設(shè)定為SDR或是DDR模式。然而對(duì)於解多工的方案,由於在每一個(gè)類(lèi)比數(shù)位轉(zhuǎn)換器的輸入取樣時(shí)脈與輸出擷取時(shí)脈間的聯(lián)系,這使得整個(gè)系統(tǒng)存在一些不確定的因素,因此設(shè)計(jì)人員需要考量更多。為了解決這個(gè)問(wèn)題,ADC083000類(lèi)比數(shù)位轉(zhuǎn)換器有能力藉由使用者供應(yīng)的DCLK_RST脈沖,來(lái)精確的重置其取樣時(shí)脈輸入到輸出擷取時(shí)脈輸出之間的關(guān)系。這項(xiàng)能力能夠讓系統(tǒng)中多個(gè)類(lèi)比數(shù)位轉(zhuǎn)換器同時(shí)擁有各自的輸出擷取時(shí)脈(以及資料)輸出轉(zhuǎn)換,并且可以共同分享輸入時(shí)脈以便進(jìn)行取樣,同時(shí),這將使得多個(gè)類(lèi)比數(shù)位轉(zhuǎn)換器之間的同步可以達(dá)成。

數(shù)位交錯(cuò)技術(shù)

類(lèi)比校正法是一種已被證實(shí)能傳遞高動(dòng)態(tài)范圍、具備整合能力的解決方案,這個(gè)解決方案具備整合性時(shí)脈相位、增益與偏移量校準(zhǔn)的功能,且已被證明能提供高精確度。

除了類(lèi)比校正技術(shù)之外,還有其他幾種可行的方法,舉例而言像是數(shù)位校正演算法也可用來(lái)處理交錯(cuò)資料。這幾種處理方法都能在不需要任何類(lèi)比偏移量、增益或是相位校正的前提下,能校正資料轉(zhuǎn)換器中數(shù)位不匹配的問(wèn)題。在理想狀態(tài)上,這些演算法都不需要對(duì)輸入訊號(hào)做任何校正或是先有基礎(chǔ)的觀念就能夠獨(dú)立運(yùn)作。除此之外,在數(shù)位偏移量、增益及相位校準(zhǔn)所需的時(shí)間則是系統(tǒng)最重要的運(yùn)算因子。

由SP元件公司所發(fā)展的數(shù)位後制處理引擎(這也是一套演算法)就能滿足上述的這些需求。SP元件公司的自動(dòng)數(shù)據(jù)交換(ADX)技術(shù),在不需特殊校正訊號(hào)或後期制作整理的條件下,會(huì)持續(xù)提供類(lèi)比數(shù)位轉(zhuǎn)換器在增益、偏移量與時(shí)間偏移錯(cuò)誤的估算。而這種演算法已經(jīng)應(yīng)用於修正靜態(tài)與動(dòng)態(tài)上不匹配錯(cuò)誤的問(wèn)題。

ADX技術(shù)能估算錯(cuò)誤并依據(jù)所有不匹配錯(cuò)誤來(lái)重建訊號(hào)。IP核心的錯(cuò)誤校正演算法,能在不限輸入訊號(hào)型式的前提下有效的執(zhí)行。數(shù)位訊號(hào)處理的結(jié)果為ADX核心之外的時(shí)序交錯(cuò)頻譜在與交錯(cuò)失真突波相關(guān)處不會(huì)出現(xiàn)明顯的不匹配錯(cuò)誤。

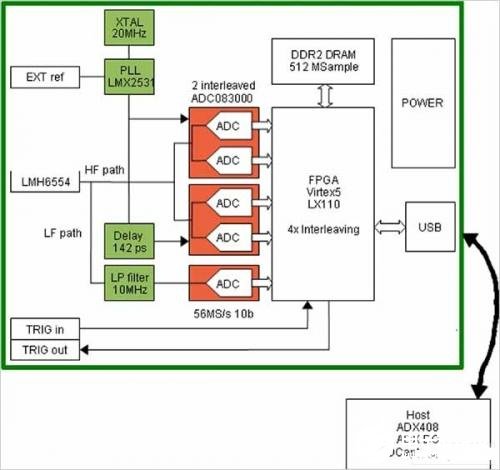

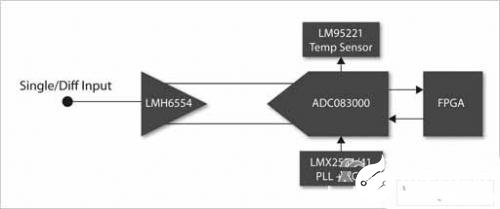

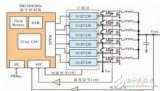

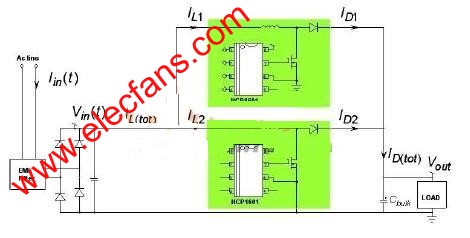

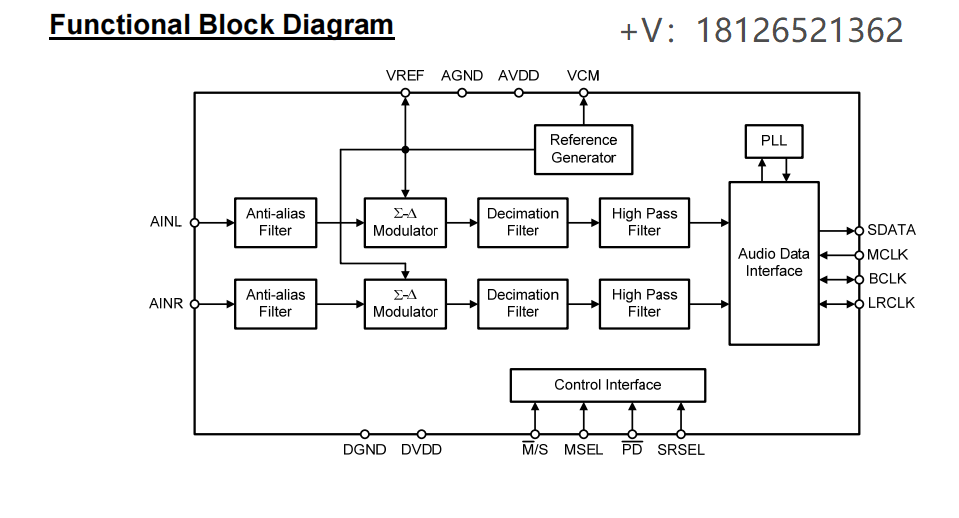

美國(guó)國(guó)家半導(dǎo)體公司在最近推出了一張配備兩個(gè)ADC083000具備3GSPS的8位元類(lèi)比數(shù)位轉(zhuǎn)換器公板,并將SP元件公司所開(kāi)發(fā)的演算法整合在公板上。其中采用ADX技術(shù)的資料轉(zhuǎn)換器為交錯(cuò)式,并嵌入公板上FPGA中。圖3所示為速率7GSPS數(shù)位卡的區(qū)塊示意圖。

圖3:具備LMX2531與LMH6554的ADQ108系統(tǒng)的區(qū)塊示意圖。

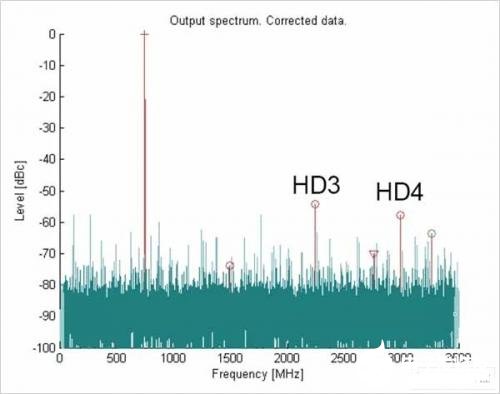

圖4:具備ADX的混合式類(lèi)比數(shù)位轉(zhuǎn)換器頻譜。

圖4所示為SP元件公司ADQ108資料收集卡的輸出頻譜效能圖。我們需要特別留意其中的峰值突波是來(lái)自於調(diào)和失真所造成的,且交錯(cuò)突波也已經(jīng)明顯的被削減掉。

超高速類(lèi)比數(shù)位轉(zhuǎn)換器之支援電路系統(tǒng)

藉由使用如ADC083000的資料轉(zhuǎn)換器能使系統(tǒng)達(dá)到高階的效能,但也必須先確認(rèn)支援的電路系統(tǒng)也具備足夠的效能。支援電路系統(tǒng)的重要關(guān)鍵元素如下:

1)高效能與低抖動(dòng)時(shí)脈源

2)使用高線性化、低雜訊的放大器或使用平衡與非平衡轉(zhuǎn)換器來(lái)驅(qū)動(dòng)類(lèi)比數(shù)位轉(zhuǎn)換器輸入

LMX2531或LMX2541之時(shí)脈合成器都因?yàn)槟墚a(chǎn)生低抖動(dòng)現(xiàn)象類(lèi)比數(shù)位轉(zhuǎn)換器的時(shí)脈訊號(hào)而被推薦使用,而LMH6554則能用來(lái)驅(qū)動(dòng)類(lèi)比數(shù)位轉(zhuǎn)換器的類(lèi)比輸入訊號(hào)。

LMX2531整合了PLL與VCO兩個(gè)元件,使能讓雜訊底部?jī)?yōu)於-160dBc/Hz.其晶片具備多種不同的版本可以符合從553百萬(wàn)赫茲到2790MHZ的頻帶范圍各種不同頻率的需求。

為了能達(dá)到更高輸入頻率的訊號(hào)雜訊比效能,因此LMX2541由於具有較低相位雜訊而成為合適的時(shí)脈源。LMX2541在頻率21億赫茲的狀況下會(huì)產(chǎn)生小於2微弧度(mrad)的均方根雜訊;以及在頻率35億赫茲的狀況下會(huì)產(chǎn)生3.5微弧度的均方根雜訊。LMX2541的PLL會(huì)產(chǎn)生-225dBc/Hz的標(biāo)準(zhǔn)化雜訊底部,且能在整數(shù)與分?jǐn)?shù)模式中以高達(dá)104MHZ的相位偵測(cè)率來(lái)運(yùn)作。

LMH6554為業(yè)界最高效能的差動(dòng)放大器。其低阻抗的差動(dòng)輸出特性可用來(lái)驅(qū)動(dòng)類(lèi)比數(shù)位轉(zhuǎn)換器的輸入訊號(hào)并在任何中間濾波過(guò)程中使用。這個(gè)具備寬頻的全功能差動(dòng)放大器可以驅(qū)動(dòng)8到16位元的高速類(lèi)比數(shù)位轉(zhuǎn)換器且在頻率800MHZ的狀況下得到0.1dB的增益值,在頻率250MHZ的狀況下得到72dBc的SFDR,以及擁有0.9nV/sqrtHz的低輸入電壓雜訊效能。

當(dāng)LMH6554將峰值對(duì)峰值2V的電壓驅(qū)動(dòng)進(jìn)入低到200歐姆的負(fù)載時(shí),便能以頻率75MHZ來(lái)線性傳遞16位元的訊號(hào)。經(jīng)由外部增益電阻器以及整合共模回饋,LMH6554也可以應(yīng)用於差動(dòng)與差動(dòng)訊號(hào)間或是單端與差動(dòng)訊號(hào)間。而放大器會(huì)提供高達(dá)18GHZ的大訊號(hào)頻寬、8dB的雜訊指數(shù)以及6,200V/us的擺動(dòng)速率。

圖5所示為一組使用上述所提到的支援元件的區(qū)塊示意圖。

圖5:典型的系統(tǒng)區(qū)塊示意圖。

結(jié)論

本文說(shuō)明關(guān)於設(shè)計(jì)時(shí)序交錯(cuò)式高速類(lèi)比數(shù)位轉(zhuǎn)換器時(shí)所面臨到的挑戰(zhàn)與幾種解決方案。現(xiàn)在由於交錯(cuò)方*的不斷演進(jìn)及低抖動(dòng)時(shí)脈源與高效能放大器的出現(xiàn),讓超越6GSPS速率時(shí)仍然維持絕佳的動(dòng)態(tài)效能得以實(shí)現(xiàn)。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論