從直流精度的角度看,高速放大器的發展過程一直就是在提高精度、提高壓擺率——這與大信號帶寬(LSBW)相關。電流反饋放大器(CFA)本身有極高的壓擺率,卻具有相對較差的DC精度。電壓反饋放大器(VFA)的壓擺率也已經通過許多方法得到了提高,此篇將會介紹這些方法。全差分放大器(FDA)有兩種選擇類型,其中基于CFA的類型具有非常高的壓擺率和較差的DC精度,而基于VFA的FDA利用類似的技術來提高精度,并與核心VFA一樣具有較高的壓擺率。FDA因為多了共模控制回路,帶來了一些新的DC精度考慮因素。本篇是這個系列的第三部分,將介紹幾種不同的VFA方法,第四部分將討論CFA和FDA的DC精度考慮因素。

提高VFA運算放大器壓擺率的途徑

可實現的DC精度(和噪聲)在很大程度上是輸入級設計問題。VFA有一些天然優勢來降低DC誤差。回想一下,VFA的第一級DC誤差是三個輸入誤差項,許多早期參考文獻都提到了如何利用它們來計算輸出誤差。

輸入失調電壓和漂移

輸入偏置電流和漂移

輸入失調電流和漂移

有時,一些其它誤差項和輸入失調電壓混淆在一起。物理輸入誤差電壓有Vout/Aol項,由于該項與輸出信號電平有關,因此可以通過輸出的增益誤差正確得到。由開環增益(Aol)引起的輸入誤差電壓沒有加到靜態DC輸入失調電壓上,而是由LG/(LG+1)所描述的增益壓縮項計算,其中LG=Aol/NG,NG=噪聲增益。那么,當VFA運算放大器在單位增益、分離平衡電源及接地非反相輸入條件下工作時,輸入失調電壓是多少?由于輸出電壓工作會非常接近于地,因此在輸入差分級內部,誤差電壓應該非常接近0V。觀察到的外部失調電壓是輸入級不對稱所需的補償電壓,使內部實際誤差電壓達到零。

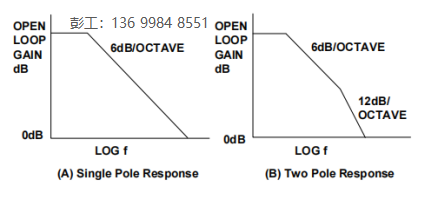

在20世紀80年代初,典型的VFA增益帶寬積(GBP)穩步增長,可是它們的壓擺率并沒有跟上增長步伐,比如一個典型的單位增益穩定高速Harris運算放大器具有的小信號帶寬(SSBW)遠超其LSBW。到大約2004年,有了兩種主要方法來增加VFA器件的LSBW:使用仿真CFA工作的輸入級或提供解補償放大器。非單位增益穩定、解補償VFA器件減小了補償電容值,通常增加了輸入級gm(輸入級中負反饋R較低,也使輸入噪聲較低)。因此,對于補償電容上大致的近似轉換電流值,可以得到更大的壓擺率。提高壓擺率的同時改善DC精度和噪聲,也是降低電源電流時要考慮的。在靜態電流更大的情況下,總是可能提高壓擺率并降低輸入電壓的噪聲。本文提供了在越來越低的靜態電流下改善這兩項指標的解決方案。

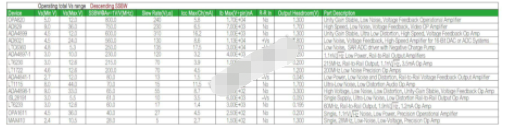

首先,讓我們回顧一下單位增益穩定、非壓擺增強型高速(》20MHz)VFA選擇。壓擺增強型單位增益穩定VFA可按LSBW/Icc值的降序排列出來。它們將出現在后面的表中,現在先討論中等壓擺率、低噪聲、精密、單位增益穩定的VFA。最近推出的許多VFA包含軌到軌輸出(RRO)和負軌輸入(NRI),或軌到軌輸入(RRI)。一些低噪聲器件是非RRIO設計。RRI器件利用交叉網絡(x-over network)或內部電荷泵,使輸入級偏置超出所應用的電源。為了在整個可用的輸入范圍內顯示更好的直流偏置器件,表1~表3中將不包含RRI器件。單位增益穩定VFA器件長期以來難以提供低輸入電壓噪聲,而最近的幾個版本似乎突破了這一桎梏——最初表現出較高的電源電流或低得多的壓擺率,但提供了改進方案(見表1)。還有許多低失調、更高速、單位增益穩定的CMOS或JFET輸入器件,它們通常顯示出更高(》4nV/√Hz)的輸入電壓噪聲,在LSBW/Icc比率時也不夠節能。其優點是可以消除輸出DC失調計算中的輸入偏置和失調電流誤差。

非壓擺增強型、單通道、單位增益穩定VFA器件

表1列出了具有代表性的非壓擺增強型、單通道、單位增益穩定VFA器件,它們同時提供低失調電壓(≤1mV最大值)和較低的輸入電壓噪聲(《4nV/√Hz)。后面的三個表格顯示了通過不同的方法來提高壓擺率。這些低噪聲和偏置器件都是雙極型的。因此,要想獲得低的輸出失調就需要在設計中使用偏置電流消除電路。如果能正確做到這些,就能減少由于Rf x Ios的輸入偏置電流引起的輸出DC誤差。再次注意,最高速器件需要非RRO設計。此處顯示的1SSBW增益通常超過真實的增益帶寬積(GBP)。例如,最快的800MHz OPA820實際上顯示了240MHz的數據手冊GBP。這又是由于LG單位增益交越處的相位裕度《65°,大大增加了閉環帶寬。

為了簡化單通道VFA表,下面的篩選條件將被遵循:

1. 壓擺率》400V/μs

2. 最大Vio》1mV

3. 輸入噪聲電壓》4nV/√Hz

4. 軌到軌輸入(RRI)器件(在表4中出現)

5. 1k MSRP(制造商建議零售價)》3.00美元

6. 過時的器件

表1:單位增益穩定、非壓擺增強型、單通道VFA器件,按SSBW降序排列。

要提供具有較高壓擺率的VFA解決方案,最常見的方法是解補償運算放大器。這種方法限制了VFA在高增益(或跨阻抗)中的應用,但在給定的電源電流范圍內可以提供非常好的DC精度,通常還有較低的輸入電壓噪聲和較高的LSBW。雖然也有許多JFET或CMOS輸入解補償選擇,但它們多數都具有較高的輸入噪聲或失調電壓。為顯示一些極低輸入偏置電流解補償選項,擴大了篩選條件:

1. 輸入電壓噪聲》3.0nV/√Hz

2. 最大輸入失調電壓》2.5mV

3. 價格》4.00美元

4. 過時的器件

使用解補償方法時壓擺率通常較高,同時大多數器件也顯示較低的輸入電壓噪聲和失調電壓。RRO或NRI器件相對較少,其中一個最新的器件(OPA838)還具有壓擺增強輸入級、極低功耗及低噪聲。一般來說,這種器件提供極低的輸入失調電流,允許使用輸入偏置電流消除技術。SSBW x Gmin降序排列遠超每個器件的實際GBP,因為最小工作閉環增益具有較低的相位裕度,擴大了最小建議閉環增益處的閉環帶寬。Gmin是建議的最小增益。通常設置為達到安全的最小相位裕量,在30°~45°之間。Gmin通常會使非反相SSBW達到峰值,但不會不穩定。因此,“最小穩定增益”有點用詞不當,“最小工作增益”更準確。使用簡單的補償技術,解補償VFA可在任何增益(包括衰減)下進行反相操作。

表2:解補償高速、單通道VFA器件,按Gmin x *SSBW(@Gmin)降序排列。

壓擺增強型、單位增益穩定電壓反饋放大器

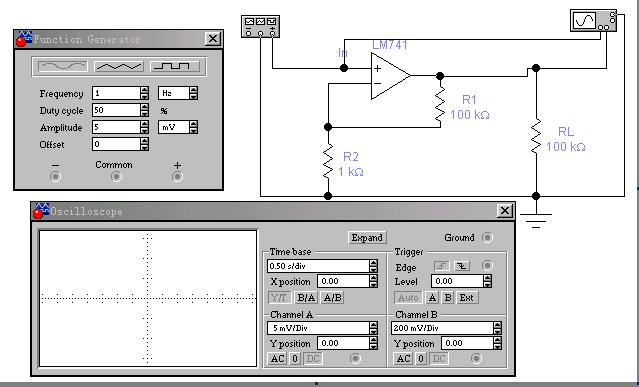

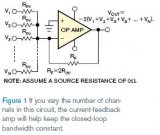

要縮小單位增益穩定VFA運放SSBW和LSBW的差距,最早的方法是在跨導元件上使用一個匹配的輸入緩沖級。這顯示了VFA的一個外部反饋特性,但隨后仿真了CFA壓擺率,因為誤差電壓的增加會導致輸入緩沖器之間電阻器中的轉換電流增加。圖1示出了一個早期的例子,圖中標出了輸入級和跨導元件。壓擺限制開始時,輸入誤差電壓增加,從而增加了通過電流鏡到補償電容(圖1中的“C”)的充電電流。

圖1:VFA輸入級仿真CFA壓擺增強。

這種方法通常可由其所帶的相對較高的輸入電壓噪聲來識別。而且,由于輸入緩沖器不是那么匹配,輸入失調電壓和電流通常要高些。沒有失調電流漂移信息也是識別該拓撲結構的一個線索。類似于CFA放大器(使用類似的輸入緩沖器),這種壓擺增強方法通常帶來較差的DC精度和非RRIO擺動性能。有些情況下很難識別這種拓撲結構(盡管LTC在其數據手冊中為這種類型提供了圖1)。表3盡可能地列出了與圖1的設計類似的一系列單通道、單位增益穩定、極高壓擺率的器件。盡管這些器件中有許多具有較高的輸入噪聲和失調電壓,表3還是去掉了極值,包括排除在外的器件(沒對輸入失調電壓進行篩選)。

1. En》12nV/√Hz

2. 1K MSRP》3.00美元

3. 非單位增益穩定的器件

4. 過時的器件

表3:單位增益穩定、極高壓擺率、單通道VFA,以Gmin=1SSBW降序排列。

雖然這些器件基本上仿真了CFA類型的LSBW性能,但DC精度和噪聲仍有很大的提升空間。此外,和所有CFA解決方案類似,它們都不支持輸入端擺動到軌。

按需提供壓擺率實現更好的失調和噪聲性能

從大約2004年開始,高速VFA的開發找到了新的方法來按需提供壓擺率,實現更好的失調和噪聲性能。他們的目標是改善DC精度和噪聲,同時在I/O引腳上實現擺動到軌的組合技術。目前尚不清楚其內部有多相似,但是在設計師的工具套件中填補這一空白已經取得了很大進展。而且,這些器件首先可以通過LSBW/Icc數值降序排列并尋找擺動到I/O軌的某種組合來識別(刪掉表3中的器件)。表4中使用的簡單數值是基于壓擺率的2Vpp輸出LSBW除以25C最大靜態電源電流。但請記住,在測試頻率增加并且壓擺增強電路工作時,對壓擺增強型運算放大器的各種LSBW測試都會顯示出電源電流的快速增加。所有CFA以及此處描述的壓擺增強型VFA器件都是如此。但是在任何壓擺增強器件的數據手冊中都難以找到這個指標。

早期提高極低功率器件壓擺率的方法卻導致了極高的噪聲和失調電壓。最新的方法在減少電源電流的情況下同時降低了輸入噪聲和失調電壓。這里我們看到更多的RRO選擇,主要是NRI。雖然表4中未顯示,但這些“精密”VFA器件的輸入失調電流和漂移通常都非常低。

有一些RRI選擇,當輸入共模處于輸入切換到上級的操作范圍時,壓擺增強是否起作用還不清楚。LTC的RRI器件在反相配置中指定了壓擺率,以保持輸入工作電壓固定在中間值附近。ADI的RRI器件壓擺率規范要求+1的工作增益,但不會進入正電源以下1.3V的交叉區域。

為簡化表4,濾除了以下內容:

1. En》6nV/√Hz

2. Vio》0.5mV

3. 1k建議零售價》3.00美元

4. 過時的器件

表4:精密、壓擺增強型、單位增益穩定單通道VFA,按LSBW/Icc降序排列。

更高速的VFA一直在努力改善其全功率帶寬,加入了與眾多《20MHz精密運算放大器類似的I/O范圍和DC精度特性。如果不需要RRIO,并且只需要適度的壓擺率,表1中列出了一些非常節能的低噪聲和低失調選擇。如果您的應用可以從解補償解決方案中受益,則會得到更高的壓擺率和電源電流。表2的幾個最新器件在非常低的靜態電流下具有極低的噪聲和失調。當VFA架構中需要CFA類型的壓擺率時,這很容易得到,但都不會提供擺動到軌的能力。如表3所示,它們也同CFA一樣具有較差的DC精度,和通常較高的輸入電壓噪聲。表4中的最新產品改善了壓擺率與靜態功率,同時提供RRO和不同的擺動到軌輸入選擇。雖然它們的輸入噪聲通常不如表1中那么好,壓擺率也遠遠比不上表3中的器件,卻可以在較低的靜態電流下擴展LSBW選擇,并且有一些吸引人的選擇。第四篇我們將繼續討論高速CFA和FDA的DC精度。

責任編輯:gt

電子發燒友App

電子發燒友App

評論