二進制解碼器是由單獨的邏輯門構成的另一種組合邏輯電路,與編碼器完全相反。

名稱“解碼器”是指將編碼信息從一種格式轉換或解碼為另一種格式,因此二進制解碼器使用2 n個輸出將“ n”個二進制輸入信號轉換為等效代碼。

二進制解碼器是另一種類型的數字邏輯設備,根據數據輸入線的數量,其輸入的2位,3位或4位代碼,因此具有一組2位或更多位的解碼器將定義為具有n位代碼,因此將有可能表示2 n個可能的值。因此,解碼器通常通過將其n個輸出中的一個準確地設置為邏輯“ 1”來將二進制值解碼為非二進制值。

如果二元解碼器接收?輸入(通常歸類為一個二進制或布爾數)它激活一個且只有其中的一個2個?基于與所有其它輸出該輸入輸出停用。

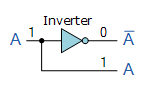

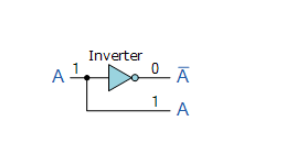

因此,例如,一個逆變器( 非門 )可以被歸類為一個1至2個二進制解碼器1-輸入和2-輸出(2 1)是可能的,因為與輸入阿它可以產生兩個輸出甲和甲(不是-A),如圖所示。

那么我們可以說標準的組合邏輯解碼器是n-m解碼器,其中m≤2 n,其輸出Q僅取決于其當前輸入狀態。換句話說,二進制解碼器查看其當前輸入,確定在其輸入處存在哪個二進制代碼或二進制數,并選擇與該二進制輸入相對應的適當輸出。

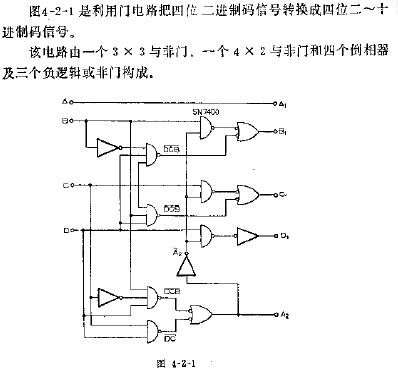

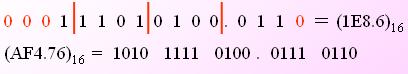

甲二元解碼器將編碼的輸入成編碼輸出,其中輸入和輸出代碼是不同的和解碼器可用于“解碼”二進制或BCD(8421碼)輸入圖案以通常為十進制輸出代碼。常用的BCD到十進制解碼器包括TTL 7442或CMOS4028。通常,解碼器的輸出代碼通常比其輸入代碼具有更多的位,并且實際的“二進制解碼器”電路包括2到4、3到8和4至16線配置。

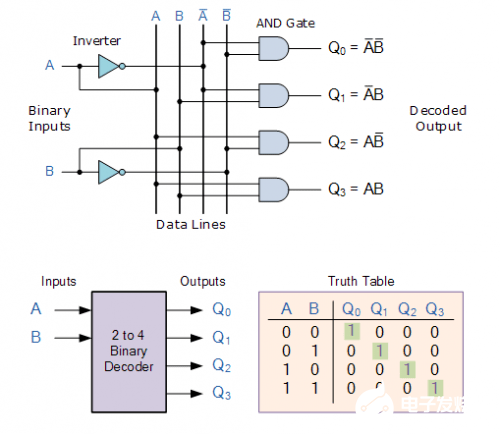

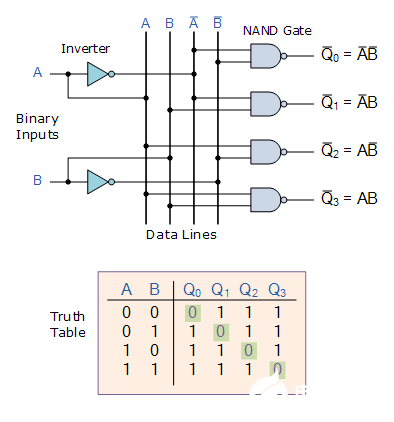

2至4行解碼器及其真值表的示例如下:

2對4二進制解碼器

上面的2到4行二進制解碼器的簡單示例由四個“ 與”門的陣列組成。標記為A和B的2個二進制輸入被解碼為4個輸出之一,因此對2到4二進制解碼器進行了描述。每個輸出代表2個輸入變量的最小項之一(每個輸出=一個最小項)。

二進制輸入A和B確定從Q0到Q3的哪條輸出線在邏輯電平“ 1”下為“高”,而其余輸出在邏輯“ 0”下保持為“低”,因此在任何情況下只有一個輸出有效(高)一度。因此,無論哪條輸出線為“ HIGH”,都標識輸入處存在的二進制代碼,換言之,它“解碼”二進制輸入。

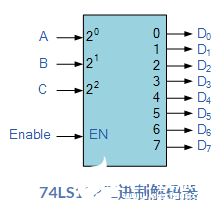

一些二進制解碼器還有一個附加的輸入引腳,標為“ Enable”,用于控制設備的輸出。此額外的輸入允許解碼器的輸出根據需要設置為“ ON”或“ OFF”。這些類型的二進制解碼器通常在微處理器存儲應用中用作“內存地址解碼器”。

我們可以說二進制解碼器是具有用于啟動解碼器的附加數據線的多路分解器。查看解碼器電路的另一種方法是將輸入A,B和C視為地址信號。A,B或C的每個組合定義一個唯一的內存地址。

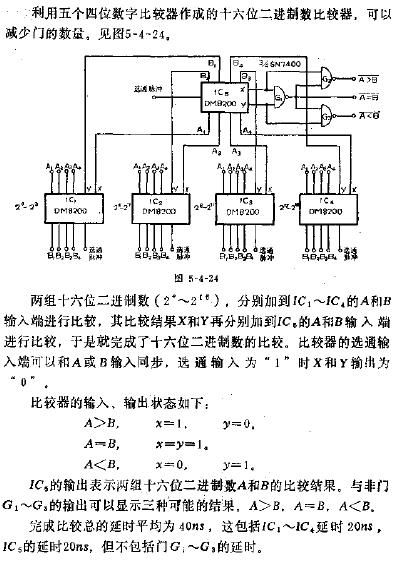

我們已經看到2到4行二進制解碼器(TTL 74155)可用于解碼任何2位二進制代碼以提供四個輸出,每個可能的輸入組合一個。然而,有時需要二進制輸出數量大于可用數量的二進制解碼器,因此通過添加更多輸入,解碼器可能會提供2 n更多的輸出。

因此,例如,具有3個二進制輸入(n = 3 )的解碼器 將產生3到8行解碼器(TTL 74138),而4個輸入( n = 4 )將產生4到16行解碼器(TTL) 74154)等。但是,解碼器也可以具有少于2 n的輸出,例如BCD到七段解碼器(TTL 7447),該解碼器具有4個輸入和只有7個活動輸出來驅動顯示器,而不是像您那樣將其輸出為16(2 4)個輸出期望。

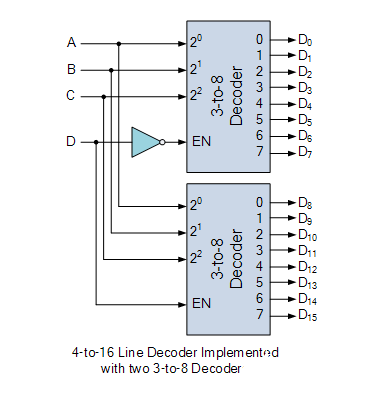

在這里,已經使用兩個較小的3至8解碼器實現了更大的4(3數據加1使能)至16行二進制解碼器。

4到16二進制解碼器配置

輸入A,B,C用于選擇任一解碼器上的哪個輸出為邏輯“ 1”(高),輸入D與啟用輸入一起使用,以選擇第一個或第二個編碼器將輸出“ 1”。

但是,可用于一個特定解碼器的輸入數量是有限制的,因為隨著n的增加,產生輸出所需的AND門的數量也會變大,從而導致用于驅動的門扇出他們越來越大。

此類有源“ HIGH”解碼器可僅使用反相器( 非門 )和與門實現。使用“ 與”門作為輸出的基本解碼元素非常方便,因為僅當其所有輸入均為邏輯“ 1”時,它才會產生“高”或邏輯“ 1”輸出。

但是有些二進制解碼器是使用“ 與非”門代替“ 與”門構建其解碼輸出的,因為與“與”門相比,“與非”門的生產成本更低,因為它們需要更少的晶體管來實現其設計。

使用“ 與非”門作為解碼元件,將導致有效的“ LOW”輸出,而其余的將為“ HIGH”。當“ 與非”門產生具有反相輸出的“ 與”運算時,“ 與非”解碼器的反相真值表看起來像這樣。

2至4行NAND二進制解碼器

然后,對于NAND解碼器,在任何給定時間只有一個輸出為LOW且等于邏輯“ 0”,而所有其他輸出為邏輯“ 1”時為HIGH。

解碼器還可提供一個附加的“使能”輸入引腳,該輸入引腳可通過分別對它們施加邏輯“ 1”或邏輯“ 0”來使解碼輸出變為“ ON”或“ OFF”。因此,例如,當使能輸入為邏輯電平“ 0”(EN = 0)時,無論輸入A和B的狀態如何,所有輸出均為邏輯“ 0”的“ OFF”(對于AND門)。

一般來實現這個功能使得能夠在2輸入AND或NAND柵極與3-輸入替換AND或NAND門。附加輸入引腳代表使能功能。

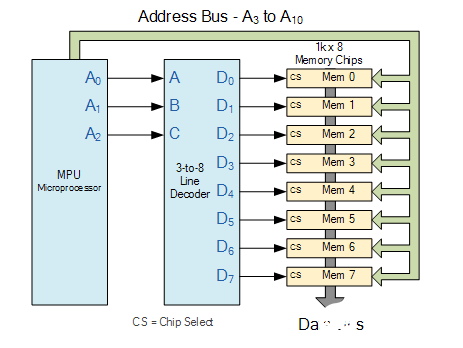

內存地址解碼器

二進制解碼器最常用于更復雜的數字系統中,以基于計算設備產生的“地址”訪問特定的存儲位置。在現代微處理器系統中,所需的內存量可能會很高,并且通常不止一個內存芯片。

克服此問題的一種方法是將許多獨立的存儲芯片連接在一起,并在公共“數據總線”上讀取數據。為了防止同時從每個存儲芯片“讀取”數據,每個存儲芯片一次要一個一個地選擇,此過程稱為地址解碼。

在這種類型的應用中,地址代表編碼數據輸入,而輸出則是特定的存儲元件選擇信號。每個存儲芯片都有一個稱為“ 芯片選擇”或CS的輸入,MPU(微處理器單元)使用它來在需要時選擇合適的存儲芯片。通常,片選(CS)輸入上的邏輯“ 1” 選擇存儲設備,而輸入上的邏輯“ 0”取消選擇存儲設備。

因此,通過一次選擇或取消選擇每個芯片,可以使我們為特定的地址位置選擇正確的存儲器地址設備。地址解碼的優勢在于,當我們指定特定的存儲器地址時,相應的存儲器位置僅存在于其中一個芯片中。

例如,讓我們假設我們有一個非常簡單的微處理器系統,僅具有1Kb(一千個字節)的RAM存儲器和10條可用的存儲器地址線。該存儲器由128×8位(128×8 = 1024字節)設備組成,對于1Kb,我們將需要8個單獨的存儲芯片,但是為了選擇正確的存儲芯片,我們還需要3至8行二進制解碼器如下所示。

內存地址解碼

二進制解碼器僅需要3條地址線(A 0至A 2)來選擇8個芯片中的每個芯片(地址的下部),而其余8條地址線(A 3至A 10)則選擇正確的存儲器該芯片上的位置(地址的上部)。

使用地址總線選擇存儲位置后,特定內部存儲位置上的信息將發送到公共“數據總線”以供微處理器使用。這當然是一個簡單的示例,但是對于所有類型的存儲芯片或模塊,其原理均相同。

二進制解碼器是將一種數字格式轉換為另一種數字格式的非常有用的設備,例如將二進制或BCD類型的數據轉換為十進制或八進制等,常用的解碼器IC是TTL 74LS138 3至8行二進制解碼器或74ALS154 4至16線解碼器。

電子發燒友App

電子發燒友App

評論