采樣保持(S/H)功能是數據采集和模數轉換過程的基礎。S/H放大器電路有兩種不同的基本工作狀態。在第一種狀態下,對輸入信號采樣,同時傳送到輸出端(采樣)。在第二種狀態下,保持最后一個采樣值(保持),直到再次對輸入采樣。在大多數應用中,S/H用作數據采集系統中模數轉換器的“前端”。這樣使用時,S/H主要用于在執行模數轉換所需的時間段內,讓模擬輸入電壓電平保持恒定不變。

具體來說,S/H是數據轉換系統必須具備的系統功能模塊,所用的模數轉換器在進行轉換期間,必須提供恒定且準確的模擬輸入。逐次逼近類型模數轉換器就是這種用法的一個示例。理想情況下,S/H會在接到HOLD命令之前“凍結”最后的瞬時輸入電壓,并將該電壓原樣提供給模數轉換器,隨后由模數轉換器將該電壓轉換成相應的數字字。實際上,在實施S/H的過程中會涉及許多誤差因素。所以,本應用筆記將探討這些基本考量因素,以及具有代表性的器件拓撲和應用。

S/H放大器的基本操作

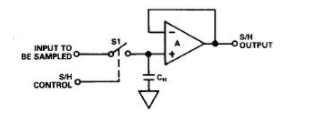

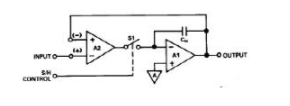

圖1顯示了S/H的一些基本信息,圖1a是基本的S/H電路結構。圖中顯示,待數字化的模擬輸入信號直接傳輸至電子開關S1。根據S1的狀態,該信號將傳輸至保持電容CH,或者被攔截。開關S1的狀態由S/H控制線控制,該控制線是一個數字輸入。

當S1關閉時,傳輸至CH的輸入信號由A1緩存。該信號也可能傳輸至S/H輸出端(本次討論不考慮低通濾波器可能造成的影響)。如果在輸入變化(與交流波形一樣)期間,S1保持連接一段時間,則該操作也可稱為跟蹤;也就是說,任何輸入變化都會傳輸至輸出。

a. 基本的S/H電路,由開關、保持電容和緩沖放大器組成

b. S/H波形,顯示被采樣的輸入(頂部)、S/H控制(中間)和S/H輸出(底部)

圖1.S/H基本信息

當S1打開時,最后的輸入電壓值作為電荷保留在CH上;也就是保持電壓不變。A1繼續讀取該電壓,直到進入下一個采樣周期。圖1b通過輸入、輸出和控制波形展示了此操作。S/H電路用于實現各種信號處理功能;不僅可用于實現模數接口,還可用于實現更通用的模擬存儲器功能,例如自穩零型放大器。

圖1b中所示的S/H工作波形幾乎是理想波形,假設開關、跟蹤、保持特性和負載/源抗擾性均是理想狀態。但實際上,在該器件的各個狀態(四個狀態)下,都存在S/H誤差。這些狀態包括:

(1) 保持采樣轉換

(2) 采樣間隔

(3) 采樣保持轉換

(4) 保持間隔

采樣/跟蹤保持放大器

很明顯,這些誤差對很多應用可能非常重要,對于高精度應用(》10位,或精度為0.1%或更低)則全部都很重要。具體的定義和說明如下文所述。

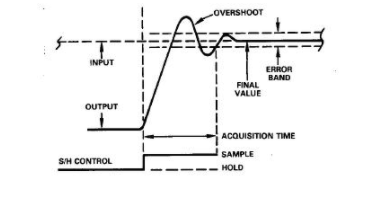

保持采樣轉換誤差

當器件從保持狀態切換至采樣狀態時,這些誤差與時間間隔相關。由于自最后一次采樣電壓之后,輸入可能發生了很大變化(例如,可能是滿量程),因此S/H必須重新獲取輸入信號,并再次在其額定精度范圍內穩定下來。如圖2所示。

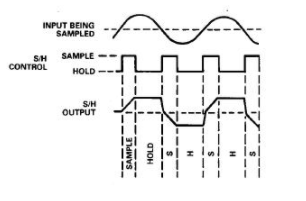

采集時間是S/H在收到采樣命令后采集并跟蹤輸入信號所需的時間。通常指定為滿量程電平變化(-10V至+ 10V,反之亦然),因為這代表了獲取任意電平信號所需時間的最壞情況。輸出必須假設所需的電平在額定誤差范圍內,與轉換或采樣所需的精度水平一致。例如,可能是0.01%或0.1%。圖2a所示為保持采樣采集波形。

圖2a.保持采樣節點采集時間,顯示新信號采集(頂部)和S/H控制(底部)

對于大幅度的保持采樣變化,采集時間的大部分都是初始擺動間隔。在這個高誤差間隔之后,輸出可能過沖,隨之將穩定在±2mV額定精度范圍內;以20V刻度為例,該范圍為±0.01%。注意,當信號穩定并保持在額定誤差范圍內時,采集時間結束。

采集時間是保持采樣誤差的主要組成部分,也是決定轉換系統S/H部分工作速度的主要因素。典型時間為約幾毫秒至0.1%或0.01%或更高的精度。采集時間很大程度上取決于所用的保持電容的值,因為該電容(通常)會影響壓擺率。

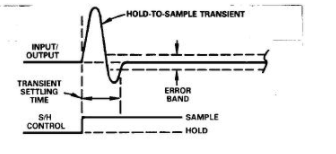

圖2b所示為保持采樣瞬態,即從保持模式轉換至采樣模式時產生的切換瞬態。注意,即使之前的保持電壓和新樣本之間相差不大,也會出現這種瞬變。由于這種瞬變幅度可能遠遠超過S/H額定精度(可能多達幾百毫伏),在確定輸出電壓樣本有效之前,必須留出足夠的時間讓這種瞬變消失。

圖2b.保持采樣模式瞬態和建立時間

由于該瞬態的建立時間會延續到保持采樣命令開始之后,系統時序必須允許此種情況。但是,實際上,與保持采樣瞬態相關的建立時間通常都遠遠短于采集時間。因此,相當于最壞情況(或采集時間)的時間間隔通常都會自動考慮保持采樣瞬態誤差及其相關的建立時間。

采樣誤差

在采樣間隔內,S/H器件會像運算放大器一樣跟蹤輸入信號。事實上,大部分S/H器件要么是專用運算放大器,要么是使用運算放大器(其特性非常適合S/H使用)構建。因此,由于大部分S/H放大器都會降低至或等同于運算放大器電壓跟隨器或反相器,所以可以采用類似方法來計算它們的采樣模式誤差。

S/H中的純比例誤差通常可以被視為良性誤差,因為它們大體上可以通過校準調整來消除。通常情況下,要執行此操作,模數基準源是一個非常方便的點,這樣可以一次性消除所有系統比例誤差。當然,這種方法適合傳統用法,例如一個模數轉換器一個S/H。如果模數轉換器之前有多個S/H,或者如果S/H只是其他電路的一部分,則需要通過增益比例電阻來調節局部增益。

在任何情況下,都必須了解最壞情況與理想S/H比例系數之間的偏差,并在計算誤差預算時考慮這種偏差。通常情況下,比例系數都為1 ±0.001%或更低的誤差。也就是與電壓跟隨器連接相關的增益誤差類型。

在使用增益電阻的情況下,例如當S/H用于同相增益而不是單位增益時,電阻公差會使這個誤差明顯增大。對于反相模式操作S/H,無論如何,都必須使用增益比例電阻。無論在哪種情況下,在S/H芯片上安裝應用電阻都是非常有利的,因為它們將獲得更高的預調精度,以及最大偏移的技術規格。對于器件,近來的趨勢是采用預調電阻來支持常用的增益-1、+2等。

注意,雖然可以通過系統比例校準來調節實際增益(比例)誤差,但增益非線性并不等同于非可調誤差。

增益非線性是一個臨界S/H誤差,它表現為與理想傳輸特性之間的偏差。此誤差分量是器件在其額定信號輸出范圍(通常為±10V)內運行時,與理想S/H增益數值(例如+1、+2、-1、 -2等)之間的動態偏差。其最大誤差分量通常是輸入級共模誤差,這是跟隨器類型連接中的典型情況(總體上最普遍)。在反相器類型連接中,共模誤差消失,但電阻匹配誤差會成為誤差源。

在±10V信號范圍內,S/H非線性典型值為0.001%至0.01%。顯然,為了保持系統性能,S/H非線性必須優于使用的模數轉換器所確立的整體非線性。對于S/H非線性,可以遵循一個很好的法則:數值應比轉換器的基本分辨率高一個數量級。例如,0.01%或更好的S/H非線性度與10位轉換器配合使用。注意,用戶可能需要根據S/H的共模抑制比(CMRR)計算非線性,例如80dB CMRR相當于0.01%的非線性。

偏移是指S/H輸入接地時輸入和輸出之間的直流偏移。通常通過可選的微調電位計將其調節至零。典型的直流偏置規格為±2mV或以下。對于S/H應用,自身的純偏移不是問題,因為在系統整體校準過程中,始終可以將其調節至零。也可以進行模數轉換器微調校準時,以手動方式或通過軟件完成。

失調溫度漂移則是另一回事,因為很難將其與實際信號區分開來。除非包含自穩零校準周期,否則S/H失調漂移誤差分量無法降低,會隨著溫度變化產生誤差。S/H漂移的典型值為1至10μV/°C,無論是要求更高的精度,還是需要廣泛的溫度范圍,此誤差都屬于嚴重誤差。

S/H失調電壓也會隨電源電壓而變化,這一點也應該說明。通常,電源抑制約為80dB或100μV/V。對于調節良好的電源或使用自動校準周期時,此參數通常不太重要。

建立時間適用于輸入電壓快速變化的采樣模式。跟蹤輸入信號時,S/H受到動態限制,這與其他運算放大器配置類似。

建立時間由壓擺率和小信號帶寬決定,如果步長大幅變化,壓擺率是主因。典型壓擺率為5至10V/μs,建立時間為5-10μs。正如采集時間部分所述,確切規格很大程度上取決于保持電容。

采樣保持轉換誤差

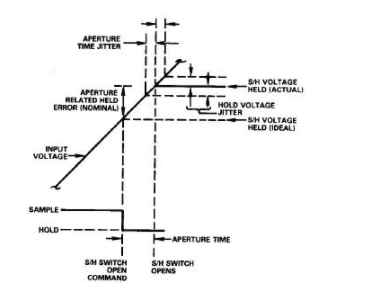

孔徑時間或孔徑延遲是指發出保持命令到實際打開S/H開關經過的時間。對于快速變化的輸入電壓,在確定實際保持電壓的過程中會產生誤差。由此產生的電壓誤差將等于有效孔徑時間間隔內輸入電壓的變化。

圖3大體顯示了與孔徑時間相關的誤差,圖3a顯示孔徑延遲如何在保持電壓內產生誤差。對于快速變化的輸入電壓,在開關從開啟到關閉期間,S/H電壓以接近1/2LSB的幅度變化。

圖3a.與孔徑相關的時間/電壓誤差。模擬輸入/輸出(頂部),采樣/保持驅動(底部)。

作為孔徑時間影響的一般示例,考慮變化速率(信號斜率)為1 V/μs,以10ns孔徑時間采樣的輸入信號。由于與孔徑時間相關的dV/dt誤差,這會產生10mV采樣誤差。

這種誤差通常很嚴重。有效孔徑延遲可以通過按照標稱孔徑延遲時長提前在系統中執行保持命令來補償,但這并非全部誤差。

去除標稱孔徑延遲之后,剩余的誤差稱為孔徑抖動(或不確定性),它具有高信號斜率輸入,是真正限制S/H采樣誤差的因素。孔徑抖動是指樣本與樣本之間的實際S/H開關時序的凈變化量。這種抖動對孔徑時間相關誤差產生最終限制。對于1v /μs壓擺率示例,1ns孔徑抖動會導致±1mV電壓不確定性。

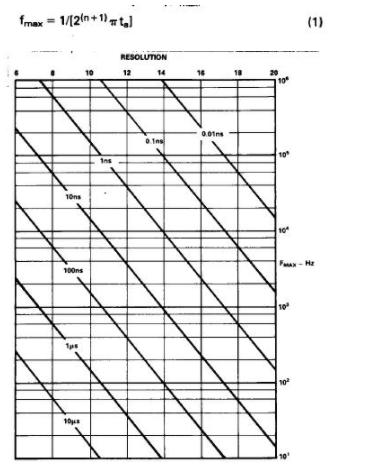

可以通過圖形顯示極限孔徑時間和由此產生的允許滿量程電平正弦波輸入頻率之間的一般關系。如圖3b所示。此圖基于最大(滿量程)正弦波輸入頻率,其誤差不超過1/2LSB。此頻率fmax的計算公式如下:

圖3b.各種孔徑時間和分辨率下的最大滿量程輸入正弦波頻率(fmax)

其中π = 3.14,ta為限制孔徑時間,“n”為轉換器的分辨率(單位:位)。

由于這些數據是針對限制孔徑,所以可用于帶有S/H的模數轉換器,或者是單獨的模數轉換器操作。在后一種情況下,模數轉換時間將定義有效孔徑時間。

該數據清楚表明了在最大化允許輸入頻率時所采用的S/H的值。不帶S/H的10μs 8位模數轉換器支持的最大輸出頻率約為60Hz。另一方面,在使用孔徑時間僅為100ns的S/H時,相同的模數轉換器支持6kHz最大頻率。注意,還存在一種更一般的關系;當轉換分辨率增加時,fmax在給定的轉換時間內降低。所以,當分辨率或頻率增加時,對S/H的需求變得更加關鍵。

顯然,S/H內的孔徑時間越短越好,因為這樣對配合使用的模數轉換器造成的限制就越少。描述中引用的時間對中速IC來說非常典型。S/H電路不是限制系統時序的最終因素,因為最大吞吐頻率通常出現在孔徑時間限制頻率之前。

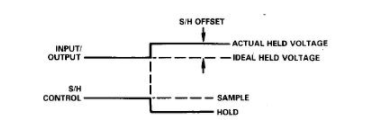

S/H偏移(也稱為S/H“基座”、“跳變”或“步進”)是S/H進行采樣保持轉換時,瞬變電荷導致的模擬誤差。它是由所用S/H開關的有限電容造成的,在較小程度上是由布局和/或封裝電容造成的。這些電容通過數字控制信號的一部分直接饋送到保持電容。一般來說,由于寄生耦合電容在給定的器件和布局中是固定的,所以可以通過使用較大的保持電容來降低這種誤差。圖4顯示了這種影響。

圖4.采樣保持偏移(頂部),S/H控制(底部)

此誤差可能為幾mV,在有些情況下,可以利用小型外部耦合電容將反相控制信號饋送至保持電容來進行補償。一般來說,可以通過將數字控制信號的峰峰電平降至絕對最小值,以及通過屏蔽/保護此信號和CH節點之間的耦合路徑來減小這種誤差。

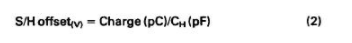

注意,采樣保持偏移并非始終這樣來直接指定,特別是在使用外部保持電容的IC器件中。在這種情況下,會給出電荷的技術規格,以pC為單位。在這些情況下,可以使用以下公式計算S/H偏移:

例如,使用1000pF CH進行10pC電荷傳輸將導致10mV S/H偏移。很顯然,傳輸的電荷越小,此誤差也越小。在更好的器件內,電荷傳輸可能低至1 pC或更低。

與純直流偏移一樣,S/H偏移最初也被視為可調節誤差。但是,如果它隨時間、輸入電壓和/或溫度改變,那么也必須考慮這些不穩定性。對于一些使用浮動開關(參見圖7b,類型2)的S/H器件,S/H偏移會隨輸入信號值變化。這顯然不可取,因為如果無法補償,則難以實現。S/H類型3(圖7c)沒有這個問題,因為其開關始終保持恒定電平(虛地)。

采樣保持建立時間是指S/H輸出收到保持命令后,在額定精度范圍內穩定下來所需的時間。其中包括開關轉換消隱的時間。

保持間隔誤差

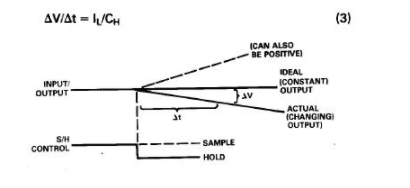

壓降也叫傾斜,是指保持時間間隔(?6?2t)內保持電壓(?6?2V)的變化,由流入(或流出)保持電容的凈漏電流導致。由于導致壓降的電流可能是一個S/H至下一個S/H的符號,所以下降電流會導致電容上的電壓升高或降低,如圖5所示。但是,重要的是保持間隔內的誤差幅度,而不是該符號。壓降由簡單的電荷/電壓關系決定:

圖5.壓降誤差(頂部),S/H控制(底部)注意,“壓降”可以為正,也可為負。

其中,IL為漏電流,CH為保持電容的值。舉例來說,對于100pF CH,電流降低1nA會導致10μV/μs壓降。在10μs保持期間,這會產生最大100μV壓降誤差,此誤差不是問題。

在給定的S/H器件中,電流IL按技術規格設定,CH則(通常)由用戶控制。所以,壓降可通過CH調節,會隨著CH增加而減小。

但是,這也需要權衡取舍。當CH增加以降低壓降時,一般會使采集時間延長。這是因為對CH充電以實現采集擺動所需的電流是固定的。所以,通常需要盡可能將漏電流IL保持在最低水平,以使壓降最低。一般來說,此參數由S/H輸出放大器的輸入偏置電流和開關漏電流決定,通常隨溫度升高而升高。在高溫下壓降最大。注意,用于計算壓降的IL值應考慮到溫度與凈漏電流之間的關系。使用FET輸入緩沖器時,溫度每上升10°C,偏置電流翻倍。

實際上,中等溫度下S/H中電壓的典型下降率接近1μV/μs,算的上很小的誤差。在計算最高溫度下的最大偏置電流時,這種情況可能并非一直保持不變。可以計算最高預期溫度下的漏電流,以確定最差的電壓下降率。

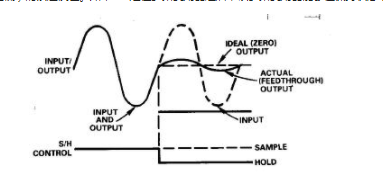

饋通是在保持(關閉)狀態下,通過S/H開關的交流信號泄漏導致的模擬誤差。與S/H偏移一樣,它基本上由開關電容引起,但也會受到布局相關電容耦合的影響。由于開關電容和保持電容可以構成分壓器,饋通會隨保持電容增大而降低,就像壓降和S/H偏移一樣。饋通的影響如圖6所示。

饋通一般由高頻率下(例如10kHz)的滿量程峰峰正弦輸入指定。在良好的S/H中,它一般達到80dB(或更高)。這相當于0.01%(或更低)的饋通誤差。如果S/H是在多路復用器之后,該多路復用器能夠在保持狀態下選擇高電平,且可能因信號饋通導致誤差,那么此參數非常重要。

圖6.饋通誤差電壓(頂部),S/H控制(底部)

電介質吸收

對于一些常見的電容類型,電介質不會在充電/放電周期后完全釋放所有電能。這種現象導致的結果是:在保持模式持續一段時間后,存儲電壓出現誤差。可以使用某些電介質,尤其是薄膜來最大限度降低這種影響。應使用指定的低DA電介質,例如聚四氟乙烯、聚苯乙烯和聚丙烯。注意,在使用外部CH,或者是使用外部CH來增強內部CH的S/H中,都需要考慮DA。

漂移和噪聲

與采樣模式下的S/H相比,保持模式下的S/H具有不同的漂移特性。在保持模式下,輸出端只有輸出緩沖放大器的漂移。在采樣模式下,可能只有輸出放大器的漂移,也可能是兩個放大器串聯產生漂移。

通常,保持模式下和采樣模式下的漂移特性不同沒有什么危害。轉換通常在幾微秒內完成,此時由溫度變化導致的漂移誤差尚不是問題。當保持時間異乎尋常的長時,則需考慮這種誤差。

噪聲則是另一種情況。例如,處于保持模式時,可以考慮圖7中的S/H類型2和3。如果輸出放大器的噪聲過大,則會在保持期間顯示,并隨所需信號一起數字化。如果此噪聲很高,且轉換器的線性度并不低于1/2LSB,則某些代碼會因噪聲調制而出錯。

MOSFET輸入緩沖器輸入電流極低,因而會用于一些S/H中。遺憾的是,這些緩沖器類型通常具有相對較高的輸入電壓噪聲,這會限制某些應用的整體精度。JFET的輸入電流不會像MOSFET那么低,但其噪聲電壓明顯更低。

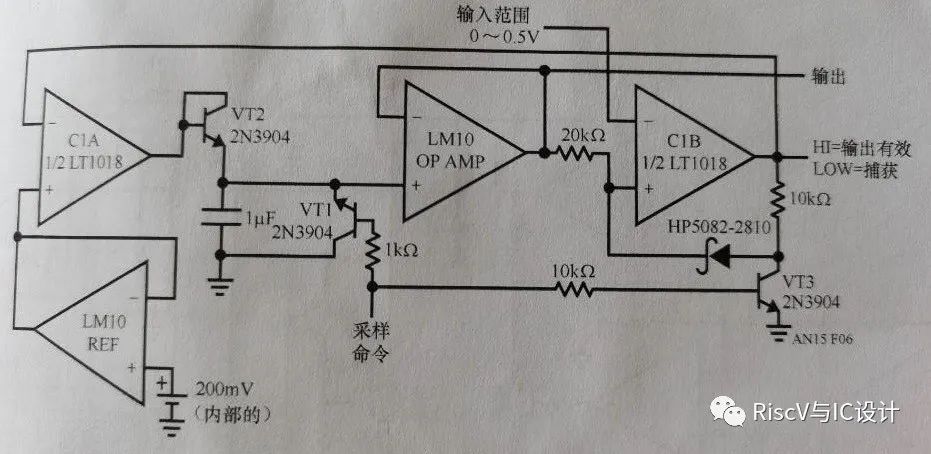

S/H設計類型

如今有大量S/H設備可用。除了非常高的性能限制外,大部分都采用幾大類設計拓撲。以下部分介紹這些設計拓撲,并針對每種拓撲展開簡單討論。了解不同的電路類型有助于針對給定應用選擇合適的S/H。

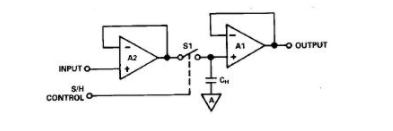

與圖1a中的基本電路一樣,圖7a中的電路也是實際S/H放大器類型。其中,A1、CH和開關的運行方式與之前所述的一樣,但還添加了輸入級緩沖器A2。

圖7a.開環,級聯跟隨器S/H(類型1)

增加緩沖器可以提高CH的充電電流。這樣可在不加載信號源的情況下,提供更快的采集速度。在這種S/H類型中,兩個放大器都必須具有高壓擺率、快速建立時間、低失調電壓和低漂移才能獲得最佳精度,因為這些誤差會累加。A1應該是一個FET輸入器件,以最大限度減少CH負載,但對于A2卻并非如此。這種S/H類型往往適用于高速采集。

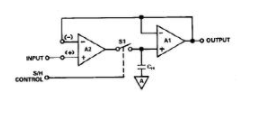

圖7b所示S/H配置的優點是,在采樣模式下,兩個放大器周圍都返回了一個整體反饋環路。所以,在采樣狀態下,A1的誤差達到最小,雖然它們還是會在保持狀態中顯示。此電路的精度可能更高,但是因為多級環路動態結構,其整體建立特性可能有所降低。

圖7b.閉環,跟隨器輸出S/H(類型2)

注意,在這種類型的S/H連接中,可以將輸入級接線,這樣(+)和(-)輸入端都可以連接外部選項,不過并非所有類型都能這樣做。憑借這種靈活性,S/H可以連接為(整體)反相或同相類型的S/H。應用電阻可能可用,也可能不可用。

圖7c中的第三個電路也在兩個運算放大器周圍連接反饋環路,在這一點上,它具有與7b類似的優勢。在這種情況下,開關在A1的虛地輸入端工作,CH則是輸出放大器級周圍的積分電容。

圖7c.閉環,積分輸出S/H(類型3)

注意,在這種類型的S/H連接中,輸入級的(+)和(-)輸入端也可按之前所述的方法使用。所以,這種類型可以連接為(整體)反相或同相類型的S/H。

S/H應用

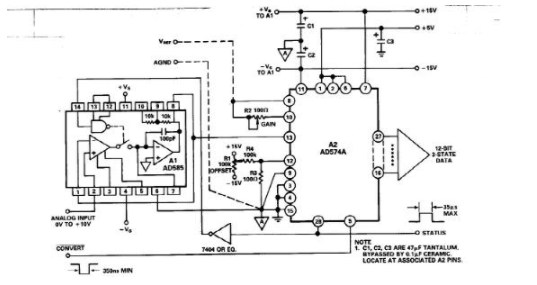

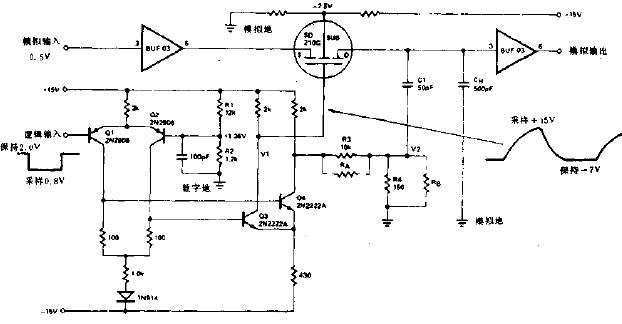

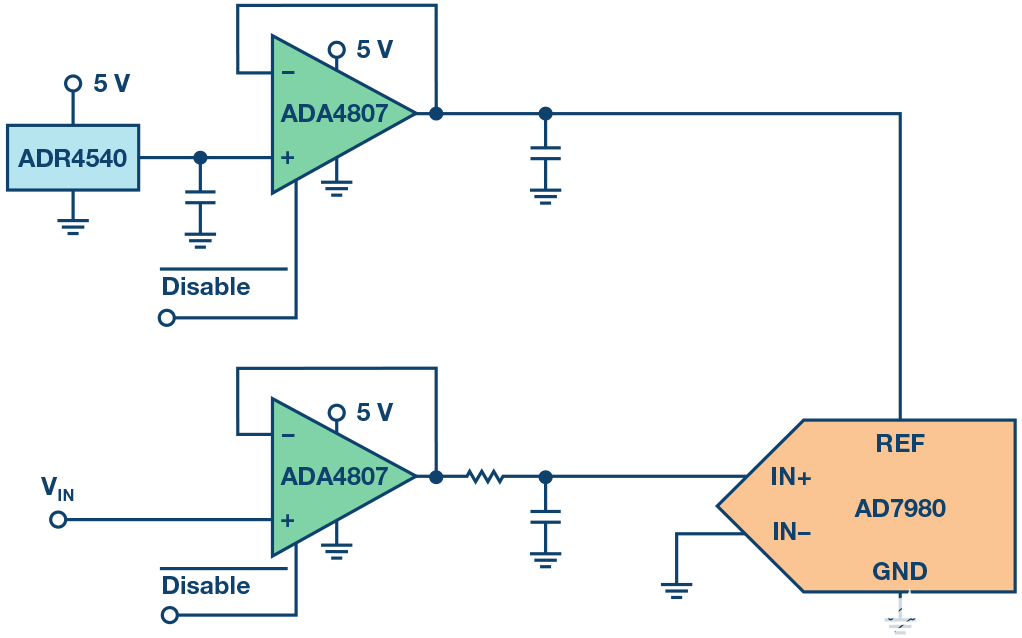

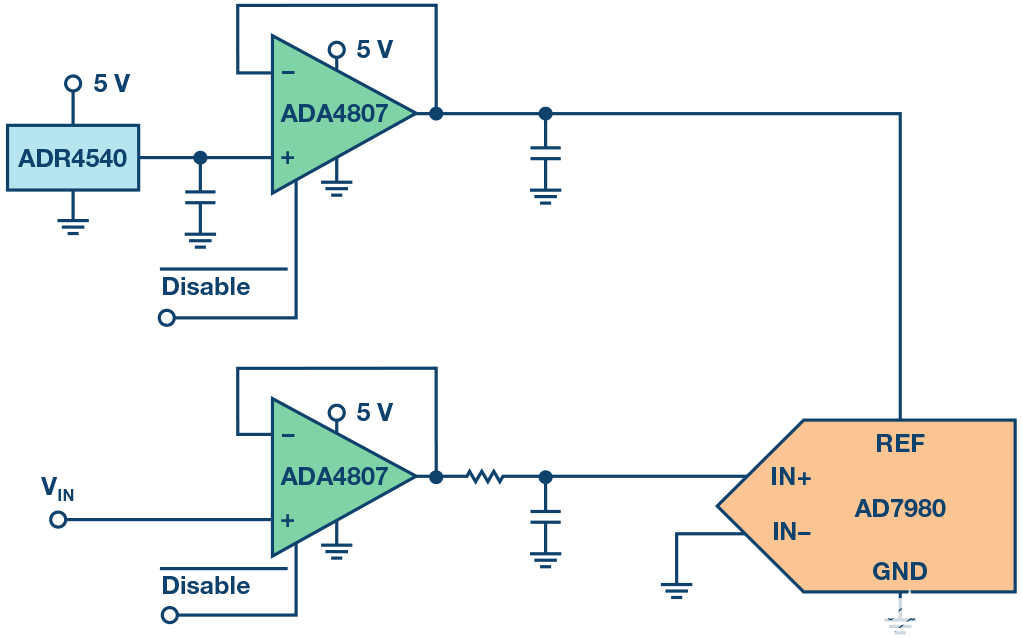

實施采用現代化模數器件和S/H器件的轉換系統并不是一件容易的事,但其采用的硬件功能多樣,將會大有助益。圖8a所示的12位獨立模數轉換器 + S/H轉換系統是一個連接示例,可以按圖示輕松實現,也可以根據其他比例等輕松更改。

此電路使用一個AD585 S/H,在同相單位增益模式下連接,HOLD)保持激活。該模數轉換器為AD574A,連接用于實現單極0至+ 10V范圍,其系統增益和偏置校準分別由R2和R1設置。AD574的狀態輸出驅動AD585 A1的HOLD)輸入,以實現盡可能低的S/H偏移。這需要在TTL級中進行反轉。

如圖所示,轉換由轉換信號發起,并從下降沿開始,狀態線路隨之進入高電平狀態,S/H進入保持狀態。對于12位轉換,AD574A需要35μs(最大值)來執行轉換。由狀態低電平信號表示轉換結束。

所示的模數轉換器微調校準可改變系統增益和偏置,足以應對/H和模數誤差。

該系統的最大吞吐時間由三個因素決定,如下所示。分別是:模數轉換時間、S/H孔徑延遲和采樣時間。轉換時間為:

各時間分別為35μs + 35ns + 3μs,或者總計38.035μs。還可以計算最大吞吐頻率,以此時間的倒數表示:

該頻率假設每個周期只有一個樣本;為了滿足奈奎斯特準則要求的每周期2個數據點,將頻率減半。(還需要注意的是,在S/H之前的任何額外的建立時間也可能需要考慮,使用時可包括IA和/或多路復用器。)

圖8a.帶S/H的獨立12位單極性模數轉換器

在帶有S/H放大器的高速逐次逼近模數轉換應用中,潛在誤差源是來自模數轉換器的回退誤差。逐次逼近模數轉換器表示S/H的動態負載,而轉換周期開始時的MSB負載會因為非零S/H輸出阻抗,在模數轉換器輸入電壓(S/H輸出)上產生瞬變。如果S/H阻抗在高頻率下不夠低,回退誤差可能會超過LSB。

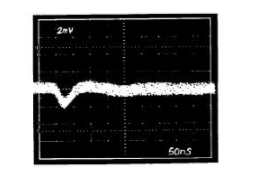

要解決這個問題,需要使用具有低阻抗輸出級的S/H,或具有高反饋的S/H,以實現低回退誤差。如果阻抗足夠低,可以使動態電壓誤差忽略不計,那么模數轉換器負載不會引發問題。AD585輸出級用于實現低動態輸出阻抗,以最小化此誤差。圖8b所示為轉換期間AD585輸出驅動AD574A的放大照片,可說明這一點。注意,MSB開關點上的負向瞬態誤差在持續時間內低而短。

圖 8b.AD585 S/H放大器的輸出驅動AD574A,MSB轉換

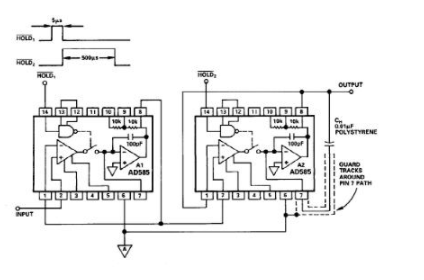

對于既需要快速采集時間,也需要低下降率的應用,可以使用級聯S/H同時滿足這些相互沖突的性能參數。圖9所示的是這樣一個電路,HOLD)1和HOLD)2控制線的驅動方式如時序圖所示。基本理念是,級聯的第一個S/H在第二個達到額定精度之前快速獲取輸入。然后,第一個S/H進入保持狀態,第二個繼續獲取第一個(快速)S/H的輸出端上出現的“輸入”。由于這構成了輸入信號的串聯路徑,因此兩個S/H的誤差會加在一起。

該電路使用兩個串聯的AD585,第一個通常配置用于實現快速采集。使用AD585的內部電容,該級將實現1mV/ms(最大)壓降率。該級進行5μs(HOLD)1信號的寬度)采樣。第二個S/H對第一個的輸出進行500μs(或HOLD)2的寬度)采樣。在這500μs期間,第一級的輸出電壓會下降,最高達0.5mV。這一般是HOLD2寬度(單位:ms)乘以1 mV/ms。

第二個AD585使用一個0.01μF外部CH,它會最大限度降低此級的電壓降幅,降低100倍(第二級和第一級CH的比率)。之后,整個電路的有效壓降變為0.5mV(第一級),加上0.01 mV/ms(第二級)。第二級的保持間隔達幾十ms,所以,此級聯S/H的凈壓降接近500μs間隔的壓降,在本例中為0.5mV。

當然,此方案作出的取舍是:整體信號吞吐量降低。實際上,因為該應用本就打算與速度較慢的模數轉換器配合使用,所以這種取舍可能只會造成很小或根本不會造成影響。此外,如果多路復用器之前使用了多個級聯S/H,此方案可能非常有用,即使很少對單個頻道采樣也能保持較高的整體吞吐率。注意,就此級聯的孔徑時間而言,有效fmax仍由兩個S/H中的第一個決定。本示例所示是同相單位增益S/H。原則上,任一(或兩個)S/H都可以使用其他比例。

對于布局,用戶需要遵循一些重要的通用實用規則。只要使用外部CH,就需要注意使用保護走線將與引腳7相關的PC走線包圍起來。應將其連接至模擬地,連接此引腳的導線越短越好。外部CH應該是低DA型電容,其外部箔片連接至S/H輸出(引腳8)。還請注意,許多S/H應用可能永遠不需要使用外部CH或引腳7。在這種情況下,可以沿封裝附近切割引線,將拾取線路剪至最短。

圖9.環路壓降級聯S/H

電子發燒友App

電子發燒友App

評論