新一年的集創(chuàng)賽已如火如荼的展開~

為了讓大家更多的了解該賽事,小編整理了2021年的優(yōu)秀作品供學(xué)習(xí)分享

在每周一為大家分享獲獎(jiǎng)作品,記得來看連載喲 ~

參賽要求:本科生組

賽題內(nèi)容:

NIC公司最近正在競(jìng)爭(zhēng)一個(gè)8bit DAC芯片設(shè)計(jì)的訂單機(jī)會(huì),需要按照甲方需求盡快提交芯片的設(shè)計(jì)和測(cè)試方案參加評(píng)審會(huì)。你們作為NIC公司的芯片研發(fā)和測(cè)試團(tuán)隊(duì),承擔(dān)了這個(gè)任務(wù),需要在2021年8月31日以前完成芯片的設(shè)計(jì)和測(cè)試方案,方案的好壞直接決定了甲方是否會(huì)和NIC公司合作。

甲方對(duì)于芯片的設(shè)計(jì)和測(cè)試方案要求如下:

1) DAC芯片架構(gòu)為R-2R,分辨率為8bit

2) DAC芯片的接口和封裝形式可自行設(shè)計(jì)

3) 要求基于Multisim實(shí)現(xiàn)該DAC芯片的電路原理仿真(基于分立器件的電路原理功能性仿真)

4) 要求基于Ultiboard實(shí)現(xiàn)該DAC芯片的測(cè)試接口板設(shè)計(jì)

5) 要求基于IECUBE-3100完成該DAC芯片的自動(dòng)化測(cè)試方案設(shè)計(jì),測(cè)試項(xiàng)需要盡量多的覆蓋該DAC芯片的靜態(tài)參數(shù)指標(biāo)和動(dòng)態(tài)參數(shù)指標(biāo)測(cè)試(至少覆蓋:INL&DNL,THD,SFDR,SINAD,SNR),并給出每種指標(biāo)的測(cè)試原理和基于制定測(cè)試平臺(tái)的實(shí)現(xiàn)方式

6) 要求提交該DAC芯片的Multisim仿真源文件、Ultiboard設(shè)計(jì)源文件和Gerber文件以及測(cè)試方案詳細(xì)設(shè)計(jì)文檔

團(tuán)隊(duì)介紹

參賽單位:湖南工業(yè)大學(xué)

隊(duì)伍名稱:會(huì)飛的特斯拉

參賽人員:張佳棟 汪敏琪 尋彬彬

總決賽獎(jiǎng)項(xiàng):三等獎(jiǎng)

1.項(xiàng)目簡(jiǎn)介

1.1 DAC設(shè)計(jì)

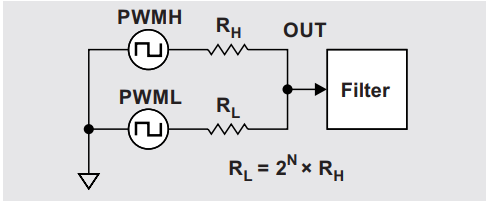

本數(shù)模轉(zhuǎn)換器由開關(guān)電路、濾波電路、R-2R電阻網(wǎng)三部分組成,控制信號(hào)通過控制開關(guān)電路的開通與關(guān)斷,進(jìn)而控制基準(zhǔn)電壓施加在不同的R-2R電阻網(wǎng)接口上,來決定電阻網(wǎng)最后的輸出電壓,最后通過二階低通有源濾波電路對(duì)輸出信號(hào)進(jìn)行濾波,使其輸出波形更加光滑,提高了輸出波形的精度。為了避免輸出非光滑信號(hào)時(shí)由于濾波電路本身的特性而產(chǎn)生失真,本設(shè)計(jì)加入了一個(gè)撥動(dòng)開關(guān)SW1,控制濾波電路與電阻網(wǎng)之間的連接與斷開。以消除此種影響。

開關(guān)電路是由八個(gè)nMOS與八個(gè)pMOS構(gòu)成八個(gè)CMOS開關(guān)。每個(gè)CMOS開關(guān)輸出端連接一個(gè)運(yùn)放,其作用是防止八個(gè)CMOS開關(guān)電路相互干擾,導(dǎo)致輸出信號(hào)失真。同時(shí)每個(gè)運(yùn)放的輸出管腳與反向輸入端管腳短接,產(chǎn)生電壓跟隨的作用,不會(huì)影響開關(guān)電路的輸出。

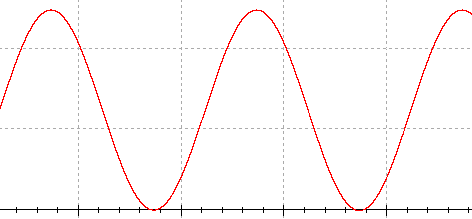

本數(shù)模轉(zhuǎn)換器輸出的正弦波形如下圖所示。

1.2 測(cè)試方案

1.2.1 IECUBE-3100介紹

IECUBE-3100是一個(gè)面向半導(dǎo)體測(cè)試教學(xué)的實(shí)訓(xùn)平臺(tái),Ready to teach的完整教學(xué)方案產(chǎn)品,包含教學(xué)課件、實(shí)驗(yàn)指導(dǎo)書和實(shí)踐實(shí)驗(yàn)平臺(tái)。課程內(nèi)容及實(shí)驗(yàn)設(shè)置完全來源于實(shí)際工業(yè)應(yīng)用,適合半導(dǎo)體測(cè)試基礎(chǔ)教學(xué)、實(shí)訓(xùn)及競(jìng)賽等應(yīng)用場(chǎng)合。

IECUBE-3100的可用資源包括可編程直流電源(0V~6V、0V~25V、-25V~0V)、雙通道示波器、邏輯分析儀、數(shù)字I/0、波形發(fā)生器、通用PCI DUT接口、面包板、數(shù)字萬用表。支持USB、WIFI連接。可用LabVIEWCPython來進(jìn)行開發(fā)。

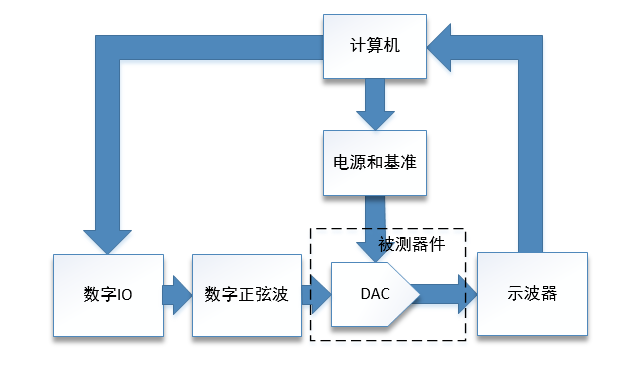

1.2.2 測(cè)試流程圖

1.2.3 DNL / INL測(cè)試

差分非線性(DNL)是指DAC局部(細(xì)節(jié))的非線性程度,可以這樣理解,在理想的情形下,在數(shù)字編碼中的1LSB變化對(duì)應(yīng)于輸出模擬信號(hào)的嚴(yán)格的1個(gè)V_LSB變化。DAC從一個(gè)模擬電壓輸出轉(zhuǎn)換到下一個(gè)模擬電壓輸出應(yīng)該有嚴(yán)格的1個(gè)V_LSB模擬輸入的變化。在模擬信號(hào)對(duì)應(yīng)于1個(gè)V_LSB數(shù)字變化大于或小于1個(gè)V_LSB的地方,被稱為DNL誤差。

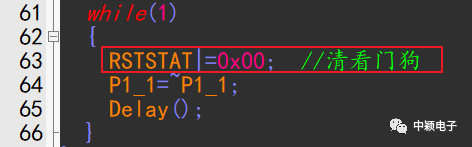

通過配置3100的數(shù)字IO產(chǎn)生8位二進(jìn)制數(shù)字鋸齒信號(hào),將信號(hào)接入接口板中的D0-D7接口,其中D7為最高位,D0為最低位,并將基準(zhǔn)電壓通過接口板中的REF接口接入,供電電壓通過接口板中的VDD接口接入,數(shù)字鋸齒信號(hào)經(jīng)過數(shù)模轉(zhuǎn)換器轉(zhuǎn)換后得到輸出波形,此時(shí)將SW1撥至斷開濾波電路位置,3100的示波器通過Vo2采集到數(shù)模轉(zhuǎn)換器的輸出信號(hào)并傳入到LabVIEW中。通過設(shè)置采樣點(diǎn)和采樣時(shí)間來獲得一個(gè)周期的完整的鋸齒信號(hào),為了減少偶然誤差,將采集頻率設(shè)置為數(shù)字IO輸出頻率的十倍,即每一個(gè)數(shù)據(jù)點(diǎn)采集十次取平均值,即為該數(shù)據(jù)點(diǎn)的模擬電壓,通過LabVIEW編程快速將256個(gè)點(diǎn)的模擬電壓測(cè)出,從第二個(gè)數(shù)據(jù)點(diǎn)開始每個(gè)數(shù)據(jù)點(diǎn)的輸出電壓與前一個(gè)數(shù)據(jù)點(diǎn)的輸出電壓之差減Vlsb后再除Vlsb所得的最大值即為該數(shù)模轉(zhuǎn)換器的DNL。DNL積分后得到INL。

1.2.4 THDSINADSFDRSNR測(cè)試

1.2.4.1 測(cè)試步驟

電源施加合適的電源電壓和參考電壓,輸出端接負(fù)載電阻;

數(shù)字碼型發(fā)生器給待測(cè)DAC施加規(guī)定幅度和規(guī)定頻率fs的數(shù)字正弦信號(hào);

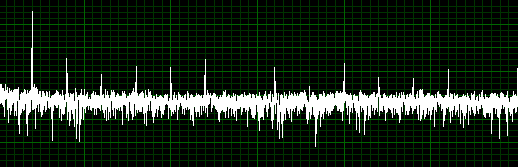

待DAC工作穩(wěn)定后,通過對(duì)輸出波形進(jìn)行FFT變換得到輸出正弦波形的功率譜,分別按定義計(jì)算出基波信號(hào)分量Vs、各次諧波信號(hào)分量Vi、噪聲信號(hào)分量Vn、最大雜波分量Vz。經(jīng)過FFT變換后,得到的圖像如下圖。

1.2.4.2 信號(hào)分量測(cè)量

通過配置3100的數(shù)字IO產(chǎn)生8位二進(jìn)制數(shù)字正弦信號(hào),將信號(hào)接入接口板中的D0-D7接口,其中D7為最高位,D0為最低位,并將基準(zhǔn)電壓通過接口板中的REF接口接入,供電電壓通過接口板中的VDD接口接入,數(shù)字正弦信號(hào)經(jīng)過數(shù)模轉(zhuǎn)換器轉(zhuǎn)換后得到輸出波形,此時(shí)將SW1撥至接入濾波電路的相應(yīng)位置,3100的示波器通過Vo1采集到數(shù)模轉(zhuǎn)換器的輸出信號(hào)并傳入到LabVIEW中。對(duì)采集到的波形通過進(jìn)行諧波失真分析,采集到波形的基波電平和2-10次諧波信號(hào)分量

輸出信號(hào)進(jìn)行偏移和縮放后進(jìn)行諧波失真分析得到信號(hào)的基頻,同時(shí)通過輸出信號(hào)經(jīng)過FFT變換得到信號(hào)的功率譜。

進(jìn)行諧波失真分析將高級(jí)搜索范圍設(shè)置為基頻的倍數(shù),循環(huán)10次,可以得到采集波形的基波信號(hào)分量V_s和2-10次諧波信號(hào)分量V_i。

在各次諧波信號(hào)分量中判斷最大值,得到最大雜波分量V_z。將輸出信號(hào)再一次進(jìn)行諧波失真分析,設(shè)置最高諧波為1,高級(jí)搜索范圍為基波的倍數(shù),循環(huán)10次,進(jìn)而得到采集波形去除基波和2-10次諧波之后的波形,并將這個(gè)波形傳輸?shù)?a href="http://www.nxhydt.com/tags/濾波器/" target="_blank">濾波器模塊對(duì)基頻倍數(shù)附近很小范圍進(jìn)行的頻率進(jìn)行濾波,最后得到調(diào)制后的信號(hào),調(diào)制信號(hào)電平標(biāo)準(zhǔn)差即為噪聲信號(hào)分量V_N。

1.2.4.3 參數(shù)計(jì)算

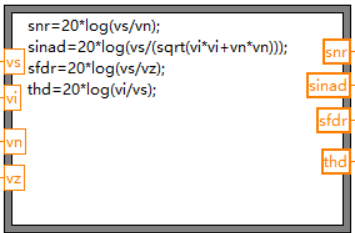

測(cè)量得到輸出模擬信號(hào)的基波信號(hào)分量V_s、各次諧波信號(hào)分量V_i、最大雜波分量V_z、噪聲信號(hào)分量V_N,在LabVIEW中的公式節(jié)點(diǎn)中插入各項(xiàng)參數(shù)的計(jì)算公式,即可得到數(shù)模轉(zhuǎn)換器的動(dòng)態(tài)參數(shù)。具體公式如下

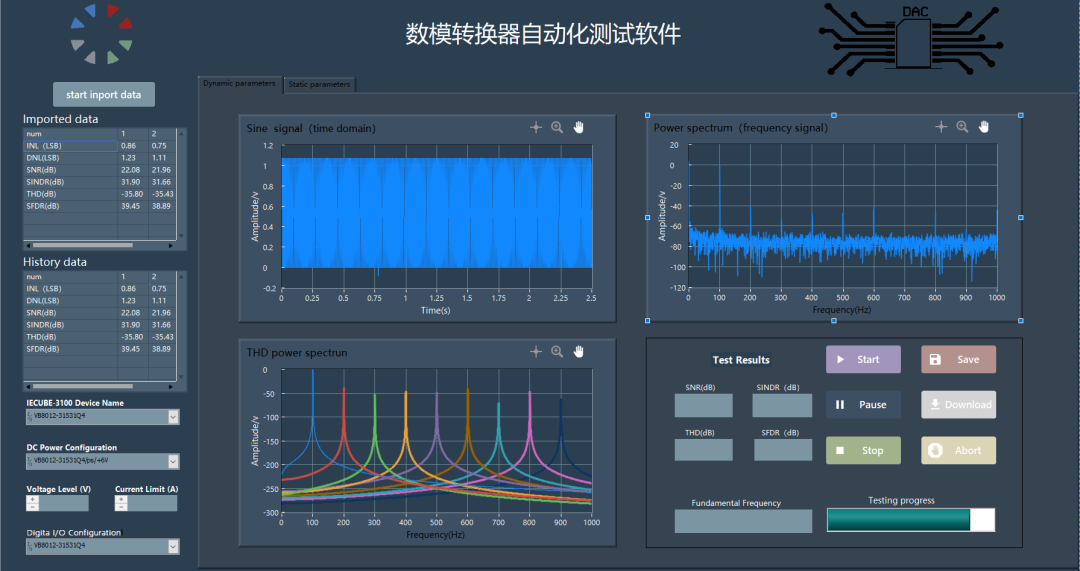

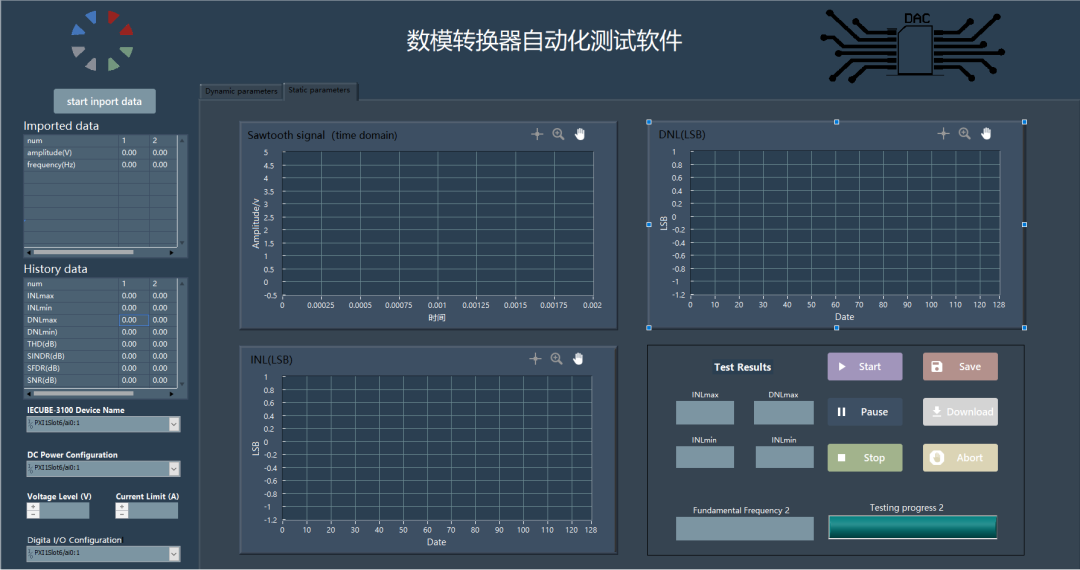

2.軟件界面介紹

2.1 動(dòng)態(tài)參數(shù)測(cè)試界面

2.2 靜態(tài)參數(shù)測(cè)試界面

本軟件分為靜態(tài)測(cè)試和動(dòng)態(tài)測(cè)試兩個(gè)模塊,測(cè)試時(shí),在左側(cè)列表中選擇IECUBE-3100儀器、配置直流電源、數(shù)字I/O和示波器。儀器配置好后點(diǎn)擊“start inport data ”使數(shù)據(jù)導(dǎo)入軟件,此時(shí)“inported date”界面中顯示輸出信號(hào)的各項(xiàng)參數(shù),然后點(diǎn)擊“start”開始測(cè)試模擬信號(hào)的靜態(tài)參數(shù)和動(dòng)態(tài)參數(shù),“Test Results”顯示各項(xiàng)測(cè)試結(jié)果。

3.參賽體會(huì)

3.1 參賽感受

在比賽過程中,為了解決遇到的問題,不斷在集成電路測(cè)試領(lǐng)域進(jìn)行探索,我們的軟硬件設(shè)計(jì)能力在學(xué)習(xí)過程中得到很大提升。

此次大賽作為集成電路行業(yè)頂尖的比賽,云集了全國(guó)250多家院校,3000多支隊(duì)伍的參加,經(jīng)過初賽、分區(qū)賽,NI杯共有24支隊(duì)伍進(jìn)入總決賽,能與這么多優(yōu)秀的大學(xué)生進(jìn)行同臺(tái)競(jìng)技,讓我們開拓了視野,將目光不止局限于學(xué)校。通過比賽,也使我們更加了解了集成電路領(lǐng)域的發(fā)展,提升了自己的能力。非常感謝賽事組委會(huì)的老師和工作人員對(duì)此次大賽的辛苦付出,讓我們可以有這樣一個(gè)充分展示自己的平臺(tái)。

3.2 后續(xù)計(jì)劃

本數(shù)模轉(zhuǎn)換器將會(huì)進(jìn)一步優(yōu)化,使其達(dá)到更高的精度。

自動(dòng)化測(cè)試軟件后續(xù)將會(huì)精簡(jiǎn)算法,使測(cè)試達(dá)到更高的速度

后續(xù)將會(huì)豐富軟件的功能,使其可以測(cè)得更多的參數(shù),可以更加全面的了解器件性能。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論