在為高性能系統選擇寬帶模數轉換器(ADC)時,應考慮許多模擬輸入規格,例如ADC分辨率、采樣速率、信噪比(SNR)、有效位數(ENOB)、輸入帶寬、無雜散動態范圍(SFDR)以及差分或積分非線性。

對于每秒千兆采樣(GSPS)ADC,SFDR可能是最重要的交流性能規格之一。它定義了ADC和系統從其他噪聲或任何其他雜散頻率中破譯載波信號的能力。

為了實現GSPS ADC中使用的轉換速度,可以采用幾種以高目標采樣率捕獲信號的架構。但是,其中一些架構的使用是以犧牲全帶寬 SFDR 性能為代價的。

為了了解轉換器SFDR對系統的影響,我們回答了設計工程師提出的一些常見問題,包括SFDR規范的細節、轉換器數據手冊中如何描述SFDR規范、限制或最大化ADC性能的架構以及限制SFDR性能的系統設計方面。

我已經看到SFDR在數據表中有和沒有警告。究竟什么是 SFDR?

能夠從噪聲中辨別信號是許多信號采集系統的一個關鍵方面。無論是定義的電信協議、雷達掃描還是測量儀器,采集和破譯微弱信號都是任何差異化系統性能的核心。

SFDR表示可以與大干擾信號區分開來的最小功率信號。它定義了載波功率的均方根(rms)值與頻域中下一個最重要雜散信號的均方根值之間的動態比,例如在快速傅里葉變換(FFT)中。因此,根據定義,該動態范圍必須沒有其他雜散頻率或雜散。

SFDR通常量化為相對于目標載波與下一個最重要頻率的功率的范圍,以功率單位(dBc)為單位。但是,它也可以參考以功率單位(dBFS)為單位的滿量程信號。這是一個重要的區別,因為目標載波可能是功率相對較低的信號,遠低于ADC的滿量程輸入。在這種情況下,SFDR在將信號與其他噪聲和雜散頻率區分開來方面變得至關重要。

什么限制了 ADC 的 SFDR?

諧波頻率是基頻的整數倍。對于設計良好的單芯片ADC內核,SFDR通常由載波頻率與目標基頻的二次或三次諧波之間的動態范圍決定。一些窄帶ADC數據手冊僅在窄帶內定義SFDR,通常是當二次和三次諧波落出帶外時。其他數據手冊可能會描述寬帶寬下的SFDR,并需要注意該性能需要滿足哪些條件。

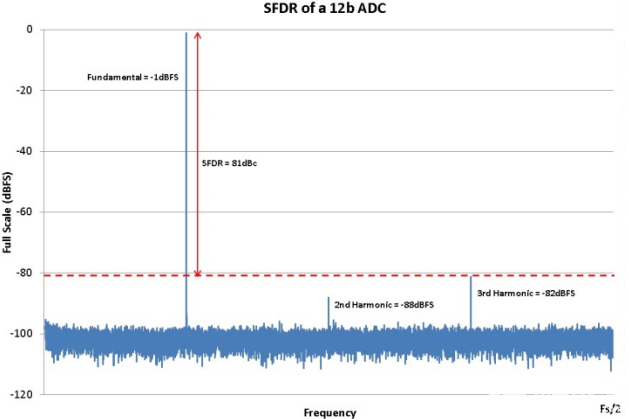

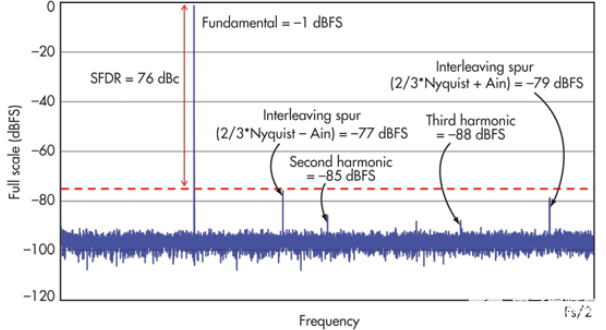

雖然二次或三次諧波通常可能是主要的雜散頻率,但由于其他系統原因,有些雜散也可能限制GSPS ADC的SFDR性能。例如,多個交錯式ADC內核可以通過在頻域中引入交錯偽像來創建雜散頻率。這些可能在幅度上大于基頻的二次或三次諧波。因此,它們將是SFDR的主要限制因素。雖然這似乎違反直覺,但SFDR也可以在交錯式ADC數據手冊中指定,并告誡交錯雜散被排除在計算之外(圖1)。

圖1.這是單芯片12位ADC的FFT,顯示三次諧波是SFDR的主要貢獻因素。在這種情況下,從基波(–1 dBFS)到三次諧波(–82 dBFS)的動態范圍為–81 dBc,因為它與載波功率有關。

窄帶SFDR可以外推到寬帶SFDR嗎?

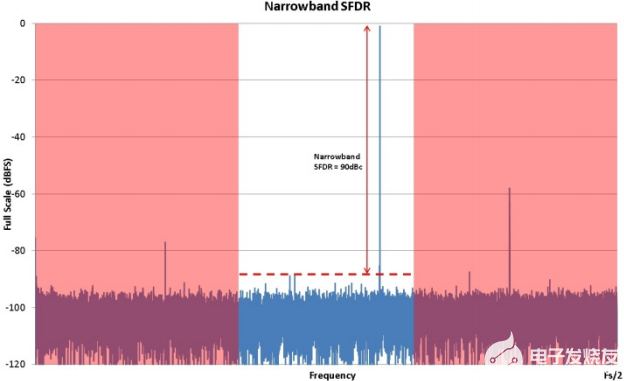

如果系統只關注窄帶頻譜,則可以使用帶通抗混疊輸入濾波器來抑制目標頻帶外的諧波或偽影。這對于某些應用可能工作正常,只要不需要觀察此濾波頻帶內的信號即可。但對于寬帶信號采集系統來說,這是不可行的。在某些數據手冊中,ADC的SFDR也可以指定在遠小于ADC全輸入帶寬的窄帶寬上。

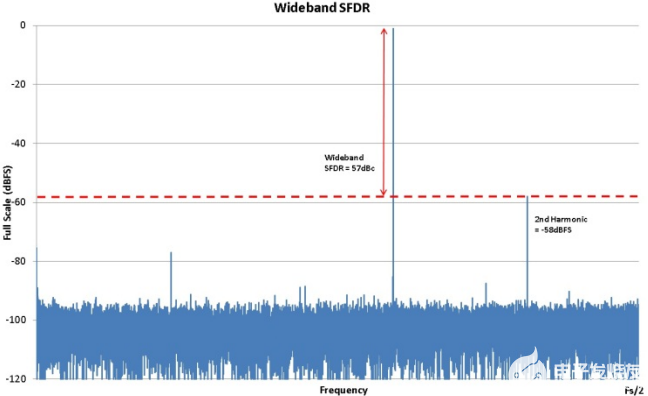

通常,不能假設可以外推窄頻帶上的SFDR,以便在Fs/2的更寬或全奈奎斯特頻帶上獲得相同的性能。這主要是因為基波窄帶的頻率規劃是有意建立的,以濾除并將高次諧波推出目標頻帶。如果去掉濾波器,那么這些諧波和其他雜散現在將成為系統中寬帶SFDR的一部分(圖2和圖3)。

圖2.窄帶應用可以有效地使用寬帶SFDR較差的ADC。通過使用抗混疊濾波器來抑制紅色陰影區域的頻率,任何諧波或雜散現在都會被帶外濾除,否則會導致SFDR較差。

圖3.使用相同的條件,但假設ADC濾波被移除,那么寬帶諧波或雜散現在將限制SFDR。這說明了一種情況,即不能假設將優秀的窄帶SFDR外推到寬帶SFDR。

差分輸入ADC的SFDR是否會受到其他前端系統組件的影響?

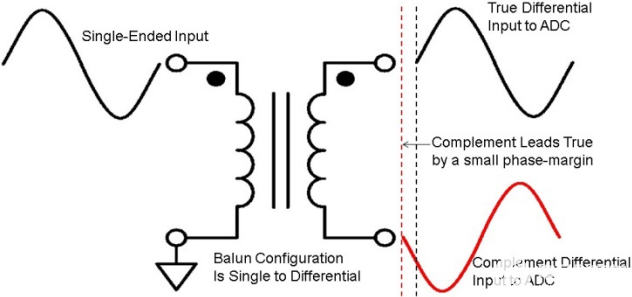

大多數高速ADC采用差分輸入結構,可提供良好的共模噪聲抑制能力。然而,這需要許多采集系統將單端信號轉換為ADC輸入前端的差分信號。無源巴倫或變壓器和有源放大器是這種單差信號轉換過程的主要選擇。雖然系統這一部分有許多高性能元件選擇,但即使是最好的解決方案也會嵌入一些小的差分不平衡,這些不平衡會使目標信號失真,并通過ADC降低SFDR。

ADC前端差分輸入信號每側之間的相位失配導致基波信號諧波的功率增加。當差分信號的一側相對于其周期在時間上領先另一側一定量的相位時,就會發生這種情況。這種效應如圖4所示,當差分對的一側領先另一側時,周期相位的幅度很小。

圖4.在這種情況下,巴倫輸出與ADC差分輸入的相位失配為幾度。這可能導致FFT中的二次諧波高于差分輸入相位完美匹配時的二次諧波,從而影響SFDR。

差分信號采集系統前端的另一個不平衡可能是幅度失配。當差分信號的一側增益與其補碼不同時,ADC輸入將一側視為較大的信號,另一側視為較小的信號。否則,這會降低基波信號的全部功率,并降低SFDR(以dBc為單位)。差分輸入之間2 dB幅度失配將導致輸入信號功率滿量程降低1 dB。這些前端信號完整性問題都有可能降低ADC的SFDR以及整個系統的信號解密能力。

有哪些ADC架構可能會限制SFDR?

采樣速率高達1 GSPS及以上的多個ADC采用一對或幾個分立通道或內核的交錯方案,以實現全高速數據速率。例如,可以使用雙通道ADC,每個內核通過交錯在采樣采集過程中旋轉,以實現全采樣速率。當一個通道正在采樣時,另一個通道仍在處理以前的樣本。交錯架構還可以使用三個或更多ADC內核。

使用交錯方法,多個ADC內核可以并行工作,以實現比單個內核更高的采樣速率。但是,每個內核的輸入之間存在相位、偏移、增益和帶寬的細微差異。結果是可以在頻譜中引入新的交錯偽像和鏡像雜散,從而降低ADC的寬帶SFDR。這將降低系統的動態范圍及其區分目標信號和交錯雜散信號的能力。為了減輕交錯式ADC的偽影,系統工程師可能必須閱讀有關特殊校準模式和雜散規劃方法的詳細應用筆記。

單芯片ADC架構只有一個處理內核,不會出現交錯雜散。單流水線內核ADC是寬帶轉換器的一個例子,它將吹捧相對較高的SFDR,通常受二次或三次諧波的限制。

交錯ADC在頻域中的性能如何?

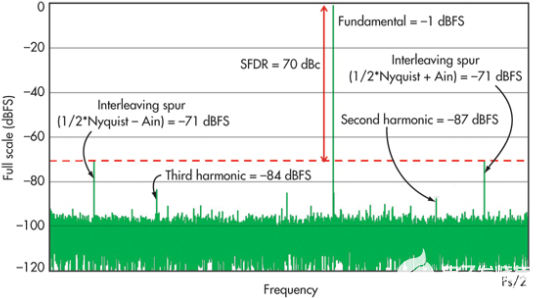

對于包含三個分立交錯內核的采樣架構,有兩個增益和相位鏡像雜散和一個失調雜散(圖 5)。在奈奎斯特× 2/3 處可以看到偏移雜散,但在這種情況下不是 SFDR 的主要貢獻者。SFDR限制增益和相位雜散在(2/3 × Nyquist ±模擬輸入頻率下可見。

圖5.本FFT顯示了交錯系統板上使用的三個分立ADC。請注意相關的交錯雜散偽像,與二次諧波(–8 dBFS)相比,這些偽像將SFDR限制為–85 dBc。

規模上最大的刺激將是該系統SFDR的主要貢獻者。如果沒有交錯雜散,SFDR將是從基頻到二次諧波的動態范圍。在這種特殊情況下,由于交錯鏡像雜散,SFDR的性能損失為–8 dB。

對于包含四個分立交錯內核的采樣架構,有三個增益和相位鏡像雜散以及兩個失調雜散(圖 6)。在奈奎斯特和奈奎斯特存在<>/<>×偏移雜散,在(奈奎斯特 – 模擬輸入頻率)處存在另一個鏡像雜散,但在這種情況下,這些不是SFDR的主要貢獻者。顯性增益和相位雜散出現在(<>/<>×奈奎斯特±模擬輸入頻率)。

圖6.該FFT顯示了交錯系統板上使用的四個分立ADC。請注意,與三次諧波(–13 dBFS)相比,在奈奎斯特±Ain×84/<>時影響SFDR的相關圖像雜散偽影,否則SFDR將SFDR限制為–<> dBc。

如果這些雜散的幅度大于二次或三次諧波,它們將成為系統SFDR的主要貢獻者。如果沒有交錯雜散,SFDR將是從基頻到三次諧波的動態范圍。在這種特殊情況下,由于交錯鏡像雜散,SFDR的性能損失為–13 dB。

其他 SFDR 限制

SFDR性能下降的另一個潛在領域是系統設計,它允許外部噪聲耦合到ADC的模擬或時鐘輸入端。此外,如果系統板布局未經過仔細規劃,ADC的數字輸出有可能耦合回輸入端。外部噪聲也可能耦合到ADC的基準電壓源、電源或接地域。如果噪聲足夠大且呈半周期性,則在系統的頻域中,它可能顯示為與基頻或ADC架構無關的不需要的SFDR限制雜散。

GSPS ADC 的未來

GSPS ADC現在可提供高寬帶SFDR,而沒有過去系統性能有限的交錯偽像。AD9680是一款雙通道、14位、1 GSPS ADC,采用78 GHz輸入時可實現1 dBc的SFDR。AD9625是一款12位、2 GSPS ADC,采用80 GHz輸入時提供1 dBc的典型寬帶SFDR。

SFDR是GSPS和ADC中重要且關鍵的性能指標。寬帶SFDR通常受到基波信號的二次或三次諧波的限制。單芯片流水線ADC和其他先進架構正在推動高性能GSPS轉換器的新領域。它們在頻域中不會出現以往在GSPS空間的ADC架構中存在的交錯雜散。

對于那些需要寬帶響應的應用程序,導航、規劃和刪除這些工件可能會有問題。新的解決方案解決了這些系統問題,可在寬帶頻譜上提供最先進的SFDR性能。

審核編輯:郭婷

電子發燒友App

電子發燒友App

評論