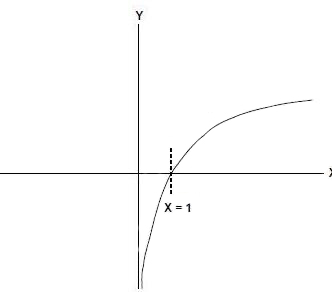

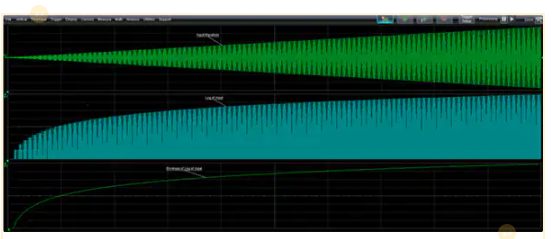

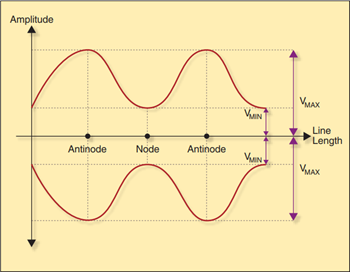

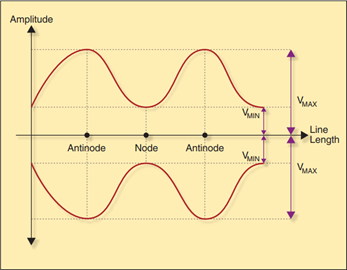

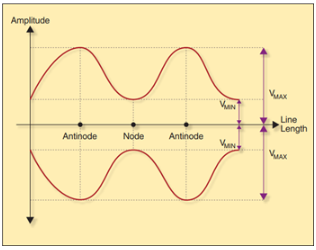

術語對數放大器,正如通常理解的那樣,是指計算輸入信號包絡對數的器件。在8307 MHz 500 dB對數放大器AD90對10 MHz正弦波對100 kHz三角波調制的8 MHz正弦波(見圖10)的響應中,請注意,示波器照片上的輸入信號由100 MHz信號的許多周期組成,使用示波器的時間/格旋鈕壓縮在一起。我們這樣做是為了顯示信號的包絡,重復頻率要慢得多,為<> kHz。隨著信號包絡的線性增加,我們可以在輸出響應中看到特征log(x)形式。相反,如果我們的測量設備是線性包絡檢測器(例如二極管檢測器),則輸出仍將是三波。

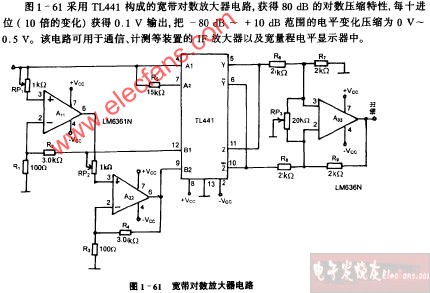

圖8:對數放大器對線性包絡斜坡的響應

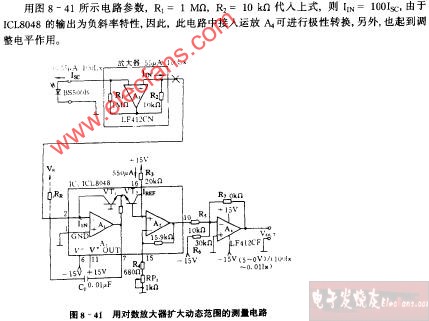

因此,對數放大器指示對數域中信號的交流幅度。通常,對數放大器用于測量信號強度,而不是檢測信號內容。用于描述這種類型的對數放大器的術語“解調”有點誤導,但由于對數放大器恢復信號包絡的對數(類似于解調AM的過程),因此已采用術語解調來描述這種類型的設備。

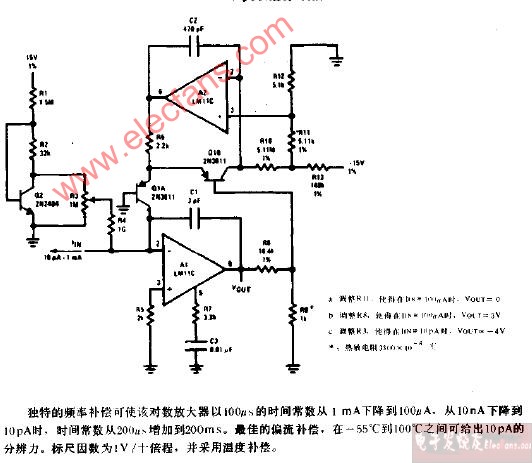

解調對數放大器的操作

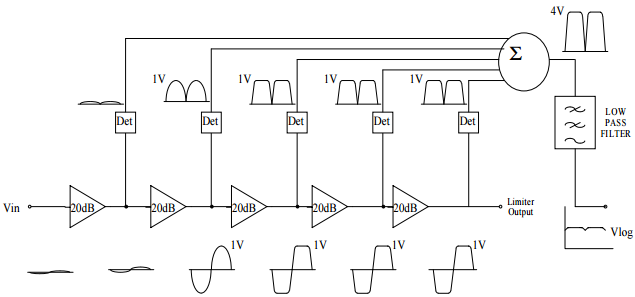

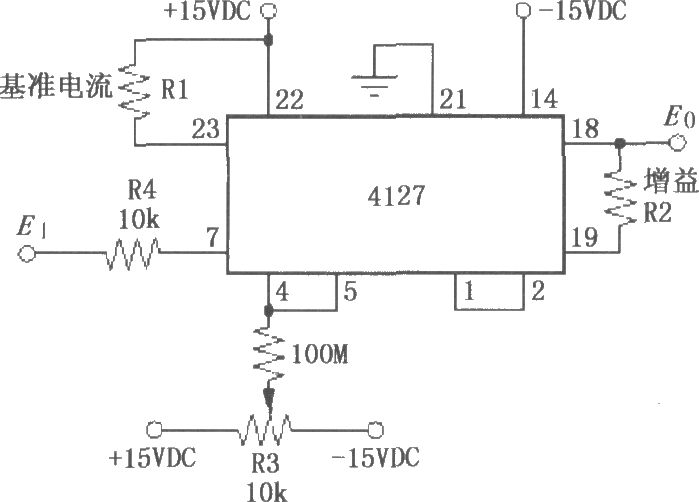

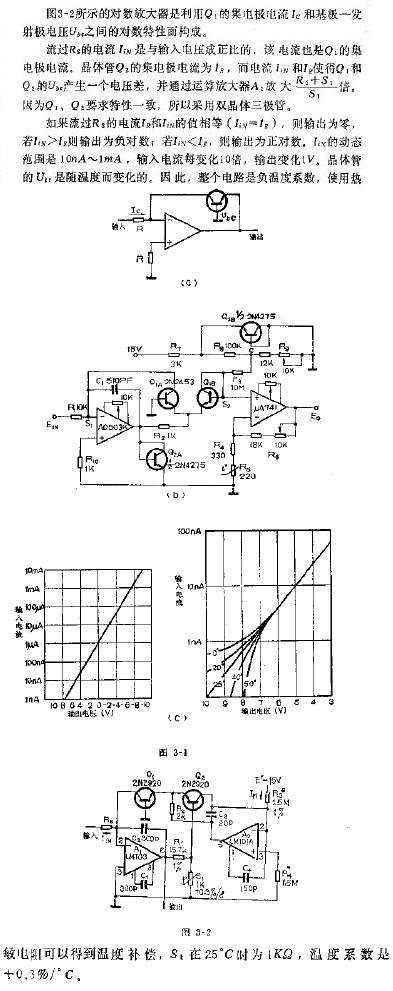

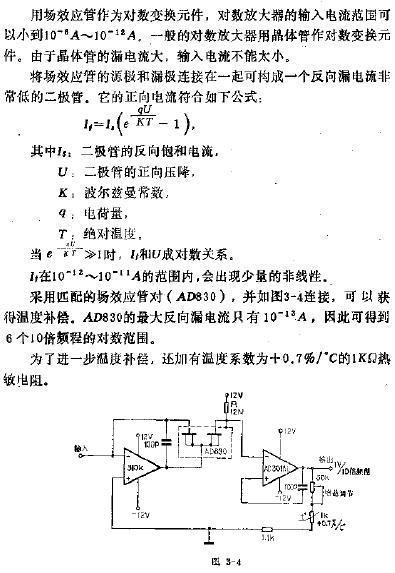

對數放大器簡化框圖(見圖9)的核心是放大器的級聯鏈。這些放大器具有線性增益,通常在10至20 dB之間。為簡單起見,我們選擇了5個放大器的鏈,每個放大器的增益為20 dB或10X。現在,想象一下一個小正弦波被饋入鏈中的第一個放大器。第一個放大器在將信號施加到第二個放大器之前,會將信號增益提高10倍。因此,當信號通過每個后續級時,它被額外放大20 dB。

圖 9:對數放大器框圖

現在,隨著信號沿著增益鏈向下移動,它將在某個階段變得如此之大,以至于它將開始在精確的水平上削波或限制,在本例中,它被設置為1 Vpk。

在信號在其中一級進入限幅后(這發生在圖9中第三級的輸出端),限幅信號繼續沿著信號鏈向下移動,保持其1 Vpk幅度。

每個放大器輸出端的信號也被饋入全波整流器(在圖9中標記為Det)。如圖所示,這些整流器的輸出相加,夏季的輸出施加到低通濾波器,以消除整流信號的紋波。這會產生對數輸出(通常稱為“視頻”輸出),這將是穩態交流輸入信號的穩態直流輸出。

要了解此信號轉換如何生成輸入信號包絡的對數,請考慮如果輸入信號減少 20 dB 會發生什么情況。如圖所示,夏季的未過濾輸出約為 4 Vpk(來自 3 個限制階段和第四個即將限制的階段)。如果我們將輸入信號減少 10 倍,則少一個級將受到限制。該階段的電壓會將夏季的輸出降低到大約 3 V。如果我們將輸入信號再降低 20 dB,夏季的輸出將降至約 2 V。

因此,輸入端每變化1 dB,輸出就會變化20 V。我們可以將對數放大器描述為具有50 mV/dB的斜率。這與以mV/dB為單位的斜率隨輸入電平變化的二極管檢波器的關鍵區別。對數放大器的明顯優點是它具有更高的動態范圍和恒定的斜率。然而,二極管檢波器傳遞函數在高精度很重要的情況下具有優勢。由于二極管電路在高輸入電平下具有非常高的分辨率(即每dB的電壓更高),因此對功率進行小幅調整將更容易。

斜率和截距方面的傳遞函數

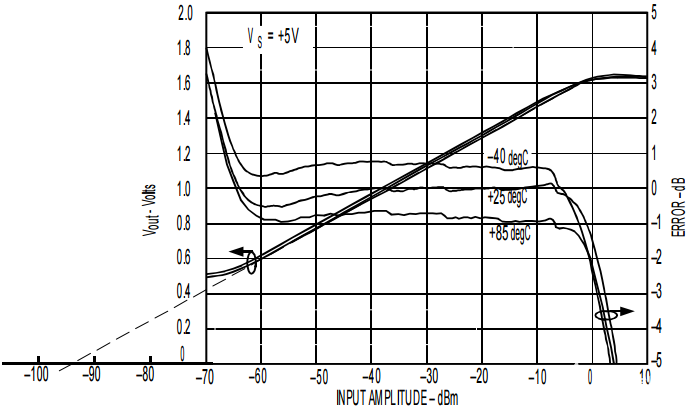

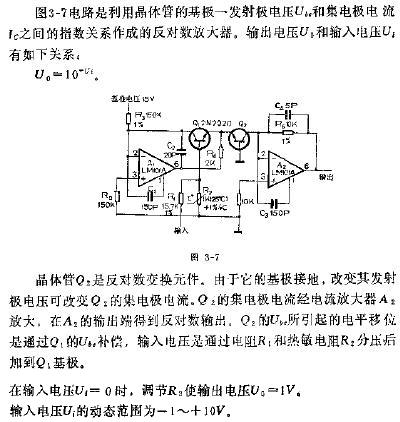

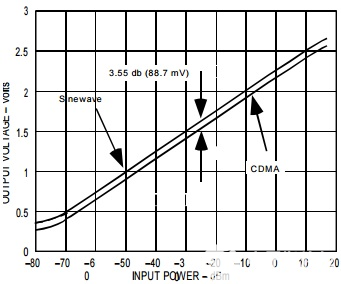

與二極管檢波器電路一樣,斜率和截距是定義對數放大器傳遞函數的兩個規格。AD900(8313 MHz至100.2 GHz 5 dB對數放大器)在65 MHz時的傳遞函數顯示,輸入端發生10 dB變化時,輸出電壓變化約180 mV。由此我們可以推斷出傳遞函數的斜率為10 mV/dB。

圖 10: 對數放大器的斜率和截距

現在,我們可以看到,當輸入信號降至約-65 dBm以下時,響應開始趨于平緩,器件處于其范圍的底部。但是,如果我們推斷傳遞函數的線性部分,直到它到達水平軸,我們就會到達一個我們稱之為截距的點(在這種情況下約為 -93 dBm)。請注意,對數放大器規格中的約定是指定此 x 軸截距,而不是我們用于指定二極管檢波器的 y 軸截距。

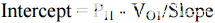

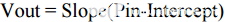

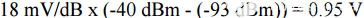

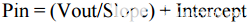

特定器件的斜率通過簡單的兩點校準來確定,即測量線性工作范圍內的兩個已知輸入電平的輸出電壓。坡度很簡單,

截距由方程給出,

一旦我們知道特定設備的斜率和截距,我們就可以使用簡單的公式計算出線性范圍內(在本例中約為-65 dBm至0 dBm)內任何輸入電平的對數放大器的理想輸出電壓,

例如,如果輸入信號為 -40 dBm,則輸出電壓將等于,

值得注意的是,截距值的增加會降低輸出電壓。

在實際系統中,我們將使用對數放大器根據測量的輸出電壓估計(未知)輸入信號。為此,我們重新排列方程 [3],

日志一致性

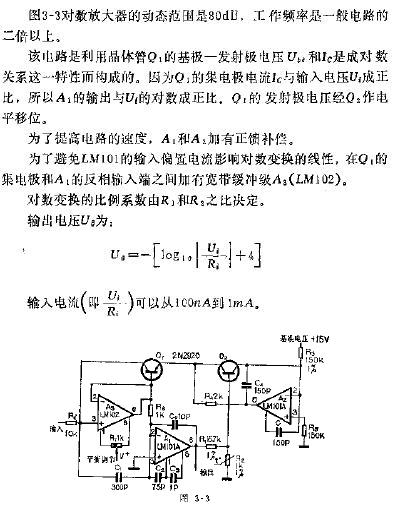

就像我們檢查二極管檢波器的線性度一樣,我們可以繪制對數放大器響應的線性度。談論對數函數的線性有點令人困惑,但更具體地說,我們對設備的傳遞函數與log(x)數學函數的一致性感興趣。

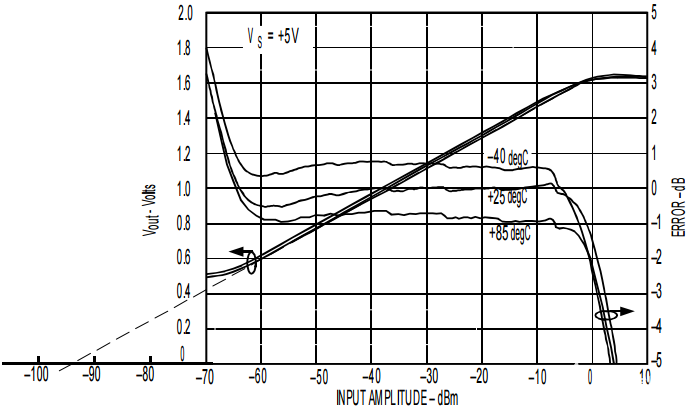

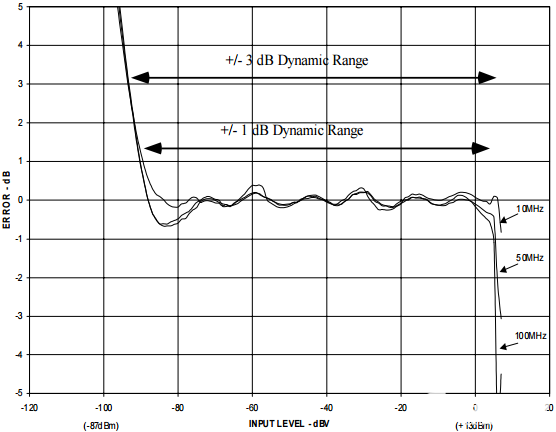

因此,對數一致性顯示了器件保持恒定斜率的范圍,還顯示了輸入范圍內的紋波或任何非線性度。對數放大器的動態范圍定義為斜率保持在某個誤差帶內的范圍,通常為±1 dB或±3 dB。例如,在圖11中,±1 dB動態范圍約為95 dB(從+5 dBV到-90 dBV)。

圖 11: 對數放大器的對數一致性

溫度穩定性

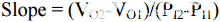

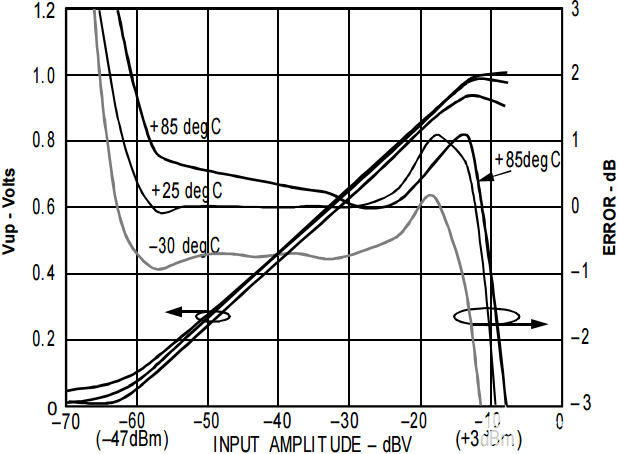

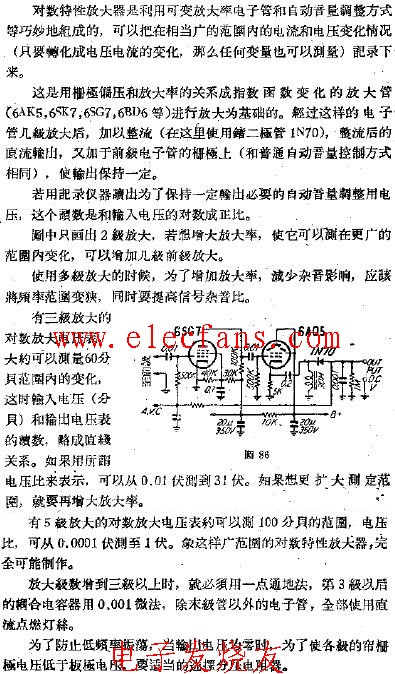

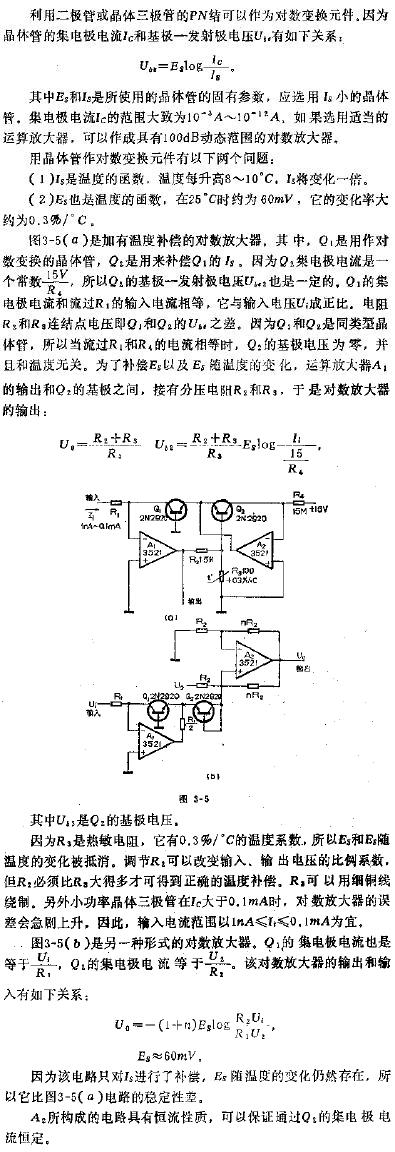

與二極管的情況一樣,我們還可以繪制對數放大器相對于計算的斜率和室溫截距隨溫度變化的對數一致性。8314 dB對數放大器AD45在2.5 GHz時的傳遞函數和對數一致性(圖12)表明,在大約1 dB(-40 dBV至-17 dBV)的范圍內,溫度漂移和對數一致性完全在±57 dB誤差帶內。在精密應用中,設備不應在此范圍之外運行。請注意,對于0 dBm(-13 dBV)的輸入電平,25 oC時的對數一致性誤差仍然相當不錯,約為+0.7 dB。然而,隨著溫度的流逝,特別是在寒冷的情況下,誤差急劇增加至約-2 dB。大多數無線通信系統在最大功率下都有最嚴格的輻射規格,這一事實加強了這種在對數放大器的最大輸入電平上“后退”的需求。

圖 12: 對數放大器的溫度穩定性

dBV 與分貝

RF系統中使用最廣泛的慣例是以dBm為單位指定功率,即相對于1 mW的分貝。在功率方面對數放大器輸入電平的規范嚴格來說是對流行慣例的讓步;與二極管檢測器一樣,它們不響應功率,而是響應輸入電壓。dBV的使用更正確。但是,由于大多數用戶根據功率指定RF信號 - 更具體地說,相對于50 Ω的dBm - 我們使用dBV和dBm來指定對數放大器的性能,在50 Ω環境的特殊情況下顯示等效dBm電平。

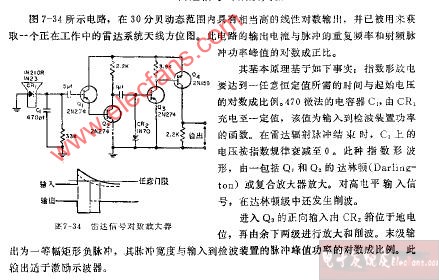

檢測快速射頻脈沖

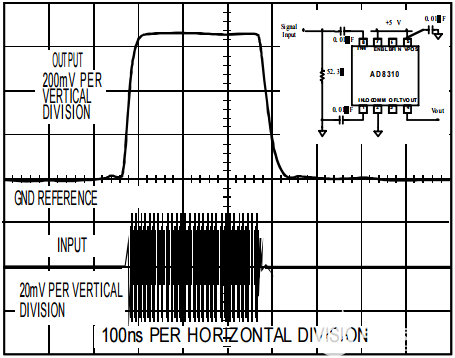

現在考慮如果輸入信號不是連續的,而是脈沖打開和關閉會發生什么。對數放大器輸出對輸入端變化的響應時間將由輸出低通濾波器的RC時間常數決定(再次參見圖9)。AD8310是一款440 MHz、95 dB對數放大器,響應持續時間為13 ns的100 MHz突發(見圖300),10%至90%上升時間(常用的對數放大器響應時間度量)約為15 ns。在實際應用中,這使我們能夠檢測和測量短至約40 ns的RF突發。

圖 13: 對數放大器脈沖響應

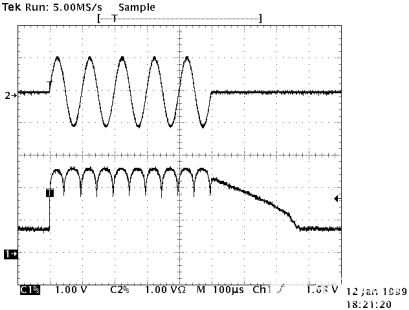

將輸出低通濾波器的帶寬(通常稱為視頻帶寬)設置得非常高將導致頻率接近或低于轉折頻率的輸入信號產生殘余輸出紋波。AD8313對10kHz輸入突發的響應會導致輸出紋波過大(見圖14),因為該器件的轉折頻率在內部設置為13 MHz左右。然而,通過在輸出端增加一個單極點低通濾波器,可以輕松糾正這個問題,而不會造成損失。

圖 14.對數放大器輸出紋波

視頻帶寬和輸入信號帶寬不應混淆。單芯片對數放大器的最大輸入信號帶寬通常在50 MHz至2.5 GHz左右,而這些器件的視頻帶寬通常在1至30 MHz范圍內。

可以看到另一個有趣的效果(再次圖 14);請注意,對數放大器響應的衰減似乎比突發的衰減慢得多。這是一個有趣的效果,它是由正在發生的日志轉換的性質引起的。但請記住,在低輸入電平下,輸入信號的微小變化會對輸出電壓產生重大影響。例如,輸入電平從7 mV到700 μV(或約-30 dBm到-50 dBm)的變化與輸入電平從70 mV到7 mV的變化具有相同的效果。作為對數放大器,這就是您所期望的。但是,如果我們用肉眼觀察輸入信號(即RF突發),我們看不到mV范圍內的微小變化。正在發生的事情(在圖14中)是突發不會立即關閉,而是下降到某個水平,然后呈指數衰減到零。現在,如果您繪制衰減指數信號的對數,您會得到一條類似于圖中尾部的直線。在實驗室。測試對數放大器脈沖響應,提供具有近乎理想衰減的輸入信號是非常具有挑戰性的。一種常見的方法是用來自發生器的脈沖對RF信號進行選通,其中脈沖寬度可以以非常高的分辨率進行調整3.

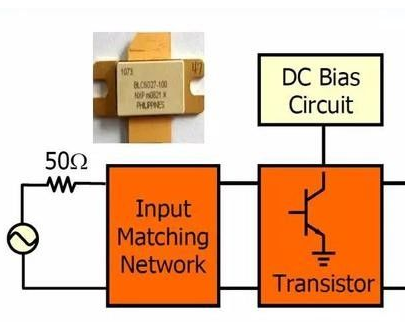

輸入匹配

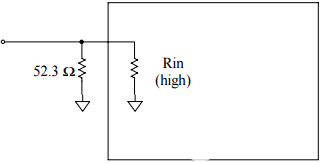

對數放大器的輸入阻抗范圍通常為數百至數千歐姆。雖然無功匹配技術可用于將典型的50 Ω源阻抗轉換為更高的電平,但簡單的電阻分流通常可提供最佳的整體輸入匹配。當對數放大器的輸入阻抗與頻率相關時尤其如此。通常,選擇略大于50 Ω的分流電阻器,該分流電阻器與對數放大器的較高輸入阻抗并聯,總輸入阻抗為50 Ω。

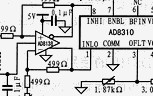

Fig. 15: Log Amp Input Matching

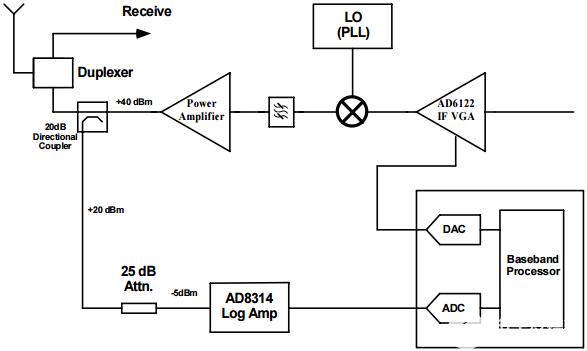

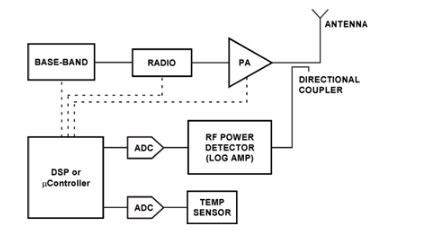

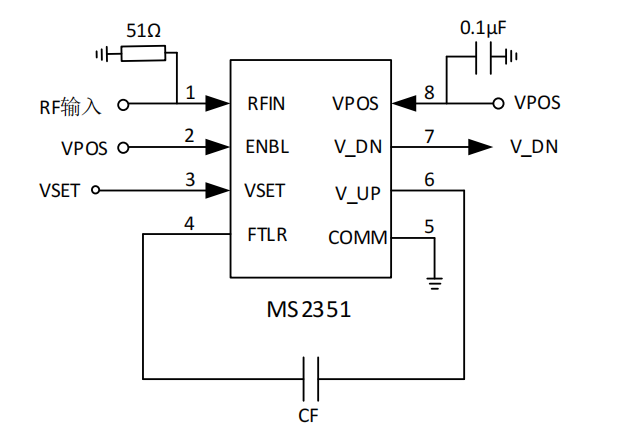

A Typical RF Power Control Loop with Digital Control

A typical RF power control loop which has digital control (Fig. 16) has RF signal from the PA (with a maximum power of +40 dBm) passing through a directional coupler on its way to the antenna. Directional couplers are characterized by their coupling factor which is typically in the 10- to 30-dB range, i.e. the output signal is 10 to 30 dB smaller than the primary output. Because the coupled output must deliver some power (in this case to the detector), the coupling process takes some power from the main output. This manifests itself as insertion loss, which is higher for lower coupling factors.

Fig. 16: Digitally-Controlled RF Transmission System

In the example shown (Fig.16) the coupled output must be attenuated by a further 25 dB before it is applied to the AD8314 log amp (recall from earlier that the AD8314 is very temperature stable for input levels below about -4 dBm.)?

The AD8314's output is digitized in an ADC. For an 8-bit ADC and a detector dynamic range of 40 dB, this results in a resolution of 0.16 dB/code (40dB/28.) This resolution is more than sufficient for most precision applications.?

Once the transmitted power is detected and digitized a DAC is used to adjust the system.?In this case the power is adjusted by changing the gain of a variable gain amplifier (VGA) at IF. This is just one way in which power can be changed with other options including bias adjustment of the PA and variation of the amplitude of the baseband signal.?

The response time of this loop will be dominated by the digital control circuitry. In general the reaction time of the detector and the VGA will be small in comparison to the conversion rates of the ADC and DAC, and the digital processing time.?

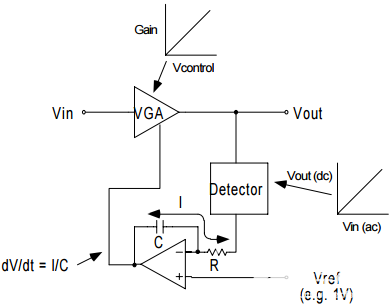

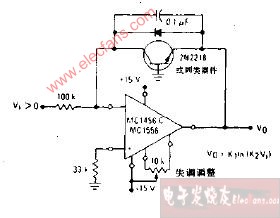

A Typical Analog AGC Loop

Where fast regulation of gain is required the inherent latency of a digitally-controlled AGC loop may not be acceptable. In such situations, an analog AGC loop may be a good alternative.

Beginning at the output of the VGA in a generic version (Fig. 17) this signal is fed, usually via a directional coupler, to a detector. The output of the detector drives the input of an op amp, configured as an integrator. A reference voltage drives the non-inverting input of the op amp, and the output of the op amp integrator drives the gain-control input of the VGA. Now, let's examine how this circuit works.

圖 17: 模擬自動增益控制環路

最初假設VGA的輸出處于某個低電平,積分器上的基準電壓為1 V。低檢波器輸出導致積分器電阻R兩端的壓降。通過該電阻產生的電流只能來自積分器電容器C.沿該方向流動的電流會增加積分器的輸出電壓。驅動VGA的該電壓增加了增益(我們假設VGA的增益控制輸入具有正意義,即增加電壓會增加增益。增益將增加,因此增加放大器的輸出電平,直到檢波器輸出等于1 V。此時,流經電阻/電容的電流將降至零,積分器輸出將保持穩定,從而建立環路。如果電容電荷隨著時間的推移而損失,增益將開始降低。但是,這種泄漏將通過新降低的檢測器電壓的額外積分器電流快速糾正。

該電路的主要用途在于其對VGA增益控制功能變化的抗擾度。至少從靜態角度來看,增益和增益控制電壓之間的關系對整體傳遞函數沒有影響。根據 Vref 的值,積分器將增益控制電壓設置為產生所需輸出電平所需的任何電平。增益控制功能中的任何溫度依賴性都將被消除。此外,VGA增益傳遞函數中的非線性不會出現在整個傳遞函數中(Vout與Vref)。唯一的要求是VGA的增益控制功能是單調的。然而,檢測器的溫度穩定至關重要。

如前所述,該電路設計用于為不同的輸入電平產生恒定的輸出電平。由于這導致恒定的輸出電平,因此很明顯,檢波器不需要寬動態范圍。我們只要求它對于對應于設定值電壓Vref的輸入電平保持溫度穩定。例如,前面討論的二極管檢波器電路在低電平時溫度穩定性較差,但在高電平下穩定性合理,在電平輸出相當高的應用中可能是一個不錯的選擇。

如果我們使用的檢波器具有更高的動態范圍,我們現在可以使用該電路在寬動態范圍內精確設置VGA輸出電平。為此,積分器基準電壓Vref是可變的。Vref上的電壓范圍直接取決于檢波器的傳遞函數。例如,如果檢波器在-0 dBV的輸入電平下提供5.20 V電壓,則當檢波器輸入為-0 dBV時,5.20 V的基準電壓將導致環路建立(VGA輸出將大于VGA和檢波器之間存在的任何耦合因子。

可變Vout情況的動態范圍由環路中具有最小動態范圍(即VGA的增益控制范圍或檢波器的線性動態范圍)的器件決定。同樣,請注意,VGA不需要精確的增益控制功能。在這種情況下,VGA增益控制的動態范圍定義為增益控制電壓增加導致增益增加的范圍。

該環路的響應時間可以通過改變積分器的RC時間常數來控制。將其設置為低電平將導致快速輸出建立,但可能導致輸出包絡振鈴。將RC時間常數設置為高將給予環路良好的穩定性,但會增加建立時間。

值得注意的是,使用術語AGC(自動增益控制)來描述這種電路架構從根本上是不正確的。術語AGC意味著增益是精確設置的。實際上,自動設置的是輸出電平,因此術語ALC(自動電平控制)會更正確。然而,就像冉冉升起的太陽和傳統電流的方向一樣,這個術語在流行術語中根深蒂固,因此試圖糾正這種不準確性毫無意義。

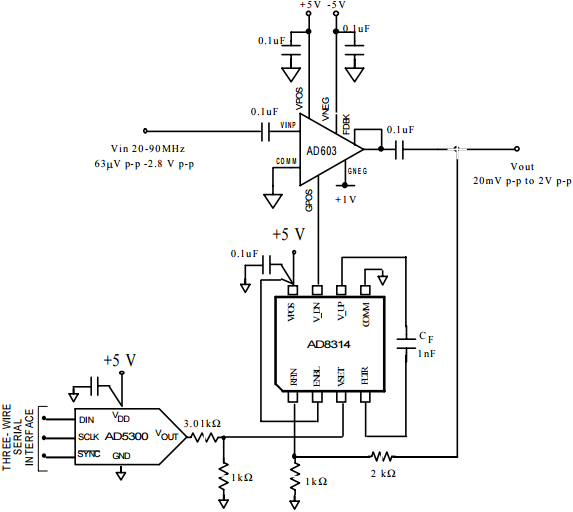

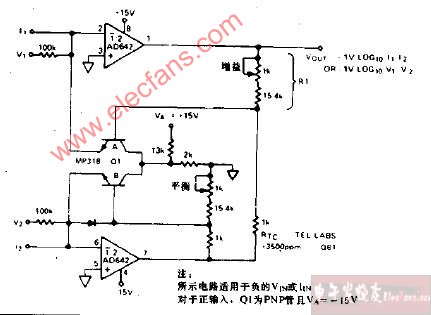

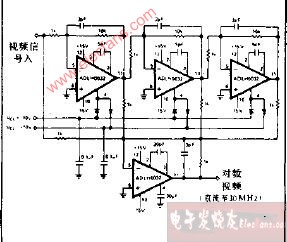

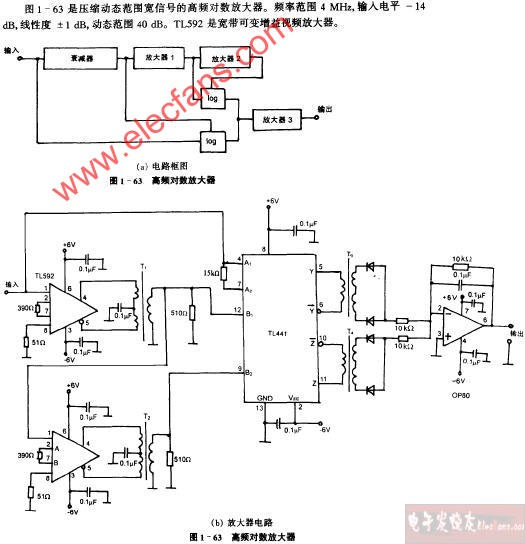

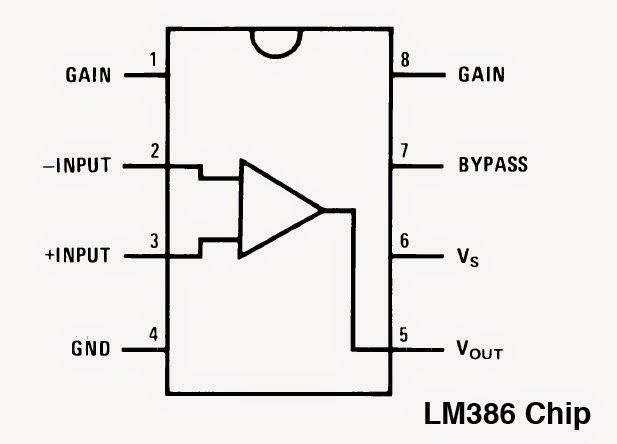

實用的模擬AGC環路

在實際的AGC環路(圖18)中,AD603(一款工作頻率高達90 MHz的通用VGA)的輸出電平由對數放大器AD8314控制;基準電壓由5300位DACAD8設置。除了用作檢波器外,AD8314還集成了完成環路所需的積分器。我們將探測器的這種工作模式稱為控制器模式。

圖 18: 實用的模擬AGC環路

AD603可提供2 Vpk-pk的最大輸出電壓。為了將此最大電平映射到AD8314的最大輸入電平,需要0.33的衰減因子(此處使用簡單的電阻分壓器實現)。DAC的滿量程輸出電壓5 V同樣按比例縮小,以對應于AD8314的基準電壓范圍(0 V至1.25 V)。這不是絕對必要的,因為我們可以只使用那些與對數放大器的參考電壓范圍相對應的DAC代碼。但是,以這種方式調整DAC電壓會使控制分辨率(以dB/代碼為單位)提高4倍。

如前所述,該電路可用于兩種不同的AGC模式。作為電平電路,可能為了向ADC提供恒定的輸入幅度,設定點電壓將保持恒定。或者,在VGA輸入電平相當恒定的發射應用中,將調整設定點電壓以將輸出信號幅度改變多達45 dB。

本系列的第三部分將討論對數放大器對不同信號類型的響應,以及均方根直流轉換器的使用。

電子發燒友App

電子發燒友App

評論