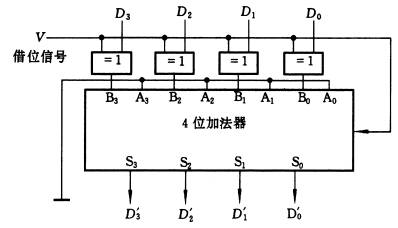

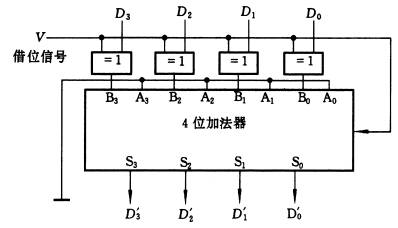

多位二進制減法器,是由加法電路構成的;在加法電路的基礎上,減法與加法采用同一套電路,實現加減法共用。

2020-09-01 16:02:09 20232

20232

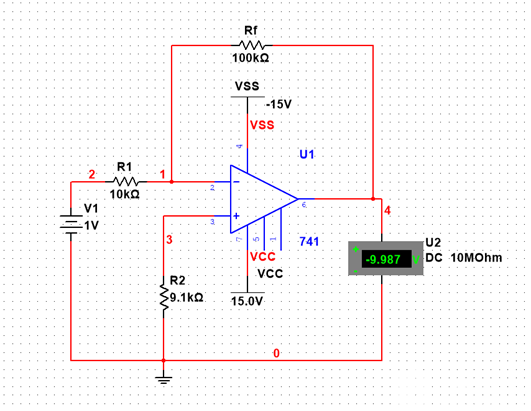

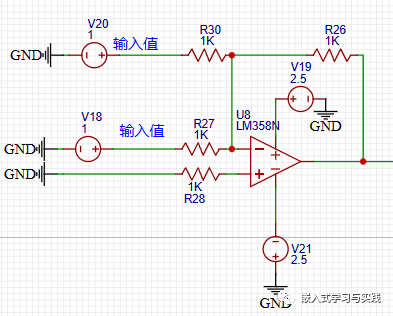

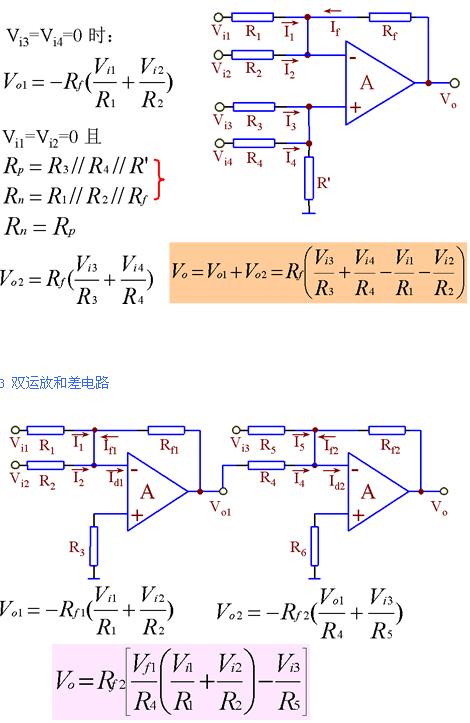

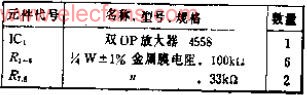

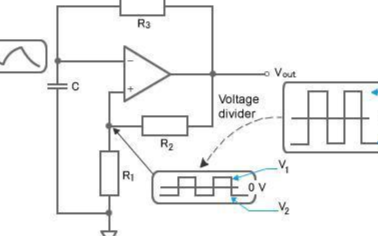

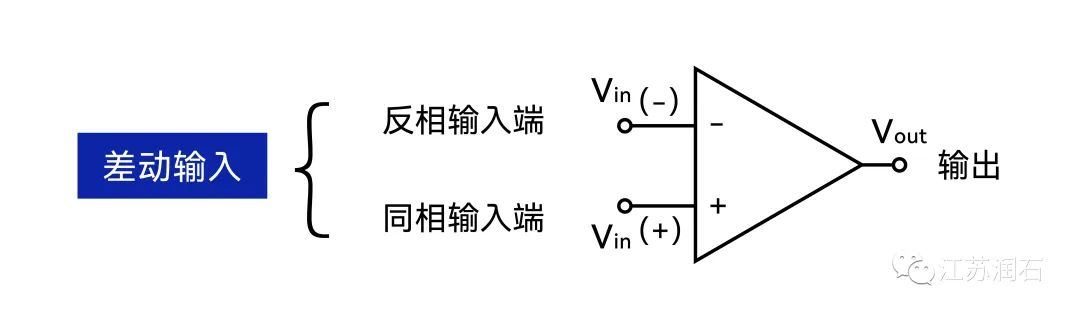

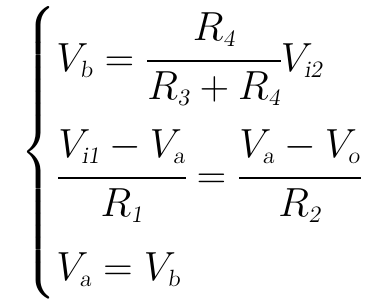

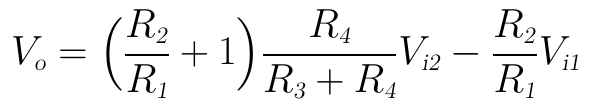

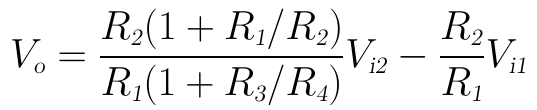

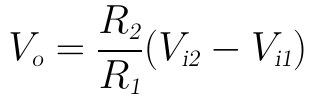

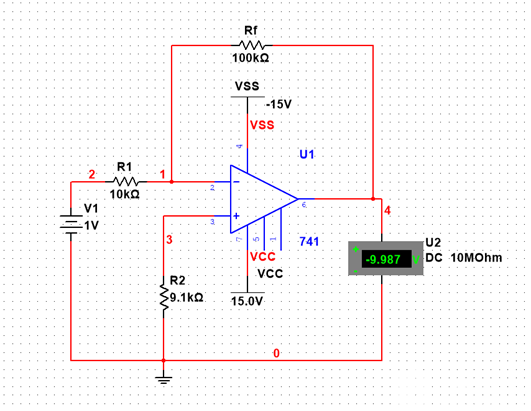

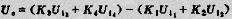

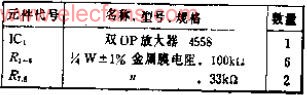

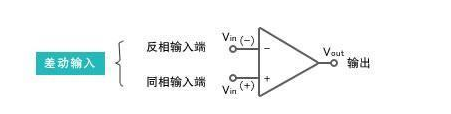

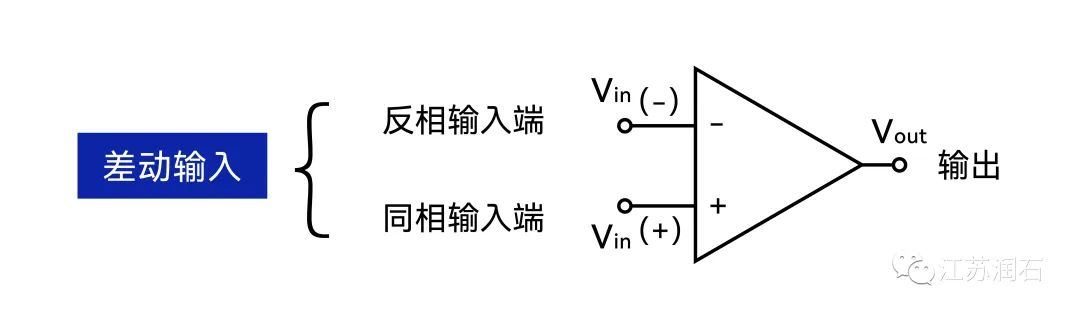

????? 集成運放在負反饋情況下工作在線性區,可以構成比例、求和、減法、加減法運算等等多種類型的算術運算電路。下面對單運放構成的反相比例、同相比例和加減法運算電路進行分析,由此導出單運放構成

2023-02-08 11:37:16 2522

2522

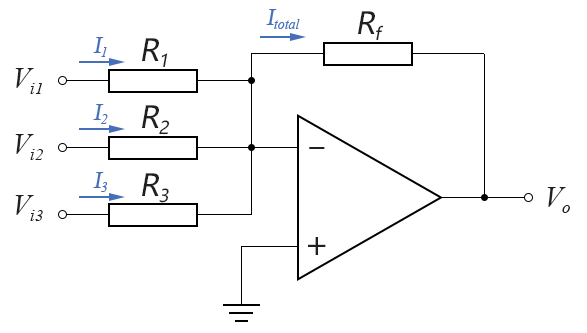

可看出輸出值與輸入值的和成反比關系,所以叫反相加法運算電路。

2023-08-08 15:41:56 3817

3817

減法器是一種電路,它可以實現二進制數字的減法運算。減法器的工作原理基于位運算和進位/借位機制。

2024-02-19 09:36:37 561

561

74ls192加減法無法正常工作此處有個圖這個是仿真圖這個是功能表。最開始的時候,我們將CPU端口接了一個高電平脈沖,CPD口接上了一個開關,置低電平。給CPU口一個高電平脈沖之后,無法正常計數

2021-12-07 08:11:15

接地,輸出才是0但是現在我想的是能夠做成一個減法運算放大電路,使得我的傳感器的輸出2.1~2.7V經過運放后 轉換為0~3.3V 的然后給我的單片機經行AD轉換大家有誰給我一個方案?或者是其他的運放也行

2015-04-25 21:35:50

這一點。3、使用運放時需要注意由電阻自身雜散電容而產生的影響這個反向比例運算電路的增益函數如下:這里,C1會使得頻率特性出現尖峰脈沖,而C2會使得高頻領域的增益下降,從而導致頻率特性惡化!對于一般的低頻

2018-10-24 16:10:37

: 41MHz;輸出電流: 最小 50mA;低失真: ? 76dB(1MHz);運放參數的理解1.運放壓擺率>多少屬于高速運放?2.輸入偏置電流、輸出電流、電流噪聲、電壓噪聲小于多少屬于是低溫漂、低失調的運放

2022-09-09 19:20:46

1、運放可以當比較器用,比較器不可當運放用

2、運放為推挽輸出,比較器為開集輸出,需接上來電阻

3、運放的電平翻轉速度比比較器要慢

2023-05-23 23:12:42

能夠處理交流信號的能力三、運放關于帶寬和增益的主要指標以及定義四、運算放大器的性能指標五、運算放大器的動態技術指標六、運放的主要參數介紹

2021-03-06 14:59:24

` 本帖最后由 gk320830 于 2015-3-4 16:17 編輯

從ti官網下載下來的關于運放的手冊第二部分:運算放大器噪聲介紹第三部分:電阻噪聲與計算示例附錄3.4:簡單運算放大器電路的電流噪聲計算方程式`

2013-05-28 20:42:23

運放的開環直流增益如何用DC仿真得出?有些人用DC怎么得出增益不太清楚?DC掃描正端,輸出不是跟隨輸入電壓?這怎么得到增益?輸入輸出電壓關系曲線是輸出除以輸入?

2021-06-24 07:37:37

`運算放大器分類 、作用及運放的選型,詳細解析了運算放大器的特點、工藝、功能、性能、參數、指標和運算放大器的對信號放大的影響和運放的選型舉例,并附有常見運算放大器列表!1. 模擬運放的分類及特點

2013-05-16 21:35:50

用霍爾傳感器把電流轉換成電壓,想用LM358把信號放大讓32芯片讀ADC,但不知道該如何用這個運放的放大倍數是多少,該如何用它?

2018-01-27 16:49:01

請教大家怎么用VHDL語言實現減法運算?在FPGA設計時又該怎么操作呢?

2012-05-17 20:07:12

需要Verilog語言,1.4.15位二進制加減法器代碼急用謝謝:)

2011-04-03 22:10:37

還需要這個來支持。另外,正反饋的閉環,更容易實現振蕩,產生振蕩波形,這也是很多時鐘的基礎。虛短和虛斷由于運放的電壓放大倍數很大,一般通用型運算放大器的開環電壓放大倍數都在80 dB以上。而運放的輸出

2019-07-04 14:58:06

20以內加減法訓練機基于單片機實現 20 以內整數加減法訓練,要求具有加法、減法(結果不出現負數)、加減法三種訓練模式,每次訓練隨機產生題目。可以選擇每次訓練題目的數目,可分為每組 5 題、10 題

2021-07-15 07:51:35

本帖最后由 liuliwei25 于 2016-1-28 14:44 編輯

請問labview如何實現加減乘除的混合運算,如圖所示。謝謝

2016-01-28 14:29:47

求,verilog語言1,4,15 位二進制加減法器設計的代碼急用,謝謝:)

2011-04-03 21:52:44

上圖是運放搭建的恒流電路,和上期講的一樣,實現1mA的恒流源。他的工作原理主要通過運放的電壓跟隨電路和三極管的射級跟隨電路。假設這里使用的U1A運放放大倍數是10萬倍,三極管的放大倍數是β=100

2021-11-08 16:15:56

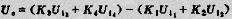

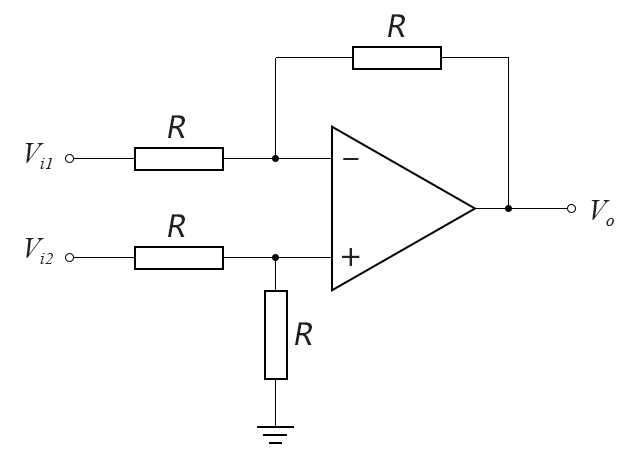

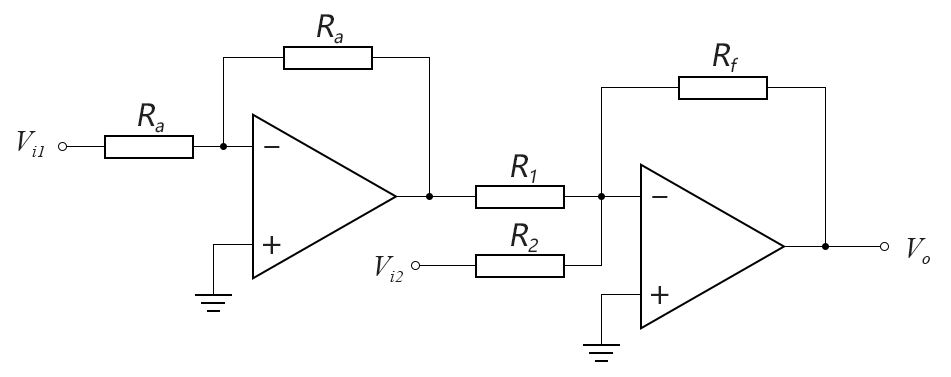

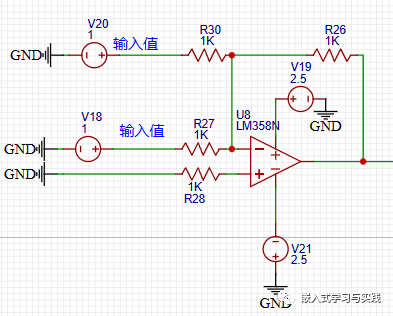

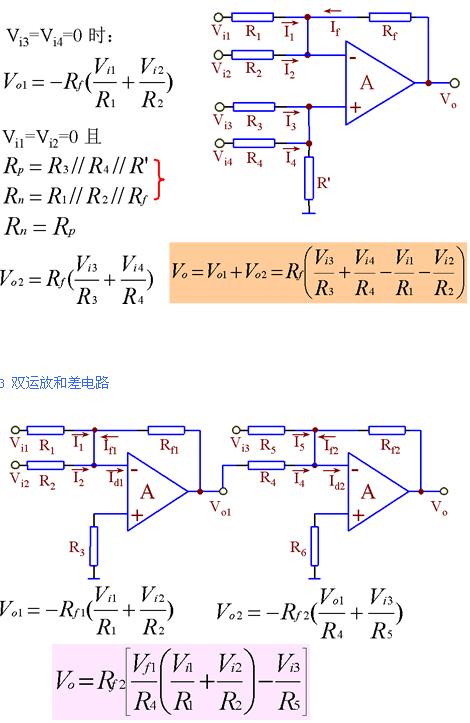

、虛斷2、單運放和差電路3、雙運放和差電路例1:設計一加減運算電路設計一加減運算電路,使 Vo=2Vi1+5Vi2-10Vi3解:用雙運放實現如果選R[sub]f1[/sub]=R[sub]f2

2021-09-10 15:19:42

想給一個橋式傳感器(就是應變片貼的橋式電路)的差分信號做一個單端輸出的放大器,橋式傳感器輸出0-20mV,本來我直接想用儀表運放AD620,但是我發現有些人會使用OP413(四運放)直接搭一個減法電路,我想問的就是這兩種方式主要的區別在哪里,這樣搭出來的電路的性能的差異主要體現在什么方面

2018-09-26 17:09:24

求指教,用VHDL語言,設計實現一個十進制雙向加減法器,要求有一個加信號add,有一個減信號***

2012-06-08 20:44:46

如視頻所示,該電路是一個高端電流檢測電路,用來檢測電池的輸出電流大小,檢測電壓為12v。該運放供電為14v單電源供電,運放型號為opa4188運放,現在的問題是,空載狀態下,電流檢測電阻壓差為0v

2022-04-22 11:02:40

(1)分析分析:單電源運放和單電源運放1.1 電源供電和單電源供電所有的運算放大器都有兩個電源引腳,一般在資料中,它們的標識是VCC+和VCC-,但是有些時候它們的標識是VCC+和GND。這是因為有些數據手冊的作者企圖將這種標識的差異作為單電源運放和雙電源運放的區別。但...

2021-11-11 06:07:27

聽別人說,單電源的運放,在做減法器的時候,結果是沒法出現負電的,是真的嗎?哪位指導一下單電源與雙電源的區別。

2017-02-15 10:20:34

下圖哪一個電路是減法器?按照書上的電路,減法器應該構成負反饋,可是把運放接成正反饋之后,輸出卻沒有變化,那么負反饋或者正反饋在電路中的作用是什么呢?問題來自論壇里的這個電路,看到構成的是正反饋

2017-08-31 19:46:42

求一份關于數電的四位十進制的加減法計數器!!!感謝各路大神!!!

2016-03-10 13:28:19

C語言中開平方的算法中要開平方的話,可以在頭文件中加#include .然后調sqrt(n);函數即可.但在單片機中要開平方.可以用到下面算法:算法1:本算法只采用移位、加減法、判斷和循環實現,因為

2021-07-15 07:03:45

目04_02有符號小數加減法練習講解05 有符號小數乘法運算05_01有符號小數乘法運算練習題目05_02有符號小數乘法運算習題講解[/td]使用ROM實現模塊劃分使用ROM實現工程解讀使用ROM實現工程仿真

2018-08-09 21:32:52

基于單片機如何去實現20以內整數加減法訓練呢?有哪些具體要求以及操作步驟呢?

2021-11-02 07:00:25

數字增益控制電路的原理是什么如何用CPLD器件實現DAGC運算?數控衰減器在中頻電路中引入的沖擊振蕩問題數控衰減器的實現方法

2021-04-08 06:02:44

如何用單片機方波實現到運放后輸出正弦波?我這邊單片機是方波占空比和頻率可調,然后我想輸送到運放那里,希望運放可以直接輸出正弦波。有沒有對應的IC?

2017-12-03 09:09:07

如何用頂級功率型運放制作耳放?

2021-06-02 06:00:51

模電 利用單運放或雙運放設計加減電路 U0=10U1+20U2+15U3-4U4-5U5

2023-03-17 10:05:12

需要先來透測的學習運放電路的內部結構和原理,對于我們來說運算放大器是模擬電路中十分重要的元件,它能組成放大、加法、減法、轉換等各種電路,我們可以運用運放的“虛短”和“虛斷”來分析電路,然后應用歐姆定律

2019-01-19 17:57:48

有效地址是什么?形式地址又是什么?有何區別?補碼加減法是指什么?

2021-07-16 11:33:33

本帖最后由 gk320830 于 2015-3-5 23:24 編輯

急求。。。。。運放實現:U。=-(4U1+2U2+0.5U3)的運算電路圖,,,要求表上數值,仿真電路圖

2012-05-09 14:13:40

Verilog語言代碼1,4,15 位二進制加減法器代碼,謝謝,急用:)

2011-04-03 22:03:49

請用2個集成運放設計電路完成運算:(公式如圖)已知電容C取0.1μF(也可以自定),加減運算電路中Rf=10kΩ(也可以自定)。

2020-06-29 13:19:59

周期嗎?3.FPGA做加減法之類的運算時間要耗費多少時鐘周期?比如我定義輸入變量A、B、C、D都是8位,輸出變量E是16位,使E的前八位存入A+B,后八位存入C+D,那么從輸入到輸出需要多少個時鐘周期?謝謝!

2015-05-11 19:17:21

關于用multisim12.0軟件,將一個4-20mA的電流通過運放產生一個0-5V電壓的一個過程。通過分析可知,4-20mA的電流不能通過單一的放大電路或者加減法電路直接得到0-5V電壓。但是可以

2019-09-23 16:02:40

有一個電流,用電流傳感器實時采樣得到的對應轉換電壓范圍為2.5~3.2V,但是我現在想得到的輸出信號為0 ~ 1.4V,所以用了如圖這個減法電路,請大家看看是否可行?此外,假如可行的話用這個運放是否

2019-01-16 16:44:26

`一個關于減法器的困惑。如圖,(Ui2-Ui1)*Rf/R1=Uo是這個負反饋減法器的性質。如果運放的電源我接的是Vcc和地,而不是+Vcc以及-Vcc;而且假設Ui1=1/2Vcc, Ui2

2012-06-27 16:50:00

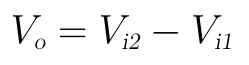

如圖所示是一個用運放實現減法電路,小弟是運放菜鳥。最近在學習運放相關知識。請教各位大俠如圖中Uo=Ui1-Ui2的詳細推導。謝謝了!

2015-06-02 14:51:27

FPGA如何實現32位減法運算

2019-02-28 04:59:09

hValue = (u16)(-Theta);hValue = 0x166-hValue;//我想在這一步實現減法運算,但是使用ST-link 進行仿真的時候發現,hValue 的值并沒有發生變化?請教大家一下,在STM32中,如何實現減法運算呢?

2019-01-17 01:04:46

請問如何用運放使0-10v的方波電壓信號轉換為+-5v輸出,運放如何選擇

2022-02-26 15:25:19

請問如何用運放搭電路將單極性正弦波轉換成雙極性的正弦波?

2017-03-26 10:16:55

8位單片機能夠實現超長數計算嗎?我說:"只要存儲器夠大,按照下面的方法設計的加減法運算器及指令,就能夠編寫程序完成。"1。用全加器搭建一個8位加法器;2。將最低下進位前連接一個1位寄存器,輸入端連接

2014-09-22 03:09:55

數據手冊進合適的電阻選擇就可以完成運放調零。 另外一些低成本的運放或許不帶這些自動調節功能,那么作為設計師的我們也不為難,通過簡單的加法電路、減法電路等可以完成固定的調零(雖然有時這種做法有隔靴撓癢

2018-12-27 09:24:29

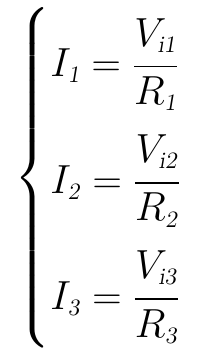

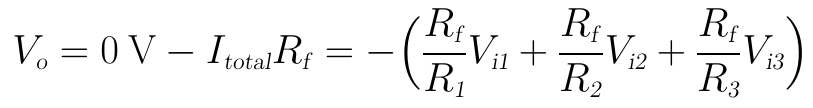

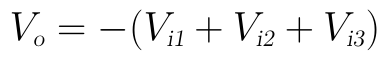

加減運算電路

求和電路

1. 反相求和電路

虛短、虛斷

2008-01-18 09:34:40 9699

9699

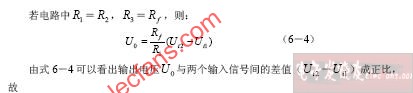

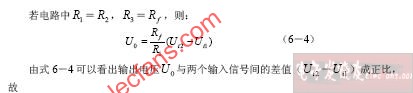

減法運算電路

圖6-4 減法運算電路

2009-03-09 10:11:43 5254

5254

減法運算

同加法運算一樣,減法運算可采用減法器來實現。半減器和全減器的設計方法和步驟與設計加法器相同。實用上,為了簡化系統結構,通常不另外設計減

2009-04-07 10:38:39 12841

12841

實現補碼加減運算的邏輯電路

運算前,X、Y寄存器分別存儲被加(減)數 和 加(減)數,計算結果存回X寄存器;F為加法器,能在命令X→F和Y→F信

2009-10-13 22:44:55 9696

9696

補碼加、減運算規則

在計算機中,通常總是用補碼完成算術的加減法運算。其規則是: [X+Y]補= [X]補 + [Y]補 ,[X-Y]

2009-10-13 22:46:58 10314

10314

補碼減法,補碼減法原理是什么? 負數的減法運算也要設法化為加法來做,其所以使用這種方法而不使用直接減法,是因為它可以和常規的加法運算使用同一

2010-04-13 11:45:46 6326

6326 浮點運算與浮點運算器

浮點加減法的運算步驟 設兩個浮點數 X=Mx※2Ex Y=My※2Ey 實現X±Y要用如下5步完成: ①對階操作:小階

2010-04-15 13:42:32 6497

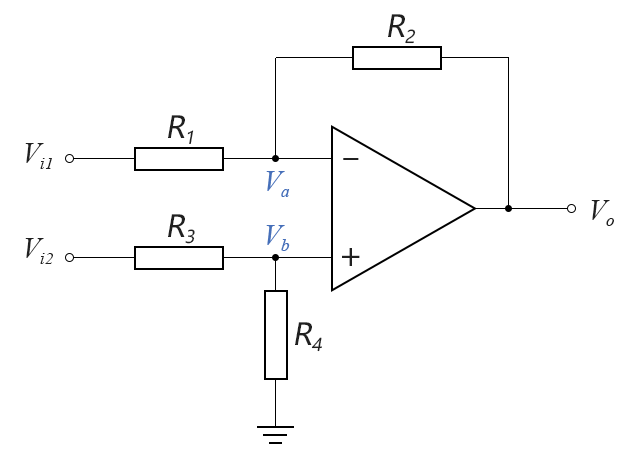

6497 加減法電路

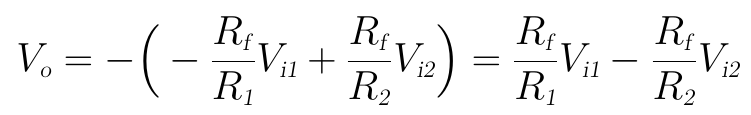

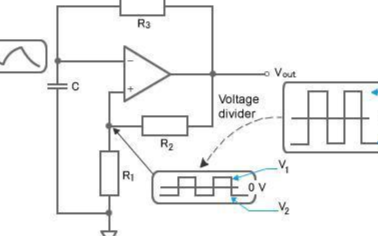

利用一個差動輸入的運放就可同時實現加減法運算,這種運算電路如圖5.4-3所示。

2010-04-22 17:50:08 9986

9986

由輸入端選擇運算方式的加、減法運算電路

電路的功能

這是一種配

2010-05-08 11:32:23 1518

1518

該ALU采取層次化設計方法,由控制模塊、邏輯模塊、加減法模塊、乘法模塊和除法模塊組成,能實現32位有符號數和無符號數的加減乘除運算,另外還能實現9種邏輯運算、6種移位運算以

2012-02-09 15:24:55 80

80 信號處理電路的基本設計方法。加減法電路,除法電路等等

2015-12-30 15:51:47 0

0 C語言教程之整數加減法練習,很好的C語言資料,快來學習吧。

2016-04-22 17:45:55 0

0 國內手機市場格局已經逐漸變成T型,國內手機廠商會加快出海步伐,OPPO也計劃2018年進行大規模出海行動。面對明年的全面屏和人工智能熱點,OPPO手機實行了線下加減法策略。

2017-12-29 11:27:53 757

757 本文是基于FPGA實現Cordic算法的設計與驗證,使用Verilog HDL設計,初步可實現正弦、余弦、反正切函數的實現。將復雜的運算轉化成FPGA擅長的加減法和乘法,而乘法運算可以用移位運算代替

2018-07-03 10:18:00 2349

2349

4.1.3加法和減法運算電路

2019-04-18 06:03:00 15195

15195

擺脫線制滿載能量,親自體驗南卡N2耳機的加減法則

2019-06-16 10:06:10 24093

24093 運算放大器是一種可以進行數學運算的放大電路。運算放大器不僅可以通過增大或減小模擬輸入信號來實 現放大,還可以進行加減法以及微積分等運算。所以,運算放大器是一種用途廣泛,又便于使用的集成電路。

2019-06-23 11:15:15 6538

6538

LED驅動電源作為LED產業鏈中不可或缺的一環,自然也難逃波及。數據顯示,2020年第一季度6家LED電源上市公司營業收入全部呈下滑趨勢,而凈利潤也僅茂碩電源、可立克2家企業實現增長。

2020-07-13 14:40:44 2228

2228 進制也就是進位制。進行加法運算時逢X進一(滿X進一),進行減法運算時借一當X,這就是X進制,這種進制也就包含X個數字,基數為X。十進制有 0~9 共10個數字,基數為10,在加減法運算中,逢十進一,借一當十。

2020-08-05 10:39:33 4344

4344

作者:OpenSLee 1、float IP的創建 搜索float雙擊Floating-point 1 Operation Selection 我們這里選擇浮點數的加減法驗證

2020-11-13 11:06:53 3731

3731

運算放大器是一種可以進行數學運算的放大電路。運算放大器不僅可以通過增大或減小模擬輸入信號來實 現放大,還可以進行加減法以及微積分等運算。所以,運算放大器是一種用途廣泛,又便于使用的集成電路。

2021-01-01 18:10:00 32548

32548

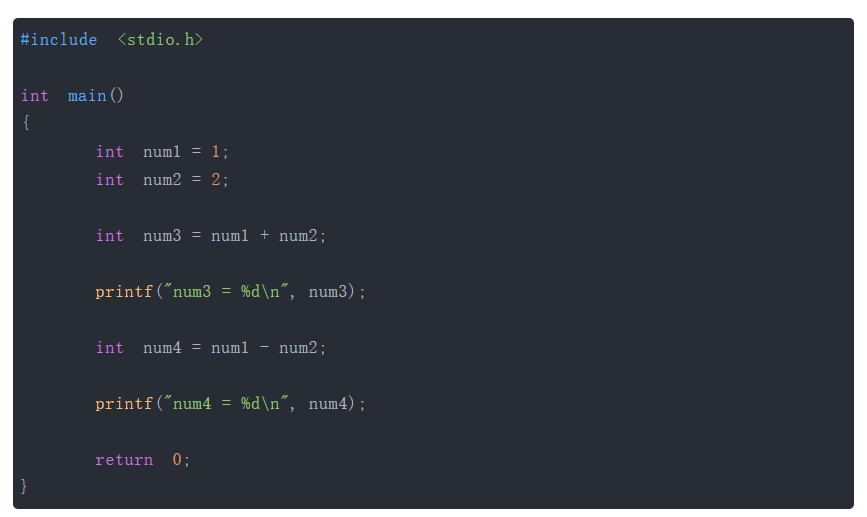

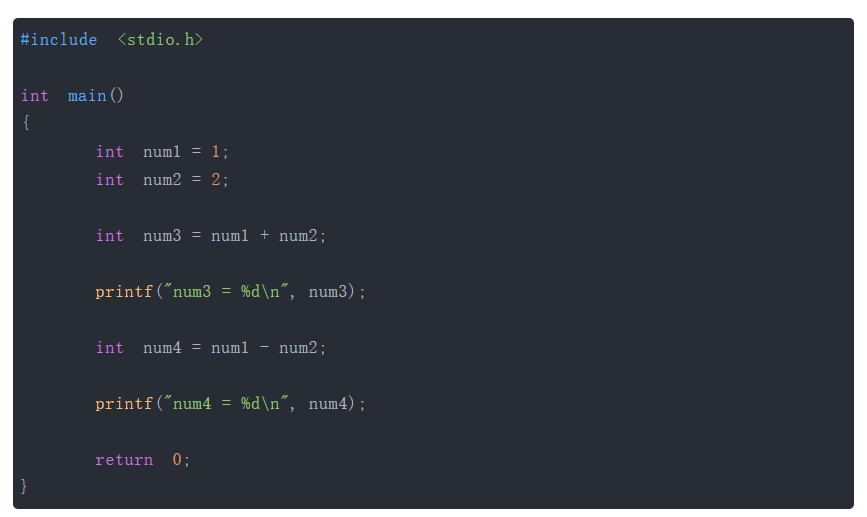

我們先看一段代碼演示加減法的使用。

2021-06-21 16:06:03 2314

2314

編程題目:用ARM匯編實現計算a+b-c的值,其中a=0x30000004F000000F;b=0x0000001110000009;c=0x03.結果存放到R0R1中。(R0保存結果

2021-10-21 10:36:02 2

2 20以內加減法訓練機基于單片機實現 20 以內整數加減法訓練,要求具有加法、減法(結果不出現負數)、加減法三種訓練模式,每次訓練隨機產生題目。可以選擇每次訓練題目的數目,可分為每組 5 題、10

2021-11-15 14:36:06 4

4 基于multisim的加減運算器

2022-06-09 14:38:55 0

0 運算放大器是一種可以進行數學運算的放大電路。運算放大器不僅可以通過增大或減小模擬輸入信號來實 現放大,還可以進行加減法以及微積分等運算。所以,運算放大器是一種用途廣泛,又便于使用的集成電路。

2023-04-24 14:57:58 4229

4229

運算放大器是一種可以進行數學運算的放大電路。運算放大器不僅可以通過增大或減小模擬輸入信號來實 現放大,還可以進行加減法以及微積分等運算。所以,運算放大器是一種用途廣泛,又便于使用的集成電路。

2023-04-24 15:05:39 1369

1369

本文是本系列的第二篇,本文主要介紹FPGA常用運算模塊-加減法器和乘法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:13:57 2625

2625

加、減 使用補碼時,加減法可以統一,因而對加減不加區分,對有無符號也不加以區分。

2023-06-06 17:07:59 685

685

FPGA實現加法和減法運算非常簡單,實現乘法和除法可以用IP,那實現對數和指數運算該用什么呢?

2023-08-05 09:37:05 810

810

CodeBlocks是一種常見的集成開發環境(IDE),用于編寫、運行和調試各種編程語言的程序。在本文中,我們將探索如何使用CodeBlocks進行加減法編程。我們將詳細介紹CodeBlocks

2023-11-26 09:27:41 370

370 異或門可以用于實現二進制數的加減法。例如,我們可以使用異或門來實現兩個二進制數的加法,如果兩個相應的輸入端上輸入的數相同時則進行減法運算。

2024-02-04 14:47:09 740

740

電子發燒友App

電子發燒友App

評論