今天給大家分享的是:集電極開路電路、集電極開路晶體管電路、集電極開路工作原理、集電極開路TTL、集電極開路輸出接線圖、集電極開路優(yōu)缺點(diǎn)。

在數(shù)字芯片設(shè)計(jì)、微控制器應(yīng)用和運(yùn)算放大器中,集電極開始輸出通常用于驅(qū)動(dòng)繼電器等高負(fù)載或用于連接其他電路。

眾所周知,BJT是一個(gè)晶體管,有三個(gè)端子(發(fā)射極、基極和集電極),這些端子主要可以配置三種開關(guān)模式:共基極、共集電極和共發(fā)射極。

這篇文章主要是關(guān)于集電極開路電路的相關(guān)知識(shí)。

一、集電極開路是什么意思?

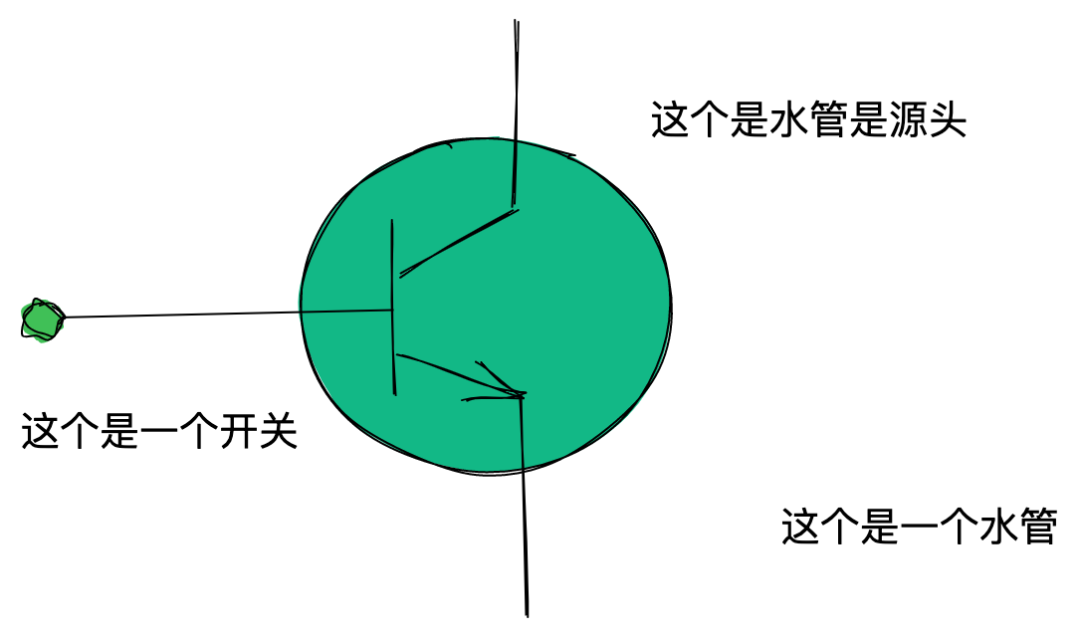

集電極開路是各種集成電路中常見的輸出。 集電極開路就像一個(gè)接地或斷開的開關(guān)。 除了將IC或任何其他晶體管的輸出連接到特定設(shè)備外,還連接到NPN晶體管的集電極開路的基極端子,NPN晶體管的發(fā)射極端子與接地引腳內(nèi)部連接。

因此集電極開路的輸出視為NPN晶體管,它允許電流吸收到公共端。 對(duì)于這樣集電極開路電路,必須有一個(gè)電源才能使輸出正常工作。 當(dāng)我們要求未連接任何電源時(shí)計(jì)算輸出電壓時(shí),電壓不會(huì)發(fā)生變化。 必須計(jì)算輸出端的電壓以了解集電極開路電路的正常運(yùn)行。

該電路可以根據(jù)晶體管的類型(NPN或者PNP)提供灌電流或拉電流輸出。

1、當(dāng) NPN 晶體管工作在“高”狀態(tài)時(shí),它向地提供灌電流; 在“低”狀態(tài)時(shí),輸出端將浮動(dòng),直到它通過上拉電阻連接到正電源電壓。

2、當(dāng) PNP 晶體管工作在“高”狀態(tài)時(shí),它向地提供源電流; 在“低”狀態(tài)時(shí),輸出端將浮動(dòng),直到使用下拉電阻連接到地。

下圖是集電極開路邏輯圖。

集電極開路邏輯

二、集電極開路晶體管電路

1、NPN 集電極開路輸出

當(dāng) NPN 雙極晶體管在集電極開路(OC 或 o/c)配置下運(yùn)行時(shí),它在完全開啟或完全關(guān)閉之間運(yùn)行,因此充當(dāng)電子固態(tài)開關(guān)。

也就是說,在沒有施加基極偏置電壓的情況下,晶體管將完全關(guān)斷,而當(dāng)施加合適的基極偏置電壓時(shí),晶體管將完全導(dǎo)通。 因此,當(dāng)晶體管在其截止區(qū) (OFF) 和飽和區(qū) (ON) 之間運(yùn)行時(shí),它不會(huì)像在其有源區(qū)受控時(shí)那樣作為放大器件運(yùn)行。

晶體管在截止和飽和之間的切換允許集電極開路輸出驅(qū)動(dòng)外部連接負(fù)載的能力,這些負(fù)載需要比以前的共發(fā)射極配置所允許的更高的電壓和/或電流。 唯一的限制是實(shí)際開關(guān)晶體管的最大允許電壓和/或電流值。

那么集電極開路輸出的優(yōu)點(diǎn)是,任何輸出開關(guān)電壓都可以通過像以前一樣將集電極端子上拉到單個(gè)正電源,或者通過單獨(dú)的電源軌為負(fù)載供電來簡(jiǎn)單地獲得。 例如,想要驅(qū)動(dòng)需要從 +5 伏邏輯門或 Arduino、Raspberry-Pi 輸出引腳的輸出提供 +12 伏電源的低電流燈或繼電器。

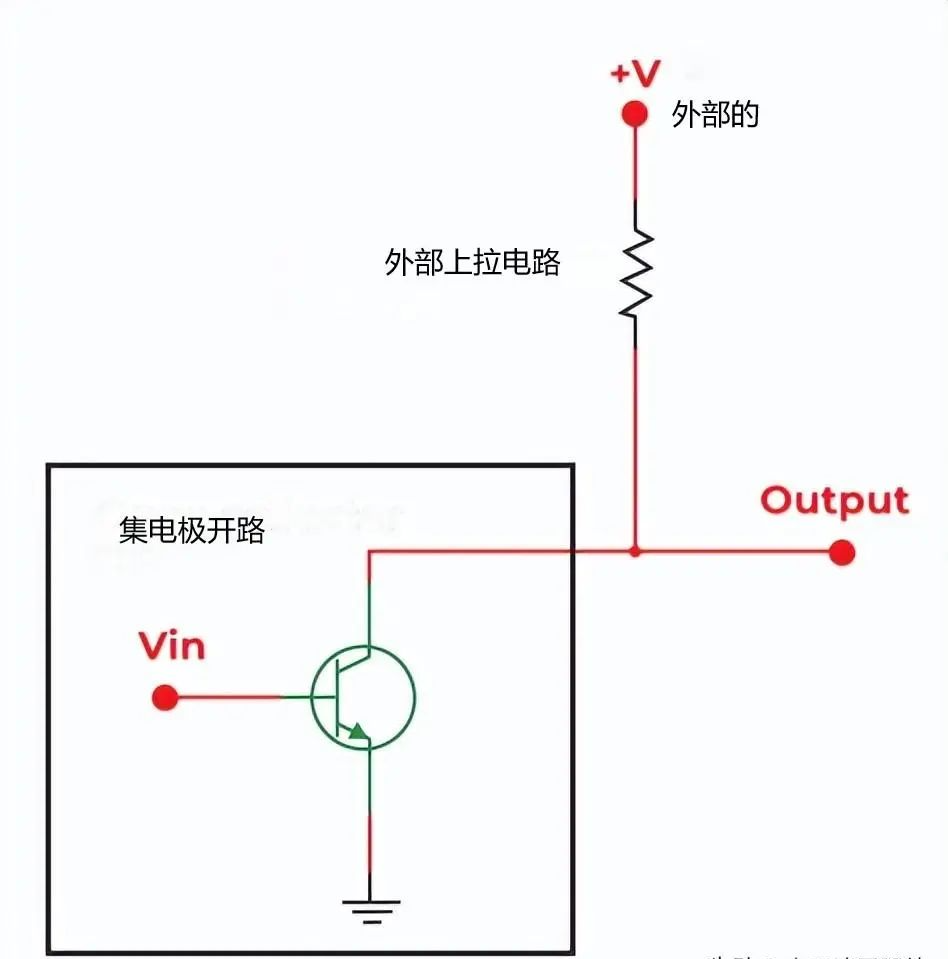

但其缺點(diǎn)是,當(dāng)使用集電極開路輸出來切換數(shù)字信號(hào)、門電路或電子電路的輸入端時(shí),由于三極管的集電極端沒有輸出驅(qū)動(dòng)能力,一般需要外接上拉電阻。 這是因?yàn)閷?duì)于 NPN 晶體管,它只能在通電時(shí)將輸出拉低至地 (0V),而在處于關(guān)斷狀態(tài)時(shí)無法返回或?qū)⑵湓俅瓮苹馗唠娖健?/p>

當(dāng)斷電時(shí),必須使用連接在其集電極端子和電源電壓之間的外部“上拉電阻”將輸出再次拉高,以阻止集電極開路端子在高電平 (+V) 和低電平之間浮動(dòng) ( 0V) 當(dāng)晶體管關(guān)閉時(shí)。

此上拉電阻的值并不重要,在某種程度上取決于輸出端所需的負(fù)載電流值,電阻值的范圍通常為幾百到幾千歐姆。 因此,對(duì)于 NPN 雙極晶體管,其集電極開路輸出僅為電流吸收輸出。

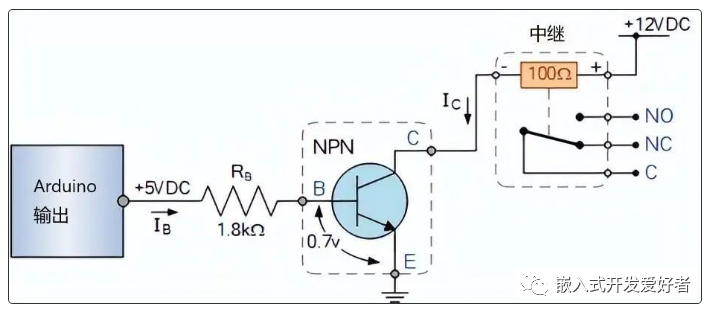

下面為集電極開路晶體管電路。

集電極開路開關(guān)電路

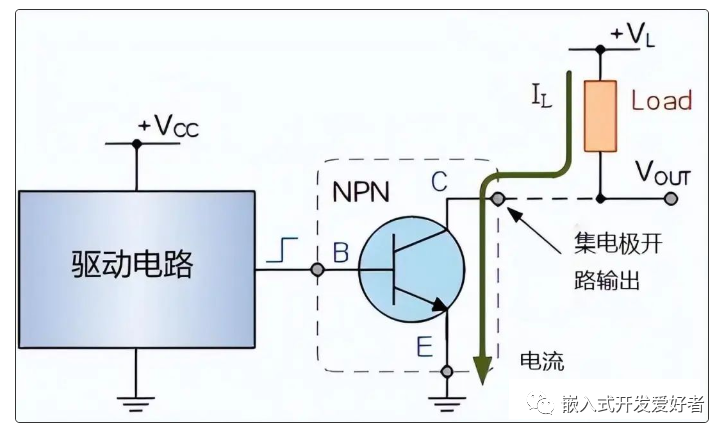

上圖顯示了集電極開路開關(guān)電路的典型布置,該電路可用于驅(qū)動(dòng)機(jī)電型設(shè)備以及許多其他開關(guān)應(yīng)用。 NPN晶體管基極驅(qū)動(dòng)電路可以是任何合適的模擬或數(shù)字電路。 晶體管的集電極連接到要切換的負(fù)載,晶體管的發(fā)射極端子直接接地。

對(duì)于 NPN 型集電極開路輸出,當(dāng)控制信號(hào)施加到晶體管的基極時(shí),它會(huì)導(dǎo)通,并且連接到集電極端子的輸出通過現(xiàn)在導(dǎo)通的晶體管結(jié)點(diǎn)被下拉到地電位連接的負(fù)載并將其打開。 因此,晶體管開關(guān)并傳遞負(fù)載電流 I L,其使用歐姆定律確定為:

?

?

負(fù)載電流,Iload= 負(fù)載電壓 / 負(fù)載電阻

當(dāng)晶體管正基極驅(qū)動(dòng)被移除(關(guān)閉)時(shí),NPN 晶體管停止導(dǎo)通,負(fù)載(可能是繼電器線圈、螺線管、小型直流電機(jī)、燈等)斷電并關(guān)閉。 然后輸出晶體管可用于控制外部連接的負(fù)載,因?yàn)?NPN 晶體管集電極開路的電流吸收開關(guān)動(dòng)作可作為開路 (OFF) 或短路 (ON)。

這里的優(yōu)點(diǎn)是集電極負(fù)載不需要連接到與晶體管驅(qū)動(dòng)電路相同的電壓電位,因?yàn)樗梢允褂幂^低或較高的電壓電位,例如 12 伏或 30 伏直流電。

同樣簡(jiǎn)單的數(shù)字或模擬電路也可用于通過簡(jiǎn)單地改變輸出晶體管來切換許多不同的負(fù)載。 例如,10mA 時(shí)為 6 VDC(2N3904 晶體管),或 3 安培時(shí)為 40 VDC(2N3506 晶體管),甚至使用集電極開路達(dá)林頓晶體管。

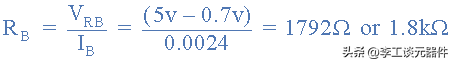

2、集電極開路輸出示例 No1

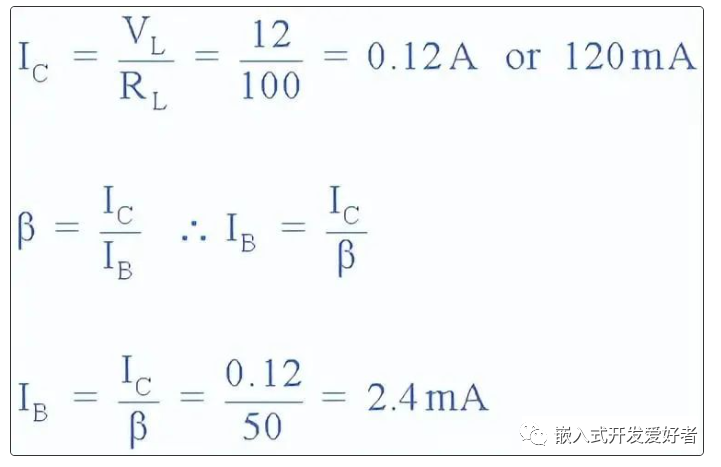

在這個(gè)電路中需要來自 Arduino 板的 +5 伏數(shù)字輸出引腳來驅(qū)動(dòng)機(jī)電繼電器。 如果繼電器線圈的額定電壓為 12 VDC、100Ω,并且在其集電極開路配置中使用的 NPN 晶體管的直流電流增益 (Beta) 值為 50,則計(jì)算操作繼電器線圈所需的基極電阻。

通過線圈的電流可以使用歐姆定律計(jì)算為:I = V/R

集電極開路計(jì)算公式

因此,對(duì)于直流電流增益為 50 的 NPN 晶體管,需要 2.4mA 的基極電流,忽略約 0.2 伏的集電極-發(fā)射極飽和電壓 (V CE(sat) )。 回想一下,晶體管的直流電流增益是指產(chǎn)生集電極電流需要多少基極電流。

當(dāng)晶體管完全導(dǎo)通時(shí),基極-發(fā)射極結(jié) (V BE )兩端的壓降將為 0.7 伏。 因此,所需的基極電阻 R B的值計(jì)算如下:

集電極開路計(jì)算公式

3、集電極開路工作原理

在集電極開路邏輯中,輸出要么接地,要么保持開路(斷開)。 當(dāng)輸出接地時(shí),輸出端電壓為0伏; 當(dāng)輸出開路時(shí),輸出電壓等于電源電壓。

集電極開路工作原理

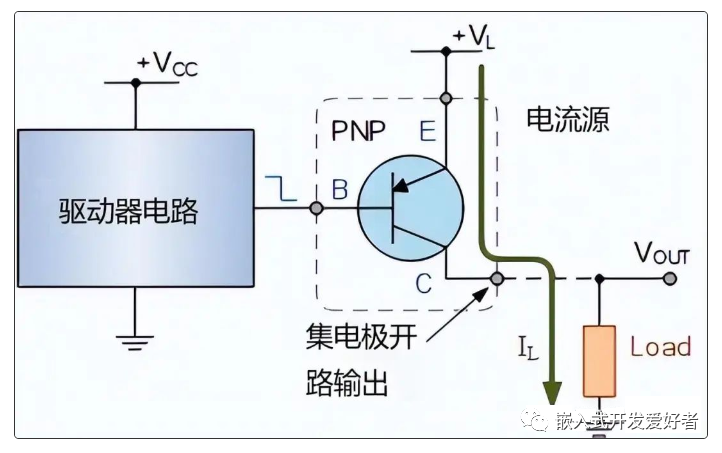

雖然 NPN 集電極開路晶體管電路產(chǎn)生“電流吸收”輸出,即 NPN 晶體管集電極開路端子會(huì)將電流吸收到地 (0V),PNP 型晶體管也可用于集電極開路配置以產(chǎn)生所謂的“電流源”輸出。

4、PNP 集電極開路輸出

上面我們已經(jīng)看到,集電極開路輸出的主要特點(diǎn)是負(fù)載信號(hào)在完全導(dǎo)通時(shí)通過 NPN 雙極晶體管的開關(guān)動(dòng)作主動(dòng)“下拉”到地電平,在關(guān)斷時(shí)再次被動(dòng)拉回產(chǎn)生電流吸收輸出。

但是我們可以創(chuàng)建相反的開關(guān)條件,方法是使用 PNP 雙極晶體管的集電極開路輸出主動(dòng)將其輸出切換到電源軌,并使用外部連接的“下拉”電阻器在關(guān)斷時(shí)再次將輸出被動(dòng)拉低。

對(duì)于 PNP 型集電極開路輸出,晶體管只能將輸出高電平切換到電源軌,因此其輸出端必須通過外部連接的“下拉”電阻再次被動(dòng)拉低,如下圖所示。

下圖為集電極開路 PNP 晶體管電路:

集電極開路 PNP 晶體管電路

然后我們可以看到,NPN 型或 PNP 型集電極開路輸出配置只能在 ON 時(shí)主動(dòng)將其輸出拉低至地,或拉高至電源軌(取決于晶體管類型),但其集電極端必須拉高如果連接的負(fù)載無法做到這一點(diǎn),則通過使用連接到其輸出端子的上拉或下拉電阻被動(dòng)地向上或向下。 所用輸出晶體管的類型及其開關(guān)動(dòng)作會(huì)產(chǎn)生電流吸收或電流源條件。

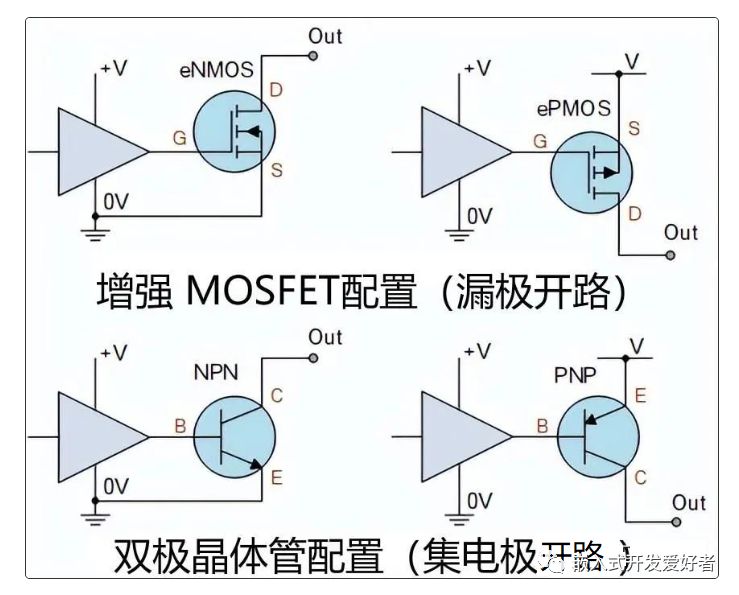

除了在集電極開路配置中使用雙極晶體管外,還可以在其開源配置中使用 n 溝道和 p 溝道增強(qiáng)型 MOSFET 或 IGBT。

與雙極結(jié)型晶體管 (BJT) 需要基極電流來驅(qū)動(dòng)晶體管進(jìn)入飽和狀態(tài)不同,常開(增強(qiáng)型)MOSFET 需要在其柵極 (G) 端子上施加合適的電壓。 MOSFET 的源極 (S) 端子直接連接到地或電源軌,而開漏 (D) 端子連接到外部負(fù)載。

將 MOSFET(或 IGBT)用作漏極開路(OD)器件時(shí),在驅(qū)動(dòng)功率負(fù)載或連接到更高電壓電源的負(fù)載時(shí),遵循與集電極開路輸出(OC)相同的要求,因?yàn)槭褂蒙侠蛳吕娮柽m用。 唯一的區(qū)別是 MOSFET 通道熱功率額定值和靜態(tài)電壓保護(hù)。

5、開漏增強(qiáng) MOSFET 配置

三、集電極開路電路--TTL 門

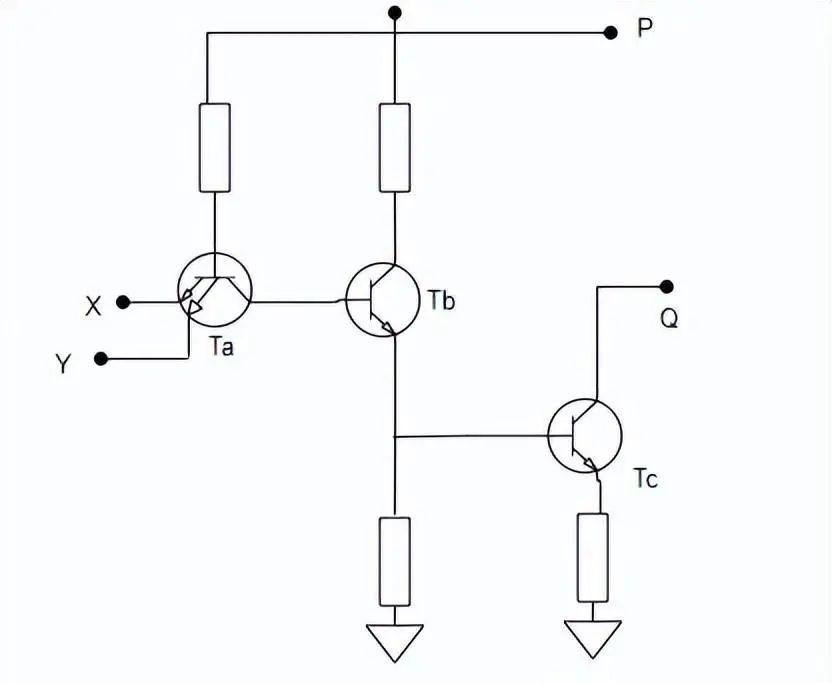

當(dāng)晶體管 Tc 從圖騰柱配置中移除時(shí),就會(huì)形成集電極開路 TTL 柵極。 通過在下圖中的輸出端子P和Q之間使用上拉電阻,可以將TTL與非門轉(zhuǎn)換為與門。

集電極開路電路--TTL 門

集電極開路與非門

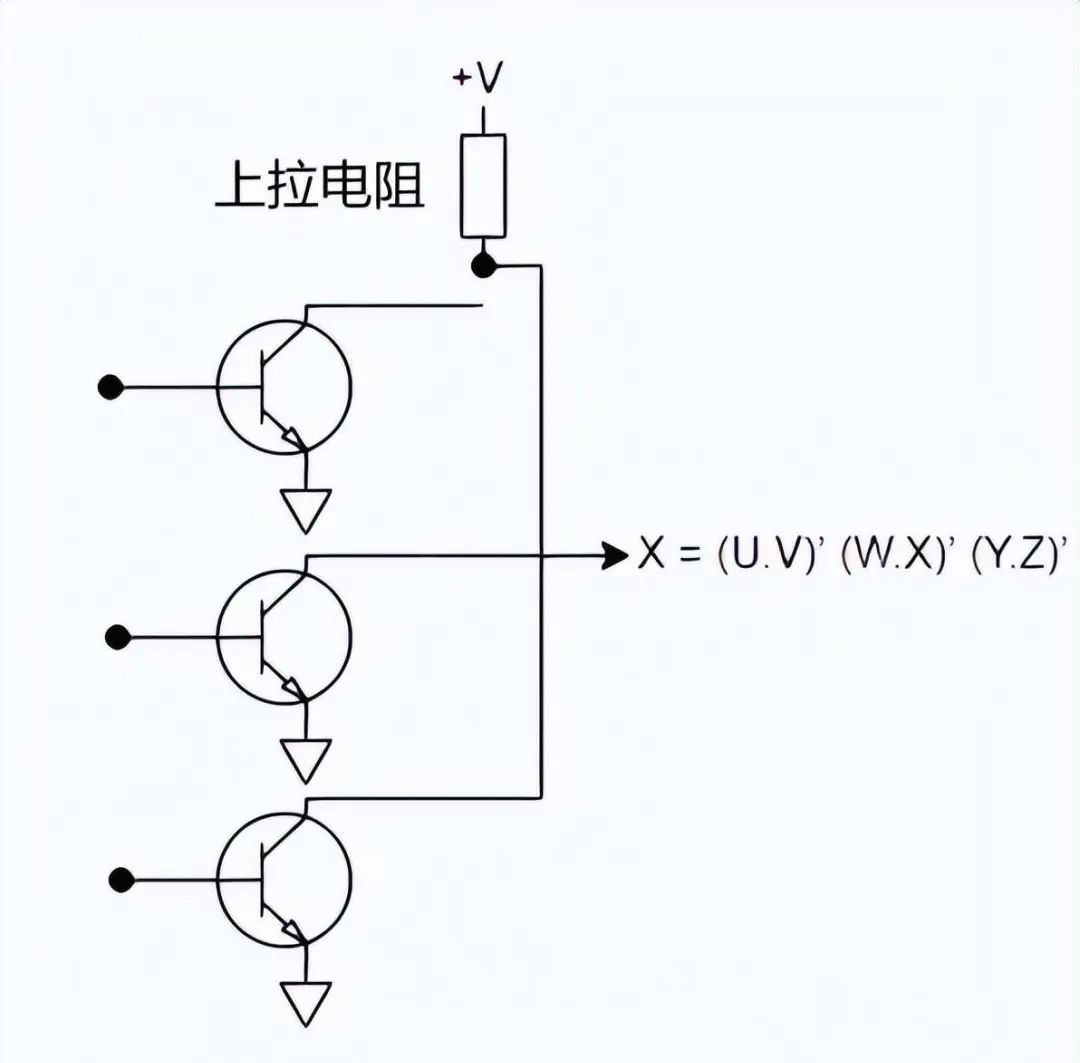

使用集電極開路邏輯門,可以開發(fā)有線 AND 和有線OR 門。 在下圖中,多個(gè)與門在集電極開路 TTL 門的幫助下進(jìn)行與運(yùn)算,結(jié)果顯示為接線與。 這是因?yàn)?AND 是通過對(duì)所有輸出進(jìn)行與運(yùn)算而產(chǎn)生的,可以表示如下:

X = (UV)' (WX)' (YZ)'

當(dāng)所有 NAND 門的集電極端子都為輸出晶體管短路時(shí),這將執(zhí)行 ANDing 操作。 通過這種有線或連接也可以通過德摩根原理得到,方程為

X = (UV + WX + YZ)'

在下圖中,上拉電阻值是通過每個(gè)輸出晶體管允許流過集電極端子的最大電流值已知的。

使用 TTL 與非門的有線與或

四、集電極開路輸出接線圖

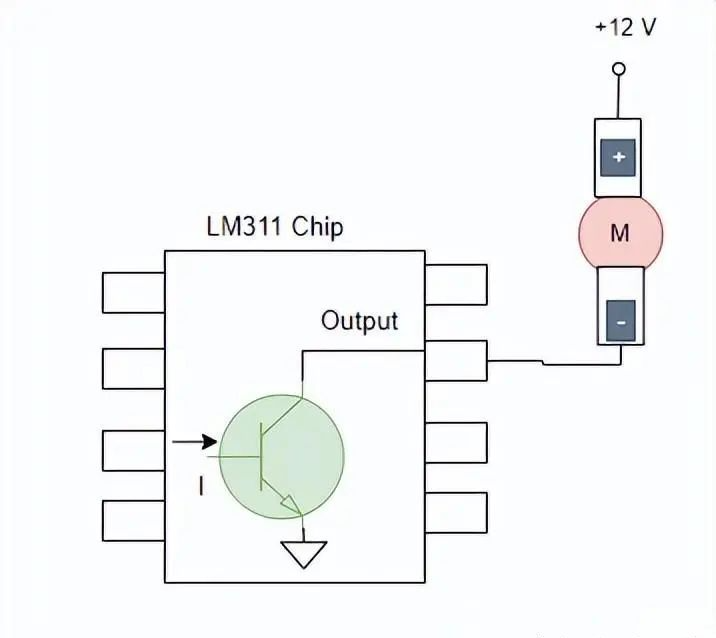

集電極開路電路通常用于電壓比較器。 很少有電壓比較器芯片是LM339、LM393和LM311,它們都作為集電極開路器件工作。

當(dāng)在輸出端連接任何設(shè)備時(shí),輸出設(shè)備應(yīng)連接到能夠驅(qū)動(dòng)負(fù)載的正電壓源。

例如:當(dāng)輸出設(shè)備為 12V 直流電機(jī)時(shí),則輸出應(yīng)接+12V。 然后,負(fù)載的負(fù)極和接地端子連接到驅(qū)動(dòng)電機(jī)的設(shè)備的輸出。

當(dāng)LM311芯片需要接一個(gè)12V直流電機(jī)時(shí),配置如下:

集電極開路輸出的LM311芯片

五、集電極開路的作用

集電極開路邏輯是一種輸出信號(hào)為漏極開路的邏輯。 這意味著輸出可以吸收電流,但不能提供電流。 集電極開路邏輯通常用于多個(gè)設(shè)備需要共享一條公共信號(hào)線的情況。

改進(jìn)的系統(tǒng)性能

較低的電容

更大的負(fù)載可以連接到收集器而沒有交叉擊穿的危險(xiǎn)

集電極開路輸出對(duì)電磁干擾相對(duì)不敏感

多個(gè)集電極開路輸出可以連接在一起以創(chuàng)建邏輯或功能。 例如,如果需要一個(gè)具有兩個(gè)輸入的 OR 函數(shù),可以將這些輸出中的一個(gè)連接到 A,將另一個(gè)連接到 B。 如果試圖找出哪個(gè)是的系統(tǒng)的更好選擇,這將很有用,例如, 是否使用 A 型或 B 型電機(jī)。

開漏輸出在未驅(qū)動(dòng)時(shí)具有高阻抗,因此非常適合用作狀態(tài)指示器。 集電極開路邏輯的缺點(diǎn)之一是需要高電壓才能關(guān)閉電路。

集電極開路輸出不能提供電流,因此不可能從單個(gè)集電極開路輸出驅(qū)動(dòng)多個(gè)負(fù)載。 設(shè)備的最大電壓輸出受驅(qū)動(dòng)設(shè)備的VOH(高電壓)限制。 例如,如果集電極開路由 5V 設(shè)備驅(qū)動(dòng),則可以施加到負(fù)載的最大電壓將為 5V。

六、集電極開路優(yōu)缺點(diǎn)

1、優(yōu)點(diǎn)

集電極開路邏輯的主要優(yōu)點(diǎn)是它很容易與其他數(shù)字設(shè)備連接。 集電極開路設(shè)計(jì)也不會(huì)像其他數(shù)字設(shè)計(jì)那樣受到串?dāng)_或噪聲的影響。 然而,集電極開路邏輯的缺點(diǎn)是它不如其他數(shù)字邏輯設(shè)計(jì)快。 集電極開路是某些集成電路 (IC) 上的一種輸出類型,它無法吸收與標(biāo)準(zhǔn)輸出一樣多的電流。 當(dāng)用作輸入時(shí),集電極開路給出與開關(guān)相同的結(jié)果:它可以是 ON 或 OFF。 使用集電極開路輸出的優(yōu)點(diǎn)是它可以連接到其他集電極開路作品以創(chuàng)建線或連接。

集電極開路邏輯的主要優(yōu)點(diǎn)是:

可用于在多個(gè)輸出之間創(chuàng)建線或連接。

集電極開路輸出可以吸收比標(biāo)準(zhǔn)輸出更多的電流,使其成為驅(qū)動(dòng) LED 和其他低電流設(shè)備的理想選擇。

集電極開路邏輯通常用于需要考慮電氣干擾 (EMI) 的應(yīng)用中,因?yàn)檩敵龊偷刂g沒有內(nèi)部連接可減少產(chǎn)生的 EMI 量。

2、缺點(diǎn):

使用集電極開路邏輯時(shí),主要缺點(diǎn)之一是可能存在競(jìng)爭(zhēng)。 當(dāng)兩個(gè)或多個(gè)設(shè)備試圖同時(shí)將輸出拉低時(shí),就會(huì)發(fā)生這種情況。 為了避免這種情況,必須使用適當(dāng)?shù)脑O(shè)計(jì)和布局技術(shù)。 另一個(gè)缺點(diǎn)是集電極開路輸出只能吸收電流,不能提供電流。 這意味著如果需要驅(qū)動(dòng)高電平信號(hào),就必須使用外部上拉電阻。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論