,幅度較小,源阻抗較高,并且共模電壓變化比較大。放大這些信號通常直流精度要求較高,失調電壓,失調電流通常是我們關注的參數,然而還有一個非常重要的參數,CMRR,共模抑制比也會對儀表放大器的精度造成

2022-11-14 06:20:19

(例如運算放大器或INA)抑制兩個輸入共用信號的能力。換言之,由于共模電壓與數據手冊中的規定不同,所以在輸入端出現偏置電壓。該偏移電壓除了初始輸入失調電壓外,還通過器件或電路的差分增益放大!CMRR

2019-03-21 06:45:01

,幅度較小,源阻抗較高,并且共模電壓變化比較大。放大這些信號通常直流精度要求較高,失調電壓,失調電流通常是我們關注的參數,然而還有一個非常重要的參數,CMRR,共模抑制比也會對儀表放大器的精度造成

2019-03-12 06:45:04

在信號線中使用共模扼流圈的目的是什么?共模扼流圈的等價電路圖中記載的黑點是什么意思?信號線用共模扼流圈的使用方法

2021-04-09 06:57:11

不同而不同,據此共模扼流線圈也會隨之發生變化。可根據傳輸信號波形判斷共模扼流線圈是否適用。一般來說共模扼流線圈的截止頻率以差動傳輸規格信號頻率的3倍使用。所謂的截止頻率是差模插入損耗變成3dB時的頻率

2020-05-23 14:52:57

今天發現幾個傳感器的激勵源都是差模信號,那是不是意味著差模信號抗干擾能力比共模信號強呢?{:6:}

2013-05-07 20:20:47

共模信號在OrCAD的原理圖里如何畫?

2015-10-28 11:00:16

在電子電路中經常會碰到共模信號,差模信號的字眼,一直對這兩個名詞理解不深。百度里是這樣說的:一對大小相等極性相反的就是差模信號;大小相同極性相同的為共模信號。其中共同點就是大小都要相同;以前我只以為只要大小和相位有其一不同就是差模,都相同才算共模。

2012-08-22 15:36:53

兩條電源線流出并從地線流回所造成的干擾。其產生的主要原因有很多,例如,接地電位不同導致電位差,引入共模干擾。輻射干擾在信號線感應的共模干擾(地-零線與地-火線面積不同,感應出不同的電流,造成共模干擾

2018-07-09 11:31:10

首先是共模信號和差模信號的定義,差模又稱串模,指的是兩根線之間的信號差值;而共模信號又稱對地信號,指的是兩根線分別對地的信號。

2019-05-24 06:42:35

;p><font face="Verdana"><strong>共模和差模信號及其噪音抑制&

2009-10-12 17:07:35

和共模電容一起作用,從而改變反饋信號的相位。因此,兩個連接反向輸入端的電容相加,加上2pF的導線的雜散電容。這個總電容與并聯阻抗反饋網絡(R1//R2)一起形成一個極點。一般認為:此極點的頻率應大于兩倍

2018-09-21 15:29:00

的原因有:圖 共模和差模電流· 外界電磁場在電路走線中的所有導線上感應出來電壓(這個電壓相對于大地是等幅和同相的),由這個電壓產生的電流;· 由于電路走線兩端的器件所接的地電位不同,在這個地電位差的驅動下

2011-11-18 09:40:36

請教一下基礎知識 共模電壓 同時加在電壓表兩測量端和規定公共端之間的那部分輸入電壓的一半這里輸入一半是什么意思? 還有通訊芯片datasheet里參數 提到驅動共模輸出電壓 在實際的應用中 這參數怎么用

2015-02-04 16:37:01

大家好,電源端和信號端用的共模電感,他們的電感量還有共模阻抗是分別是怎么計算的呀

2022-03-28 21:27:18

的磁場而相互抵消,此時正常信號電流主要受線圈電阻的影響(和少量因漏感造成的阻尼);當有共模電流流經線圈時,由于共模電流的同向性,會在線圈內產生同向的磁場而增大線圈的感抗,使線圈表現為高阻抗,產生較強

2013-01-05 15:59:41

電磁干擾。圖 2中的干擾信號則能很好地被共模電感抑制,而差分信號則幾乎無影響。2、CAN總線特性CAN收發器內部CANH、CANL分別為開源,開漏輸出形式,驅動電路如圖 3所示。這種方式可以使總線輕松

2020-03-31 15:38:02

電磁干擾。圖 2中的干擾信號則能很好地被共模電感抑制,而差分信號則幾乎無影響。2、CAN總線特性CAN收發器內部CANH、CANL分別為開源,開漏輸出形式,驅動電路如圖 3所示。這種方式可以使總線輕松

2020-03-31 15:38:53

共模扼流圈 (Common Mode Choke),也叫共模電感,是在一個閉合磁環上對稱繞制方向相反、匝數相同的線圈。常用于過濾共模的電磁干擾,抑制高速信號線產生的電磁波向外輻射發射,提高系統的EMC,在實際應用中一般是在差分的信號線上加共模電感。

2019-05-22 06:27:57

模干擾無電感抑制作用。但實際線圈繞制的不完全對稱會導致差模漏電感的產生。信號電流或電源電流在兩個繞組中流過時方向相反,產生的磁通量相互抵消,扼流圈呈現低阻抗。共模噪聲電流(包括地環路引起的騷擾電流,也

2019-05-21 09:11:11

本文就給大家簡單介紹一下共模電感的原理以及使用情況。共模電感是一個以鐵氧體為磁芯的共模干擾抑制器件,它由兩個尺寸相同,匝數相同的線圈對稱地繞制在同一個鐵氧體環形磁芯上,形成一個四端器件,要對于共模

2020-10-29 10:03:27

信號,使用傳統的阻容方式去匹配SIN和SIN_n,COS和COS_n仍然會在芯片引腳處出現共模電壓,超出2.3~4.0V的范圍,有時單端甚至超過了手冊中0.15~VDD-0.2V的范圍,造成角度跟蹤錯誤

2023-12-14 08:20:51

問題?

我的理解:

輸入的直流電壓信號應該在0-90mv內變化,輸出都應該成線性變化。(理解有誤?)正確的電路應該怎樣?

我用ADI公司的仿真軟件模擬過,如果共模電壓在2V左右或者接正負5V供電,(0-88mv)上述電路基本沒問題。如果不采用正負電壓供電,怎么樣在輸入端產生一個2V的共模電壓?

期盼解答!

2023-11-28 07:54:59

的理解:輸入的直流電壓信號應該在0-90mv內變化,輸出都應該成線性變化。(理解有誤?)正確的電路應該怎樣? 我用ADI公司的仿真軟件模擬過,如果共模電壓在2V左右或者接正負5V供電,(0-88mv)上述電路基本沒問題。如果不采用正負電壓供電,怎么樣在輸入端產生一個2V的共模電壓?期盼解答!

2018-11-26 09:32:37

在電路板上增加共模電壓。

3,我把取樣電阻接入運放AD627的 IN-那一端與地短接,結果輸出波形就正常了 ,但這個前提是我用AD627進行差分輸入就沒什么意義了,普通運放也能做到。

我想了很多辦法也不得其中原因,希望專家給我分析下 ,給點建議,感激涕零!

2024-01-09 07:12:33

AD7795輸入端能承受的最大共模電壓

2023-12-15 07:53:25

你好,我是從事IC測試的,目前在測試AD8138,其中差分輸入失調電壓這個參數,產品手冊給的信息是它等于二分之一的差模輸出電壓,即,Vosdm=1/2 Vodm。而共模輸入失調電壓等于共模輸出電壓

2023-11-17 16:13:48

1. 原理圖 圖12. 測試結果圖23. 問題1) 實驗原理如圖1,根據計算,輸出信號V+和V-應該是共模在Vocm=2V,但是測試結果如圖2,測試結果高于2V,這是問什么呢?2) 如圖2所示,可以看出黃色曲線的共模比綠線略低,這是為什么呢?與阻抗匹配有關嗎,請多多指教!

2018-12-11 11:36:20

您好,附件是AD8138的外圍電路,是參考芯片手冊的電路設計的。主要是為了實現單端轉差分的功能。現在出現幾個問題:1. 對于Vocm引腳,我從0V變化到750mV的過程中,輸出的共模電壓并不是芯片所

2018-11-12 09:41:19

AD8331VGA的差分輸出采用什么耦合方式轉成單端信號,能大大提高抑制共模噪聲?我現在用的是ADT1-6T,原理圖如下,希望ADI工程師幫我分析下這個電路可行嗎?有什么需要改進的地方?

2023-11-23 06:42:03

近期在使用AD9162時,配置的模式不成功,測試時鐘CLK發現,CLK±單端信號共模電壓接近0V,手冊上是0.6V,但測試9162-FMC-EZB參考板上的CLK也是共模電壓為0V,請問這個會有什么影響嗎?

我們現在測試配置JESD204B接口模式不正確,不確定是否CLK的影響?

2023-12-05 06:14:24

我加的共模電壓是1.5V。我空載的時候,該運放輸出的共模電壓,四路都是還比較準的1.5V,可是當我加上IQ信號后,四路的直流輸出就不一樣了,I+和I-之間存在60mV左右的偏差,Q路也一樣,這是為什么呢?求高手賜教!

2018-12-05 09:06:08

為了濾除DCDC輸出高達200mv的紋波,在DCDC的輸出級加入了共模電感濾波,具體的使用方法是共模電感的一段接DCDC輸出的3.8V,一端接地(PGND),輸出端的3.8V給后級的LDO轉為

2019-04-02 10:43:42

要做個系統,留給客戶DC24V輸入,但是想在DC輸入端添加濾波電路,因為系統對共模干擾信號很敏感,所以想了解一下怎樣濾除共模干擾?

2012-05-03 15:13:00

HMC960芯片應用時,采用阻容耦合,CMI(輸入共模電壓)、CMO(輸出共模電壓)必須連接嗎?

2023-11-15 07:05:33

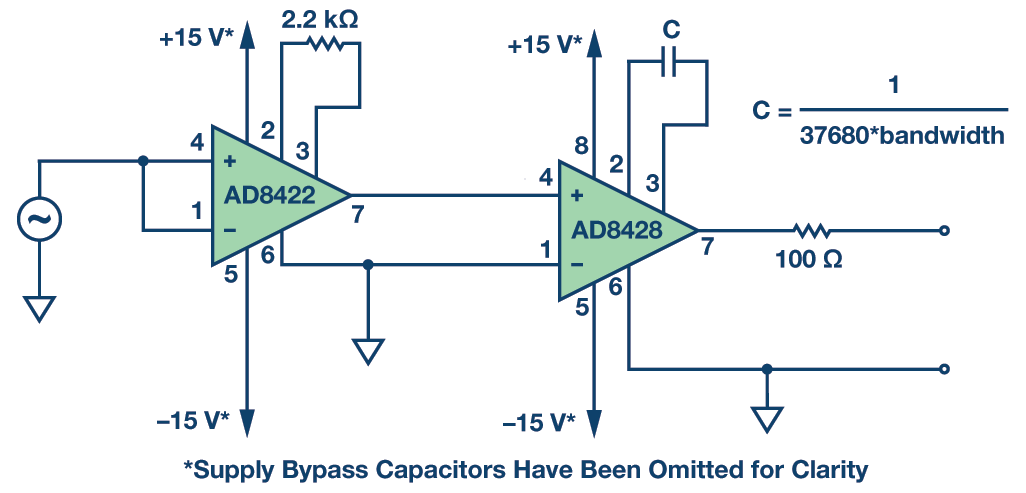

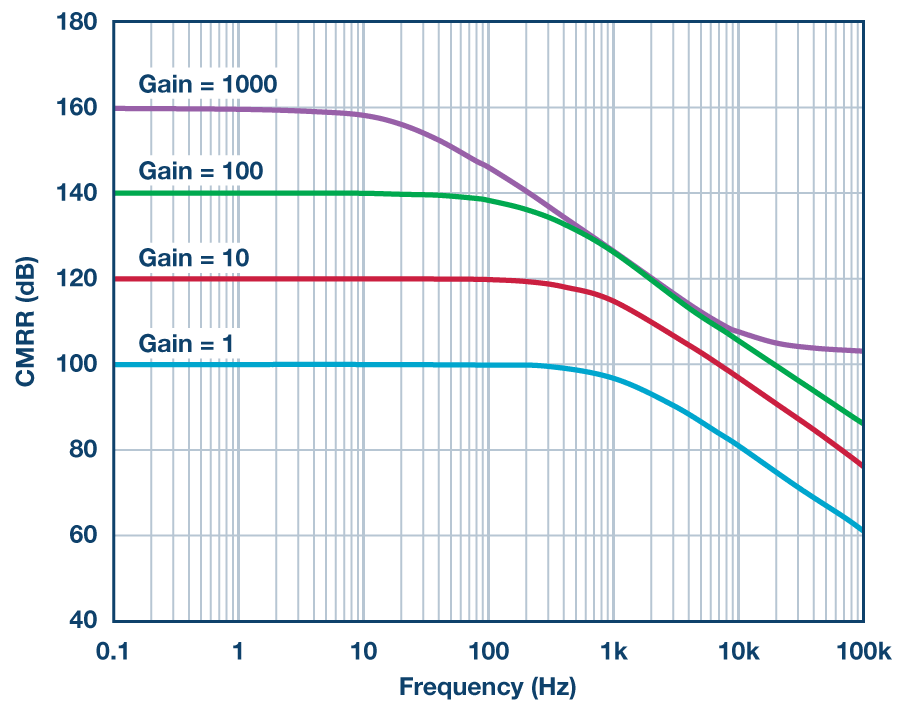

公式 2 是 CMRR 的學術定義,其中 Adm 是差分增益,Acm 是共模增益。包括 INA 在內的差分放大器不僅要抑制共模信號,而且還要放大差分信號。因此,根據公式 2 可知,增大 Adm 將提高

2018-09-17 16:29:31

PWM 逆變器產生的高頻共模電壓導致了其在變頻調速應用中的一系列負面效應。本文通過分析PWM 逆變器輸出的共模電壓成分,研究了逆變器輸出無源共模濾波器的設計。濾波器通過共模扼流圈和提供共模支路來達到

2019-02-03 21:01:41

OP1177與差分增益為1的AD8476級聯而實現的圖1. 改進的單端轉差分電路然而,許多應用需要更大的輸出動態范圍,例如溫度和壓力傳感器輸出的信號調理等。如果還能調節共模,那么該電路將能非常方便地

2019-09-29 08:30:00

在真正談論CMRR之前,必須先談論共模電壓。對于非反相配置的放大器,輸入信號是共模信號。反相配置始終具有與輸入信號無關的固定共模電壓。放大器共模電壓范圍取決于設計,且用戶需要確保其處于指定的工作范圍

2022-11-15 07:51:59

什么是共模與差模共模干擾產生原因共模干擾電流如何識別共模干擾 如何抑制共模干擾

2021-02-24 06:43:19

電壓電流的變化通過導線傳輸時有二種形態,我們將此稱做“共模”和“差模”。設備的電源線,電話等的通信線,與其它設備或外圍設備相互交換的通訊線路,至少有兩根導線,這兩根導線作為往返線路輸送電力或信號

2011-07-27 09:45:44

信號移動的中點—參見圖1。圖1. 差模與共模信號示例您也可以將其視為新中點或零代碼—放大器,通常通過一個VOCM 引腳或類似的器件,在輸出端建立CM。不過要小心,這些引腳也有一定的電流和電壓范圍要求

2018-10-11 10:34:45

的差分電壓,抑制兩個輸入端的共模。 圖 2:三運算放大器儀表放大器的標準拓撲放大器的輸入級包含兩個放大器:A1 和 A2。電源電壓或共模電壓的變化會帶來這兩個放大器輸入失調的相應變化,在圖 3 中分

2018-09-19 10:53:42

電路,使輸入信號置于運放VICMR區間規格內。第三,可以嘗試換用一種能滿足所有其它要求的軌至軌輸入運放。在選擇一款運放時,記住輸入共模電壓區間是最需懂得的重要規格。如果器件的輸入無法接受輸入信號的電平

2011-10-24 21:06:52

對稱式電路

長尾式差分放大電路

二、對共模信號影響

當電路輸入共模信號時:

一方面:基極電流和集電極電流的變化相等,因此集電極電位的變化也相等,即uC1=uC2。使得輸出電壓uo

2023-05-15 16:34:10

傳輸接口相比,運用HDMI必需愈加留意保證信號的質量。所以,如果在傳輸中存在噪聲,這對HDMI高清信號質量將會造成很大影響。 HDMI信號線里耦合了共模噪聲,則共模電流發生的磁場將得到增強,使得

2017-08-15 09:23:37

,以及如何通過運放內置的共模抑制和電源抑制來緩解這些誤差。差分放大器來測量CMRR。右圖將輸入的差模連接在一起,理論輸出為0.交越失真帶來的CMRR變化,因此數據手冊中可能會給出不同階段的CMR...

2021-12-30 06:50:21

帶可調輸出共模的多功能、精密單端轉的差分信號性能改進

2021-03-16 16:11:24

干擾信號,而對線路正常傳輸的差模信號無影響。 通常情況下,同時注意選擇所需濾波的頻段,共模阻抗越大越好,因此我們在選擇共模電感時需要看器件資料,主要根據阻抗頻率曲線選擇。另外選擇時注意考慮差模阻抗對信號的影響,主要關注差模阻抗,特別注意高速端口

2017-06-27 10:38:38

的基本電路如圖1所示。該五端器件有兩個輸入端、兩個輸出端和一個接地端,使用時外殼應接通大地。電路中包括共模扼流圈(亦稱共模電感)L、濾波電容C1~C4。L對串模干擾不起作用,但當出現共模干擾時,由于

2021-12-28 07:54:31

都可作為共模噪聲耦合。很多差分器件都能很好地抑制這種噪聲。下面是 LMH6881 可編程差分放大器 (PDA) 的共模抑制比 (CMRR) 圖示。CMRR 可確定差分信號受共模噪聲干擾的“污染程度

2022-11-21 06:34:35

共模抑制和差模信號介紹不同結構的儀表放大器解析

2021-04-07 06:04:27

,相位差為0°V3=0(4)共模信號的電路如圖3所示,其波形如圖4所示。因為在負載兩端沒有電位差,所以沒有電流流過負載。所有的共模電流都通過電纜和地之間的寄生電容流向地線。在以電纜傳輸信號時,因為共模信號

2011-08-10 14:21:36

差模和共模信號有什么特點?有什么方法可以抑制一般噪音?

2021-04-07 06:45:55

共模電感的原理差模噪聲和共模噪聲主要來源共模電感如何抑制共模信號共模電感的選取

2021-03-17 07:30:17

差分放大電路的差模信號是兩個輸入端信號的和,共模信號是兩個輸入端信號的差。這是為什么,能舉個例子嗎?

2023-03-31 14:06:38

分輸入測量浮動信號,在負輸入端接了個偏置電阻!!而在測量交流信號時,在正輸入端和負輸入端分別接一個偏置電阻。不知道這是什么原理,怎么能穩住共模電壓的,請高手指教!!!

2012-01-16 11:40:18

路徑。在差分信號路徑中,大部分環境噪聲都可作為共模噪聲耦合。很多差分器件都能很好地抑制這種噪聲。下面是 LMH6881 可編程差分放大器 (PDA) 的共模抑制比 (CMRR) 圖示。CMRR 可確定差

2018-09-13 14:27:23

開關電源共模電感和X電容的選取? - EMC論壇_可靠性設計 - 21ic電子技術開發論壇電磁干擾濾波器電路 電磁干擾濾波器的基本電路如圖1所示。該五端器件有兩個輸入端、兩個輸出端和一個接地端

2021-12-30 07:44:14

專注于重要的信號...比賽。信號通過量及中斷我看比賽的程度類似于放大器CMRR。在真正談論CMRR之前,必須先談論共模電壓。對于非反相配置的放大器,輸入信號是共模信號。反相配置始終具有與輸入信號無關

2019-03-20 06:45:09

1. 原理圖

圖1

2. 測試結果

圖2

3. 問題

1) 實驗原理如圖1,根據計算,輸出信號V+和V-應該是共模在Vocm=2V,但是測試結果如圖2,測試結果高于2V,這是問

2023-11-24 07:13:20

用數據采集卡測試SAR ADC/DAC,數據采集卡輸出和輸入(單端)的電壓范圍是-2V-2V,SAR ADC/DAC的輸入和輸出(單端)電壓范圍是0-2.5V,想用一個帶輸出共模電壓管腳的單端運算放大器匹配數據采集卡和SAR ADC/DAC之間的電壓范圍,求推薦,謝謝。

2023-11-15 06:37:35

角度,就像幾何學里的坐標變換,同一個點在不同坐標系中的坐標值不同,但始終是同一個點。運放的共模輸入范圍:器件(運放、儀放……)保持正常放大功能(保持一定共模抑制比 CMRR)條件下允許的共模信號的范圍

2018-01-09 09:00:50

輸入范圍:器件(運放、儀放……)保持正常放大功能(保持一定共模抑制比CMRR)條件下允許的共模信號的范圍。顯然,不存在“某一端”上的共模電壓的問題。但“某一端”也一樣存在輸入電壓范圍問題。而且這個范圍

2018-03-12 13:24:07

(3)大小相等,相位差為0°V3=0(4)共模信號的電路如圖3所示,其波形如圖4所示。因為在負載兩端沒有電位差,所以沒有電流流過負載。所有的共模電流都通過電纜和地之間的寄生電容流向地線。在以電纜傳輸信號

2019-05-22 09:25:43

如圖:升壓芯片tps61088,輸入11V左右,升壓輸出12V,輸出端串一個共模電感。調試時發現輸出電壓異常接近無,輸入端電感發出吱吱聲,后面取消這個共模電感后,輸出正常。不理解這個共模電感是怎樣影響的?請教各位。

2019-12-31 20:13:35

=13.3333px]AD9204允許的最大共模電壓輸入為1.3V)。[size=13.3333px]由于ADA4938并不是軌道軌輸出,它的輸出電壓最低只能到1.1V,因此單端輸出電壓范圍最大為1.1V~1.5V

2019-02-22 13:09:48

AD7795輸入端能承受的最大共模電壓

2018-08-23 09:09:33

你好,我是從事IC測試的,目前在測試AD8138,其中差分輸入失調電壓這個參數,產品手冊給的信息是它等于二分之一的差模輸出電壓,即,Vosdm=1/2 Vodm。而共模輸入失調電壓等于共模輸出電壓

2018-08-14 07:40:19

儀表yunrun.com.cn2、什么是共模干擾?共模干擾是指干擾電壓出現在儀表任一輸入端(正端或負端)對地之間的交流信號,這種干擾又稱為“對地干擾”和“縱向干擾”。 測量共模干擾電壓,可以用高阻電壓表

2018-06-19 21:29:21

fs,生成100mV的共模模信號Vc;3、ffs; 把Vd+Vc施加到AD7767的輸出端。計算量化數據中頻率為f和fs的功率,按10 log(Pf/Pfs)算出110dB?

2018-11-16 09:56:40

如圖1的反比例運放:(1)關于反比例運放,看到這句話 “有一點需要引起注意,對于反向比例放大電路,如下圖,它的同向端是接入到地的,由于“虛短”。此放運放的共模信號將為0,并且不隨信號的變化而改變

2018-01-31 21:34:00

運放輸入的共模信號和差摸信號,具體是怎么定義的?

2017-05-05 22:41:02

電子發燒友App

電子發燒友App

評論