他方面的損耗,反而會引起更嚴重的EMI問題,導致整個系統不能穩定工作。所以需要在減少MOSFET的損耗的同時需要兼顧模塊電源的EMI性能。

2017-12-24 08:36:53 16901

16901

瑞薩電子開發第三代車載SJ-MOSFET,計劃1~2年內開始量產。該器件降低了導通電阻和EMI(電磁噪聲)...

2013-05-31 09:22:20 1467

1467 基于最近的趨勢,提高效率成為關鍵目標,為了獲得更好的EMI而采用慢開關器件的權衡并不值得。超級結可在平面MOSFET難以勝任的應用中提高效率。與傳統平面MOSFET技術相比,超級結MOSFET可顯著降低導通電阻和寄生電容。

2014-04-17 11:24:12 1348

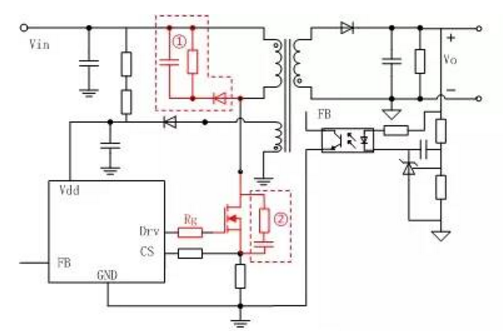

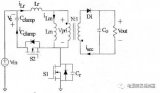

1348 本文主要闡述了MOSFET在模塊電源中的應用,分析了MOSFET損耗特點,提出了優化方法;并且闡述了優化方法與EMI之間的關系。

2015-09-18 14:33:17 6213

6213

簡化的MOSFET等效電路MOSFET開通(turn on)過程MOSFET損耗——Rds和Rg電阻損耗Di

2017-10-31 15:43:38 21570

21570

本文主要闡述了MOSFET在模塊電源中的應用,分析了MOSFET損耗特點,提出了優化方法;并且闡述了優化方法與EMI之間的關系。

2023-08-17 09:16:30 1300

1300

在高功率應用中,碳化硅(SiC)MOSFET與硅(Si)IGBT相比具有多項優勢。其中包括更低的傳導和開關損耗以及更好的高溫性能。

2023-09-11 14:55:31 347

347

東芝將進一步擴大其MOSFET產品線,通過減少損耗提高設備電源效率,進而幫助其降低功耗。

2022-03-31 11:13:27 1196

1196

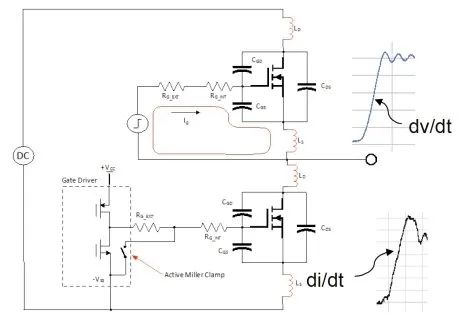

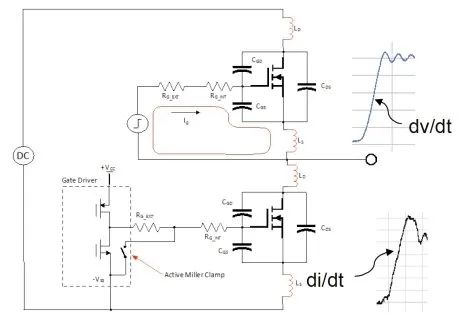

正確的二極管外,設計人員還能夠通過調節柵極驅動導通源阻抗來控制Eon損耗。降低驅動源阻抗將提高IGBT或MOSFET的導通di/dt及減小Eon損耗。Eon損耗和EMI需要折中,因為較高的di/dt 會

2018-08-27 20:50:45

阻抗將提高IGBT或MOSFET的導通di/dt及減小Eon損耗。Eon損耗和EMI需要折中,因為較高的di/dt會導致電壓尖脈沖、輻射和傳導EMI增加。為選擇正確的柵極驅動阻抗以滿足導通di/dt

2021-06-16 09:21:55

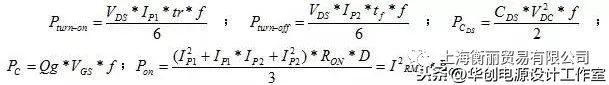

MOSFET功率損耗的詳細計算

2023-09-28 06:09:39

提高電源的開關和導通損耗。此外,它還會提高電磁干擾的噪聲水平,從而使設計出的產品達不到理想的性能。若要最大限度降低電路板布局帶來的影響,設計人員必須確保通過將驅動和MOSFET盡可能地背靠背放置,從而

2019-05-13 14:11:31

內部二極管的反向恢復時間trr高速化的ROHM SJ-MOSFET。PrestoMOS的FN系列與標準型AN系列相比,trr速度提高至約1/5。同時,反向恢復電流Irr也降低至約1/3。這些特性的提升

2018-11-28 14:27:08

MOSFET較小的柵極電阻可以減少開通損耗嗎?柵極電阻的值會在開通過程中影響與漏極相連的二極管嗎?

2023-05-16 14:33:51

MOSFET更好的在系統中應用,需要給碳化硅MOSFET匹配合適的驅動。 接下來介紹基本半導體碳化硅MOSFET及驅動產品 基本半導體自主研發的碳化硅 MOSFET 具有導通電阻低,開關損耗小的特點,可降低

2023-02-27 16:03:36

的SiC,可使用更小的電感器,仍能達到以前相同的電感器紋波電流要求。在OBC系統中使用SiC MOSFET的好處是能夠以更高的頻率進行開關,功率密度更高,能效更高,EMI性能得到改善以及系統尺寸減小

2022-05-30 10:01:52

電機效率的影響因素降低電機損耗的關鍵制造技術

2021-01-26 07:49:16

使用絕緣柵雙極晶體管(IGBT)。但隨著半導體技術的進步,碳化硅 (SiC) 金屬氧化物半導體場效應晶體管 (MOSFET) 能夠以比 IGBT 更高的頻率進行開關,通過降低電阻和開關損耗來提高

2022-11-02 12:02:05

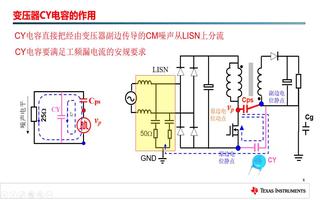

降低電源中的EMI

2021-08-25 17:11:19

導通電阻,但成本的提高所付出的代價是商業品所不允許的。引入少數載流子導電雖能降低導通壓降,但付出的代價是開關速度的降低并出現拖尾電流,開關損耗增加,失去了MOSFET的高速的優點。 以上兩種辦法

2023-02-27 11:52:38

B1M080120HC是一款碳化硅 MOSFET 具有導通電阻低,開關損耗小的特點,可降低器件損耗,提升系統效率,更適合應用于高頻電路。降低器件損耗,提升系統 EMI 表現。在新能源汽車電機控制器

2021-11-10 09:10:42

轉換器采用R6004END時,開關損耗略有減少,兩種因素疊加可使效率提高1%左右。另外,在開關損耗降低的同時,噪聲也得以改善。綜上所述,通過重新探討開關MOSFET的特性和柵極電阻,可同時改善效率和噪聲,因此,與上一篇、上上篇中提到的二極管相同,MOSFET的特性也需要充分進行探討和確認。

2022-04-09 13:36:25

的基礎。MOSFET設計的改進可使電路設計者充分發揮改進器件的性能,比如開關性能的提高和其他幾個關鍵參數的改善,可確保轉換器能夠更高效地運行。某些情況下,還可對設計的電路進行修改。若不采用這些改進

2018-12-07 10:21:41

關斷器件。這會大大延遲關斷,從而增加MOSFET的功率損耗,降低轉換效率。此外,雜散電感可導致電路中出現超過器件電壓額定值的電壓尖峰,從而導致出現故障。 旨在降低電阻和提升熱性能的封裝改進還可極大

2018-09-12 15:14:20

的調制,以引入邊帶能量,并改變窄帶噪聲到寬帶的發射特征,從而有效地衰減諧波峰值。需要注意的是,總體 EMI 性能并沒有降低,只是被重新分布了。利用正弦調制,可控變量的兩個變量為調制頻率 (fm) 以及您

2017-05-16 16:56:41

本帖最后由 張飛電子學院魯肅 于 2021-1-30 13:21 編輯

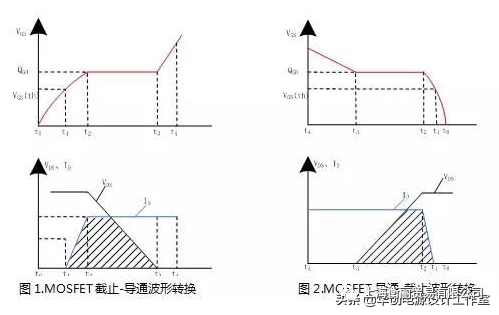

本文詳細分析計算功率MOSFET開關損耗,并論述實際狀態下功率MOSFET的開通過程和自然零電壓關斷的過程,從而使電子

2021-01-30 13:20:31

模塊電源的開關頻率來降低驅動損耗,從而進一步提高輕負載條件下的效率,使得系統在待機工作下,更節能,進一步提高蓄電池供電系統的工作時間,并且還能夠降低EMI的輻射問題;2.通過降低、來減少MOSFET

2019-09-25 07:00:00

就可通過降低RDS(ON)和柵極電荷(Qg),最大限度地減少傳導損耗和提高開關性能。這樣,MOSFET就能應對開關過程中的高速電壓瞬變(dv/dt)和電流瞬變(di/dt),甚至可在更高的開關頻率下可靠地工作。

2019-09-04 07:00:00

外,設計人員還能夠通過調節柵極驅動導通源阻抗來控制Eon損耗。降低驅動源阻抗將提高IGBT或MOSFET的導通di/dt及減小Eon損耗。Eon損耗和EMI需要折中,因為較高的di/dt 會導致電壓尖

2019-03-06 06:30:00

。設計挑戰然而,SiC MOSFET 技術可能是一把雙刃劍,在帶來改進的同時,也帶來了設計挑戰。在諸多挑戰中,工程師必須確保:以最優方式驅動 SiC MOSFET,最大限度降低傳導和開關損耗。最大

2017-12-18 13:58:36

SiC-MOSFET和SiC肖特基勢壘二極管的相關內容,有許多與Si同等產品比較的文章可以查閱并參考。采用第三代SiC溝槽MOSFET,開關損耗進一步降低ROHM在行業中率先實現了溝槽結構

2018-11-27 16:37:30

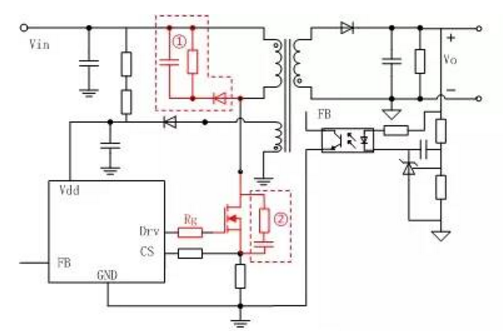

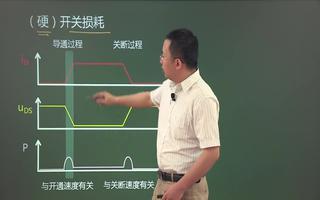

,提高開關的速度,從而降低開關損耗,但是過高的開關速度會引起EMI的問題。(2)提高柵極驅動電壓也可以提高開關的速度,降低開關損耗。同時,高的柵極驅動電壓會增加驅動損耗,特別是輕載的時候,對效率

2017-03-06 15:19:01

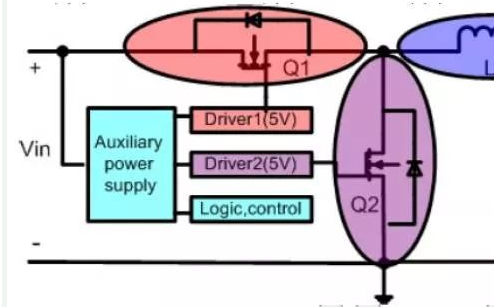

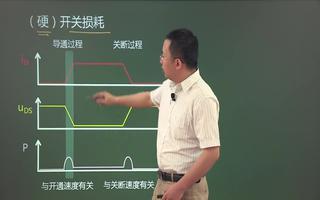

過程中的開關損耗。開關損耗內容將分成二次分別講述開通過程和開通損耗,以及關斷過程和和關斷損耗。功率MOSFET及驅動的等效電路圖如圖1所示,RG1為功率MOSFET外部串聯的柵極電阻,RG2為功率

2017-02-24 15:05:54

無論您的系統是用于無線通信、雷達,還是 EMI/EMC 測試,系統的性能水平都是由其中的天線決定的。系統天線的性能決定了系統的整體質量,最終可能會影響整個程序或應用軟件的效率。本文介紹了 5 個旨在幫助您提高天線性能的關鍵要點。

2021-02-24 07:24:14

開關管MOSFET的功耗分析MOSFET的損耗優化方法及其利弊關系

2020-12-23 06:51:06

問題:如何使用擺率控制來降低EMI?

2019-03-05 20:59:44

MOSFET的驅動電流,減緩該MOSFET的接通時間,同時有助于降低開關節點振鈴噪音。注意:減慢高側MOSFET的關閉時間會增大開關損耗。在低電磁輻射和高側MOSFET的開關損耗之間選用RHO時,需要

2018-08-31 19:55:41

從事低電磁干擾 (EMI) 應用的設計工程師通常面臨兩大挑戰:需要降低設計的 EMI,同時還要縮小解決方案尺寸。用于減輕開關電源產生的傳導 EMI 的前端無源濾波可確保符合傳導 EMI 標準,但這種

2021-08-31 14:58:42

如何去降低USB 3.x的插入損耗?有大神能解答這個問題嗎

2021-07-15 06:26:36

對于各種不同的數據中心工作負載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-10-10 07:46:05

汽車電源設計之不改PCB如何降低EMI

2021-03-18 06:04:50

如何更加深入理解MOSFET開關損耗?Coss產生開關損耗與對開關過程有什么影響?

2021-04-07 06:01:07

如何測量EMI濾波器插入損耗

2014-04-04 10:44:43

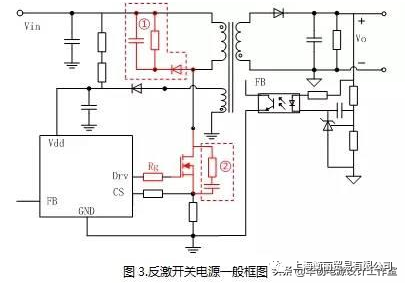

開關電源設計中,我們常常使用到一個電阻串聯一個電容構成的RC電路, RC電路性能會直接影響到產品性能和穩定性。如何設計既能降低開關管損耗,且可降低變壓器的漏感和尖峰電壓的RC電路?

2019-01-10 14:07:18

問題:如何通過驅動高功率LED降低EMI?

2019-03-05 14:33:29

中的寄生源電感。因此,采用SMD封裝的MOSFET也能實現快速開關,同時降低開關損耗。適用于4引腳器件的SMD封裝名為“ThinkPAK 8X8”。 III.分析升壓轉換器中采用最新推出的TO247

2018-10-08 15:19:33

射頻VMMK器件是怎么提高性能的?通過降低寄生電感和電容嗎?

2019-08-01 08:23:35

ROHM在全球率先實現了搭載ROHM生產的SiC-MOSFET和SiC-SBD的“全SiC”功率模塊量產。與以往的Si-IGBT功率模塊相比,“全SiC”功率模塊可高速開關并可大幅降低損耗

2018-12-04 10:14:32

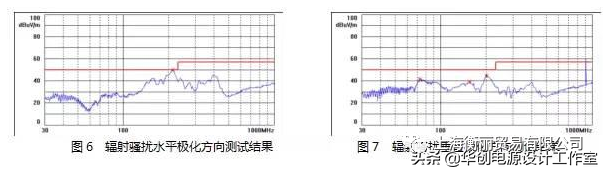

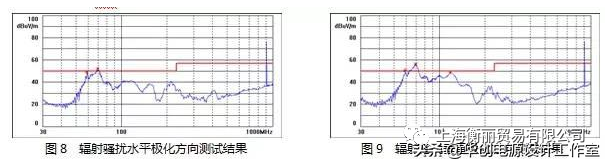

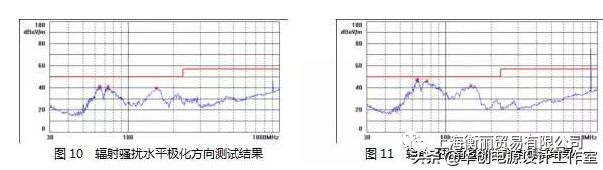

效率。圖8.將啟動電阻器添加到LMR23630轉換器開關節點的影響。EMI輻射較低,但由于開關損耗較高,因此效率有所降低。圖8顯示了LMR23630 EVM的EMI輻射掃描。對布局進行更改后,將輸入

2019-06-03 00:53:17

解決問題:怎么改變電源頻率來降低EMI性能 解決辦法:調制電源開關頻率延伸EMI特征 更大調制指數進一步降低峰值EMI性能 文章里的這種方法涉及了對電源開關頻率的調制,以引入邊帶能量,并

2016-01-15 09:57:10

今天的電源設計人員和測試工程師都在努力尋找非常小的漸進改良方案,來提高功率轉換效率,或降低設計中的損耗。這要求能夠準確評估和測量非常小的性能提高。

2019-08-12 06:24:09

設計角度,討論如何降低電路 EMI。為提高開關電源的功率密度,電源工程師首先想到的辦法是選擇開關頻率更高的 MOSFET,通過提高開關速度可以顯著地減小輸出濾波器體積,從而在單位體積內可實現更高的功率

2020-10-10 08:31:31

將去耦電容直接放在IC封裝內可以有效控制EMI并提高信號的完整性,本文從IC內部封裝入手,分析EMI的來源、IC封裝在EMI控制中的作用,那么,最佳EMI抑制性能的設計規則具體有哪些呢?

2019-08-06 07:58:53

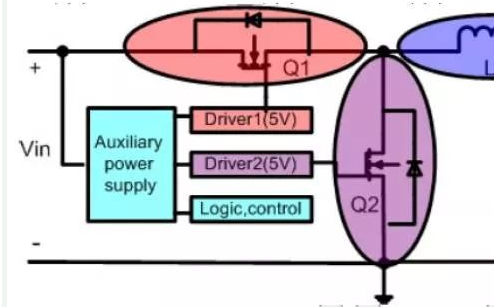

能夠正常工作,這個損耗是無法避免的,在IC選型的時候盡量選擇工作電流小的。 四、開關管損耗 輸入端的MOS管Q1在待機的時候,主要體現的是開關損耗,所以需要降低待機時MOS管的損耗,待機的工作頻率

2023-03-20 16:59:01

功率MOSFET的Coss會產生開關損耗,在正常的硬開關過程中,關斷時VDS的電壓上升,電流ID對Coss充電,儲存能量。在MOSFET開通的過程中,由于VDS具有一定的電壓,那么Coss中儲能

2017-03-28 11:17:44

減小硅鋼片的厚度,但薄鐵芯片會增加鐵芯片數目和電機制造成本。3、采用導磁性能良好的冷軋硅鋼片降低磁滯損耗。4、采用高性能鐵芯片絕緣涂層。5、熱處理及制造技術,鐵芯片加工后的剩余應力會嚴重影響電動機

2018-10-11 10:21:49

MOSFET的半導體廠商。 此外,集成一個類似肖特基的二極管可提高系統能效,并降低尖峰電壓。它采用的是一種單片集成式單元結構,相比常規MOSFET體二極管而言,在很寬的負載范圍內具備多種關鍵優勢。一方面

2018-12-06 09:46:29

設計角度,討論如何降低電路EMI。為提高開關電源的功率密度,電源工程師首先想到的辦法是選擇開關頻率更高的MOSFET,通過提高開關速度可以顯著地減小輸出濾波器體積,從而在單位體積內可實現更高的功率等級

2020-10-21 07:13:24

新技術就可通過降低RDS(ON)和柵極電荷(Qg),最大限度地減少傳導損耗和提高開關性能。這樣,MOSFET就能應對開關過程中的高速電壓瞬變(dv/dt)和電流瞬變(di/dt),甚至可在更高的開關頻率下

2011-08-17 14:18:59

MOSFET和去耦電容器的布局布置。目的是在開關換向期間最大程度地減小功率環路寄生電感并降低電壓過沖。隨之而來的三個優點是:更低的電磁干擾(EMI),更低的開關電壓應力和更高的轉換效率。48V電池電壓變化

2019-09-21 13:25:03

有源EMI濾波技術是一種較新的EMI濾波方法,可減弱電磁干擾,讓工程師能夠大幅縮小無源濾波器的尺寸、降低成本并提升EMI性能。為了說明有源EMI濾波器在EMI性能提升和空間節省方面的主要優勢,在本文

2022-11-04 08:12:50

%。-明白了。最后請你總結一下,謝謝。SiC MOSFET具有超低導通電阻和高速開關的特點,還具有可進一步縮小電路規模、提高相同尺寸的功率、以及因降低損耗而提高效率并減少發熱量等諸多優點。另一方面,關于

2020-07-01 13:52:06

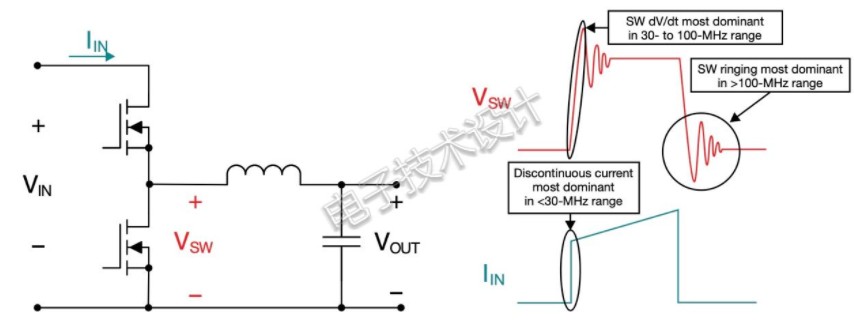

噪聲的傳導回路面積較大,進一步推動輻射發射的產生。在第 3 部分中,我將全面介紹降壓穩壓器電路中影響 EMI 性能和開關損耗的感性和容性寄生元素。通過了解相關電路寄生效應的影響程度,可以采取適當的措施將

2020-11-03 07:54:52

在第 3 部分中,我將全面介紹降壓穩壓器電路中影響 EMI 性能和開關損耗的感性和容性寄生元素。通過了解相關電路寄生效應的影響程度,可以采取適當的措施將影響降至最低并減少總體 EMI 信號。一般來說

2022-11-09 07:38:45

圖1:開關損耗讓我們先來看看在集成高側MOSFET中的開關損耗。在每個開關周期開始時,驅動器開始向集成MOSFET的柵極供應電流。從第1部分,您了解到MOSFET在其終端具有寄生電容。在首個時段(圖

2022-11-16 08:00:15

的SJ-MOSFET。通過降低柵極電阻Rg和柵極-漏極間電荷量Qgd,提高了開關性能。通過提高開關速度,可降低開關損耗并提高效率。最后列出了這三個系列相關技術信息的鏈接。這里雖然給出了各系列的特征,但為了進一步

2018-12-03 14:27:05

根據MOSFET的簡化模型,分析了導通損耗和開關損耗,通過典型的修正系數,修正了簡化模型的極間電容。通過開關磁鐵電源的實例計算了工況下MOSFET的功率損耗,計算結果表明該電源中

2011-11-14 16:46:22 112

112 為了有效解決金屬-氧化物半導體場效應晶體管(MOSFET)在通信設備直流-48 V緩啟動應用電路中出現的開關損耗失效問題,通過對MOSFET 柵極電荷、極間電容的闡述和導通過程的解剖,定位了MOSFET 開關損耗的來源,進而為緩啟動電路設計優化,減少MOSFET的開關損耗提供了技術依據。

2016-01-04 14:59:05 38

38 MOSFET的損耗主要包括如下幾個部分:1導通損耗,導通損耗是比較容易理解的,即流過MOSFET的RMS電流在MOSFET的Rdson上的I^2R損耗。降低這個損耗也是大家最容易想到的,例如選用更低

2017-11-22 17:26:02 25214

25214

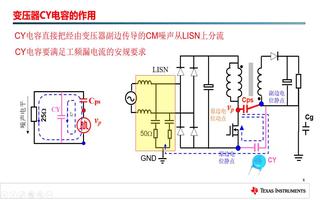

本文將介紹開關電源中EMI的來源以及降低EMI的方法或技術。本文還將向您展示電源模塊(控制器、高側和低側FET及電感器封裝為一體)如何幫助降低EMI。

2018-10-17 18:08:15 8065

8065 MOSFET的損耗分析

2019-04-17 06:44:00 6005

6005

1.7 EMI濾波器與插入損耗

2019-02-20 06:14:00 10996

10996

開關電源小型化設計中,提高開關頻率可有效提高電源的功率密度。但隨著開關頻率提升,電路電磁干擾(EMI)問題使電源工程師面臨了更大的挑戰。本文以反激式開關拓撲為例,從設計角度,討論如何降低電路EMI。

2019-07-19 16:02:28 640

640 優秀PCB設計練習降低PCB的EMI有許多方法可以降低PCB設計的EMI基本原理:電源和地平面提供屏蔽頂層和

2019-08-20 09:11:38 3845

3845 Mosfet的損耗主要有導通損耗,關斷損耗,開關損耗,容性損耗,驅動損耗

2020-01-08 08:00:00 11

11 降低開關頻率也會增加轉換器電感、輸出電容和輸入電容的物理尺寸。同時,需要使用一個大尺寸π濾波器以通過傳導輻射測試。隨著開關頻率降低,濾波器中的電感L和電容C需相應增大。在低壓線路滿載條件下,電感電流額定值應大于最大輸入電流。因此,前端需要使用一個大尺寸電感和多個電容以符合嚴格的EMI標準。

2020-08-06 10:07:50 3392

3392 超高效電機最重要的是工藝保證程度。電動機效率不斷提高的過程是產品不斷更新換代的過程,同時也是一個國家電機工業綜合水平的標志。

高效電動機的設計要點就是要降低各項損耗,提高電動機效率

2020-09-10 10:19:05 1490

1490 隨著電路集成化、模塊化,電路分析和設計可以說成是系統的分析和設計,EMI方案研究會對今后的電子產品性能提高有顯著影響。電子產品的日益普及,以及對電磁危害的逐漸認識,減小電磁干擾EMI已經成為了目前電子科學界的重要課題。下面分析下如何降低電源模塊EMI。

2021-03-03 17:21:43 2581

2581 功率MOSFET的開關損耗分析。

2021-04-16 14:17:02 48

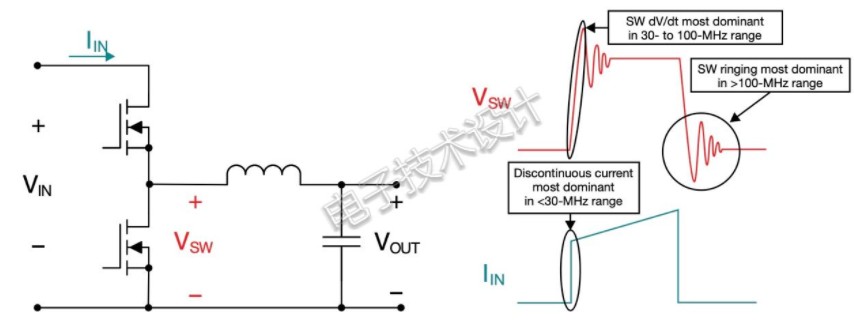

48 圖1以降壓轉換器拓撲為例,說明了不同頻帶下各個因素的影響。隨著設計壓力不斷提升,通過提高開關頻率來降低尺寸和成本,以及通過增大壓擺率來提高效率,使EMI問題變得更加嚴重。因此,有必要采用不影響電源設計、同時具有成本效益且易于集成的EMI緩解技術。

2021-05-01 09:17:00 4041

4041

AN144-通過靜默交換機設計降低EMI并提高效率

2021-05-07 15:27:55 6

6 節省空間,降低EMI

2021-05-20 11:42:15 6

6 性能的影響強弱,探討了如何降低高速PCB的插入損耗,可為高速PCB的選材和加工工藝設計提供參考。 關鍵詞:高速電路板;高速材料;加工工藝;插入損耗;信號完整性 0引言 隨著高速互聯鏈路信號傳輸速率的不斷提高,作為器件和信號傳輸的

2021-11-23 16:39:00 8973

8973

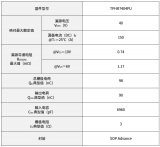

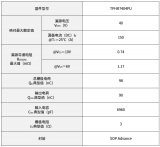

TPHR7404PU 做電源設計的工程師朋友都知道,MOSFET由于其快速開關,導通電壓低等特性,在電源設計中應用的非常廣泛。但是使用MOSFET時易出現的尖峰電壓會增加EMI(電磁干擾

2021-11-26 15:08:03 2422

2422

在功率半導體器件中,MOSFET以高速、低開關損耗、低驅動損耗在各種功率變換,特別是高頻功率變換中起著重要作用。在低壓領域,MOSFET沒有競 爭對手,但隨著MOS的耐壓提高,導通電阻隨之

2022-03-11 11:20:17 3004

3004

在功率半導體器件中,MOSFET以高速、低開關損耗、低驅動損耗在各種功率變換,特別是高頻功率變換中起著重要作用。在低壓領域,MOSFET沒有競 爭對手,但隨著MOS的耐壓提高,導通電阻隨之

2022-03-17 09:35:33 2873

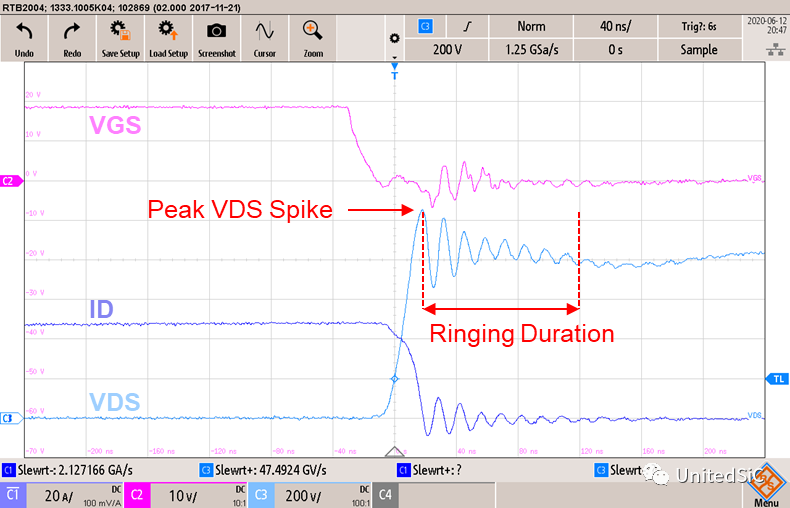

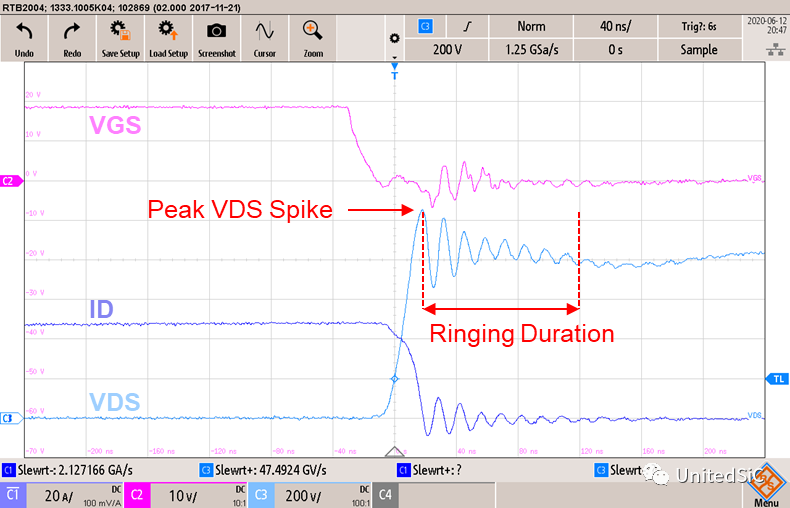

2873 寄生電感是SiC MOSFET Vds尖峰和振鈴的主要原因。SiC MOSFET的快速開關速度會導致較高Vds尖峰和較長的振鈴時間。這種尖峰會降低設備的設計裕量,并且較長的振鈴時間會引入EMI。

2022-08-29 15:20:38 1010

1010 干貨 | 如何降低晶體管和變壓器損耗,提高開關電源效率?

2023-01-05 09:51:42 388

388 降低定子銅耗的措施,主要包括減小定子電阻、縮短繞組端部長度;減薄絕緣,提高槽滿率、增加導線截面積、采用新材料降低電磁線的電阻率等;

2023-01-15 14:34:24 968

968 關鍵要點 ? SiC MOSFET因其在降低功率轉換損耗方面的出色表現而備受關注。 ? 以DC-DC轉換器和EV應用為例,介紹使用新一代(第4代)SiC MOSFET所帶來的優勢–降低損耗

2023-02-15 23:45:05 343

343 的傳導和開關損耗,本文以給出了使用ST碳化硅MOSFET的主要設計原則,以得到最佳性能。一,如何減少傳導損耗:碳化硅MOSFET比超結MOSFET要求更高的G級電壓

2022-11-30 15:28:28 2648

2648

電子發燒友網站提供《DMC4040SSD可降低MOSFET損耗 確保可靠運行.pdf》資料免費下載

2023-07-25 16:07:11 0

0 性能提升,功耗降低!,這樣的MOSFET是你的最愛么?

2023-12-04 15:09:36 114

114

使用SiC MOSFET時如何盡量降低電磁干擾和開關損耗

2023-11-23 09:08:34 333

333

變壓器有哪些損耗?如何降低變壓器的損耗? 變壓器中存在幾種主要的損耗,包括銅損、鐵損和額外損耗。下面將詳細介紹這些損耗,并提出一些有效降低變壓器損耗的方法。 一、銅損 銅損是由于變壓器的線圈電阻

2023-11-23 15:04:28 1377

1377

電子發燒友App

電子發燒友App

評論