SiC MOSFET 在功率半導體市場中正迅速普及,因為它最初的一些可靠性問題已得到解決,并且價位已達到非常有吸引力的水平。隨著市場上的器件越來越多,必須了解 SiC MOSFET 與 IGBT 之間的共性和差異,以便用戶充分利用每種器件。本系列文章將概述安森美 M 1 1200 V SiC MOSFET 的關鍵特性及驅動條件對它的影響,作為安森美提供的全方位寬禁帶生態系統的一部分,還將提供?NCP51705(用于 SiC MOSFET 的隔離柵極驅動器)的使用指南。本文為第二部分,將重點介紹安森美M 1 1200 V SiC MOSFET的?動態特性?。

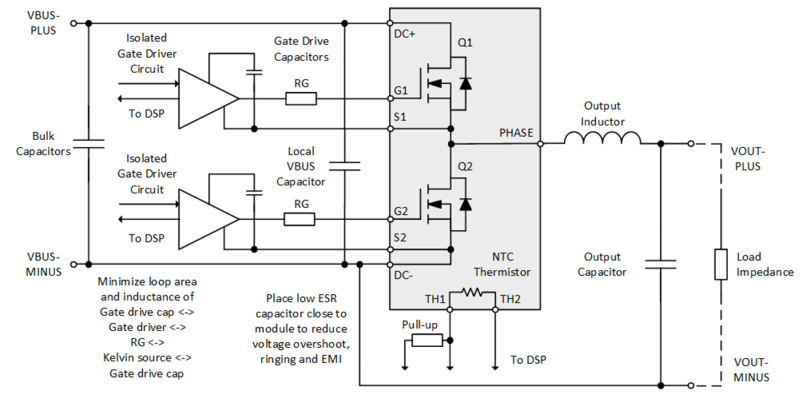

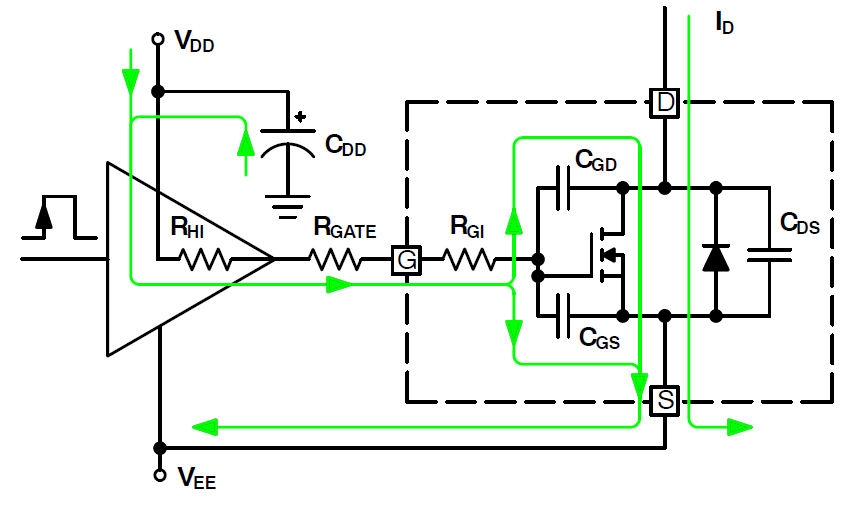

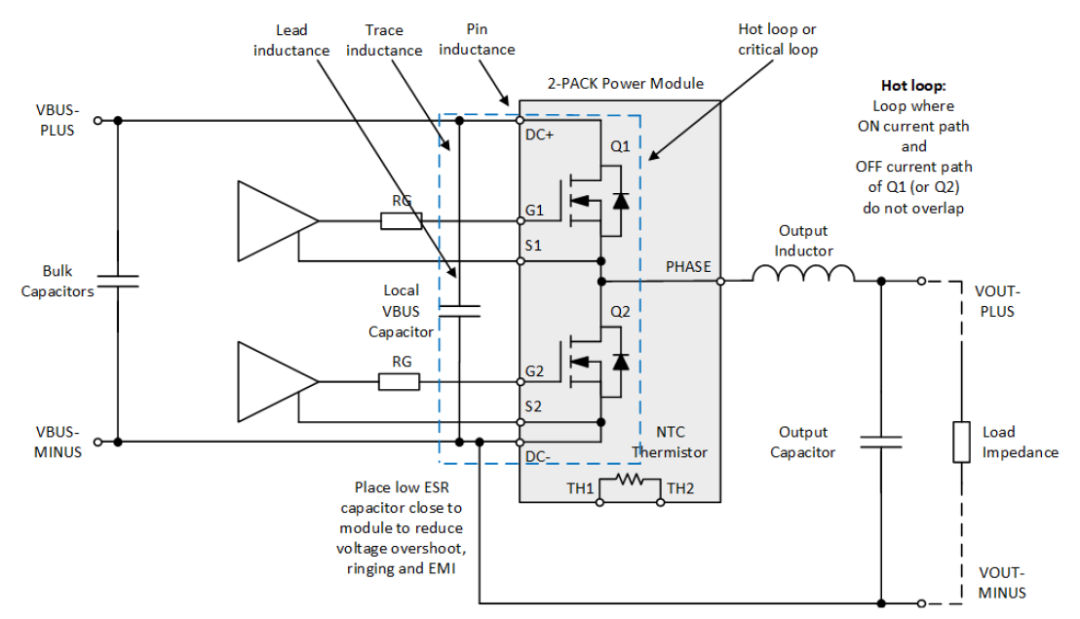

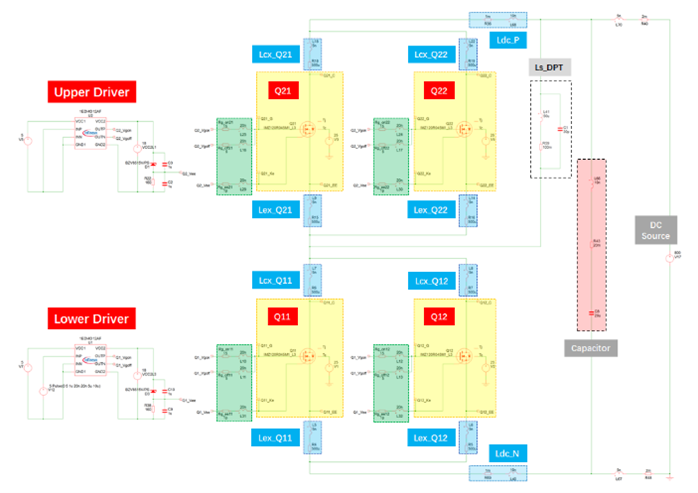

為了表征安森美 M 1 SiC MOSFET 的動態特性,使用了一個 20 m 的半橋模塊,其中兩個 40 m 器件并聯。圖 10 說明了測試設置。

圖 10:動態特性測試設置框圖

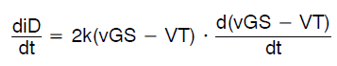

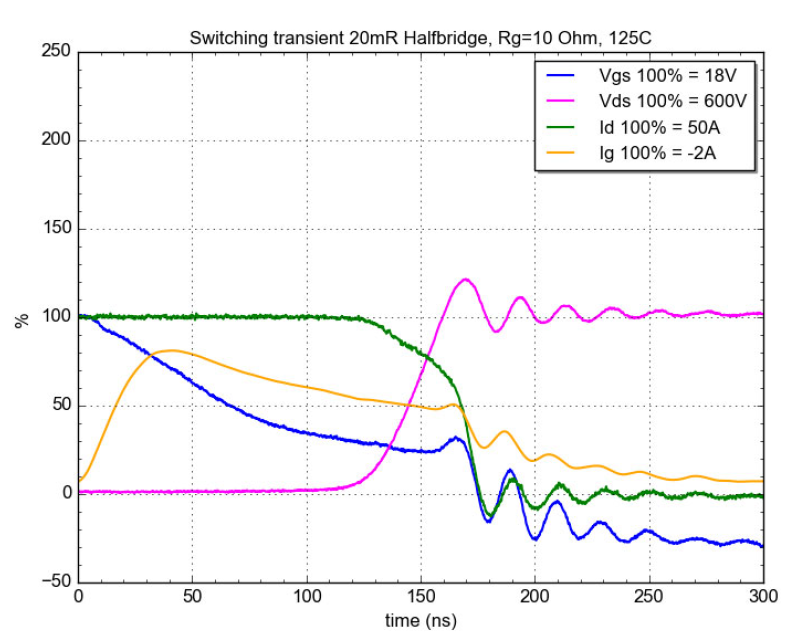

圖 11 顯示了上述測試設備的導通波形。品紅色曲線是低壓側 MOSFET 的漏電壓。綠色曲線是通過低壓側 MOSFET 的電流。

如果柵極驅動器在時間 t = 0 時被切換到 18 V,則切換序列開始。在初始緩升之后,柵極驅動電流起步很高,并隨著柵極電壓的增加而減小。柵極電壓升高,直至達到閾值電壓。電流增加,直至達到流過二極管的電流:負載電流+反向恢復電流+電容電流。

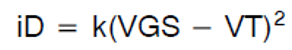

SiC MOSFET 的臺階電壓高度依賴于負載電流。在圖 11 中,臺階電壓約為 10 V。給定 ID 的 VGS 由以下公式得出。

因此,坡度將隨時間變化如下:

當柵極電壓隨時間呈近似線性變化時,di/dt 隨時間呈線性變化。由di/dt 隨時間呈線性下降引起的 Vds 壓降從電流達到閾值電壓時開始,到達到電流峰值時結束。

柵極電流和電壓達到臺階電壓。柵極電流為 QGD 充電,并且漏電壓降低到幾乎為零。

漏極電流向負載電流下降,并伴有一些振鈴。

最后,柵極電壓升高至 18 V。漏電壓降低至負載電流乘以 18 V 時的 R?DS(ON)?。

圖 11:20 mohm、1200 V 半橋模塊的導通波形

圖 12:SiC MOSFET 源極電流

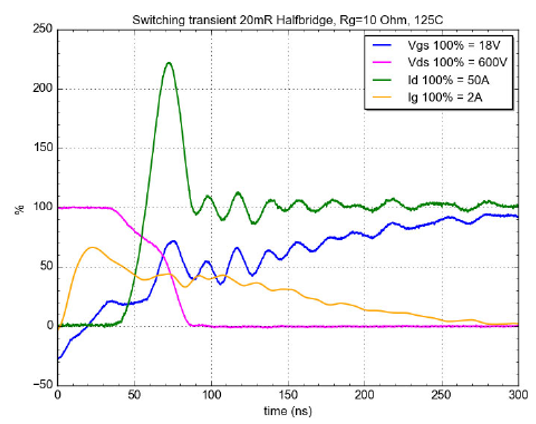

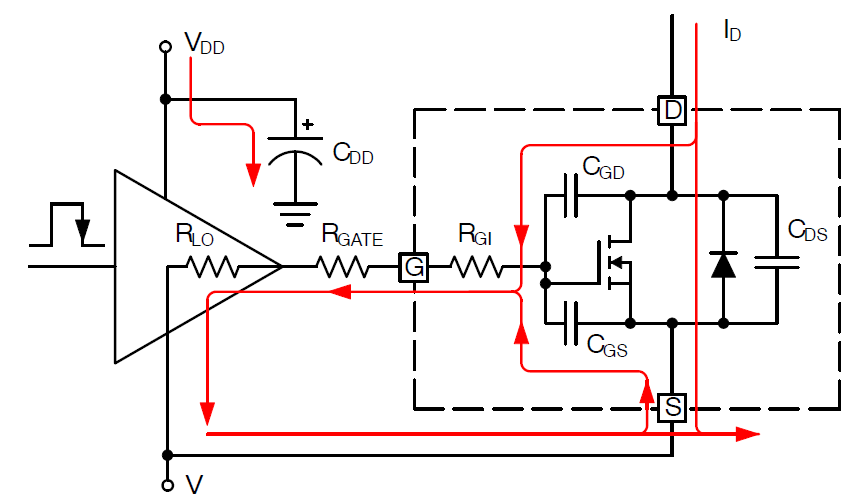

圖 13 顯示了使用兩個 40 mohm 器件的 20 mohm、1200 V 半橋模塊的關斷波形。

如果柵極驅動器在時間 t = 0 時被切換到 -5 V,則開關序列開始。在初始緩升之后,柵極驅動漏極電流起步很高,并隨著柵極電壓的增加而減小。柵極電壓下降,直至達到臺階電壓。由于沒有反向恢復電流,臺階電壓低于導通期間的電壓。QGD 放電時,電壓升高。一些漏極電流用于給非線性 COSS 電容放電,其在漏極電流中表現為負斜率。

柵極電壓過沖由電路中的回路電感引起:離直流總線最近的電容–模塊的直流+觸點–模塊的直流?觸點–回到直流總線電容。模塊和電容之間的連接應盡可能低電感,以最大限度地降低振鈴電壓。

當達到峰值電壓時,柵極驅動器將柵極從臺階電壓放電至閾值電壓,使電流降至零。柵極驅動器繼續給柵極放電,直至達到 ?5 V。

圖 13:20 mohm、1200 V 半橋模塊的關斷波形

圖 14:SiC MOSFET 漏極電流

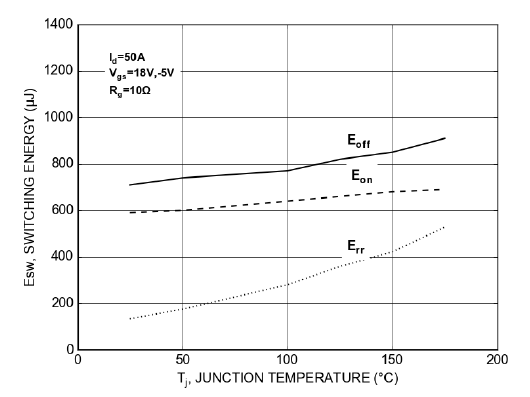

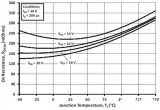

開關損耗隨溫度增加

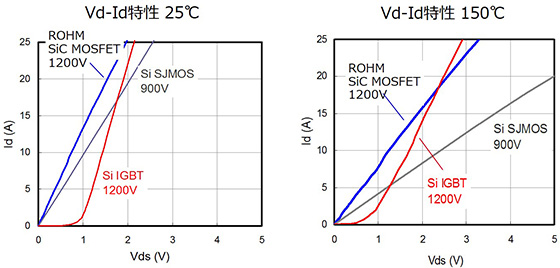

與靜態特性一樣,SiC MOSFET 的工作溫度將對開關性能產生影響。不過,如圖 15 所示,EON?和 EOFF?的溫度系數幾乎相同,150℃ 時的開關性能將非常接近 25℃ 時的特性。反向恢復損耗 (E?rr?) 卻非如此,其在 25℃ 時可忽略不計,但隨著溫度升高,它們可能會達到損耗計算應考慮的程度。因此,如前一章所述,考慮實際工作溫度下的參數至關重要,而不僅僅是 25℃。

在 Err?的情況下,值得注意的是,這些損耗的很大一部分是電容損耗,而不是 pn 結損耗。這些電容損耗看起來像示波器上的損耗,但不會導致體二極管發熱。這些損耗的影響和幅度取決于電壓和電流,但可能高達典型數據表中所示 Err損耗的 40%。因此,直接從數據表中獲取 Err?損耗是一種保守的方法。然后,在實際應用中,只能通過比較系統輸入功率和系統輸出功率來測量總損耗。

圖 15:20 mΩ、1200 V SiC MOSFET 模塊中的開關損耗與 Tj

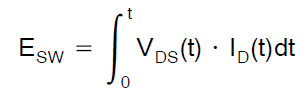

開關損耗隨漏極電流 (I?D?) 而增加

根據定義,MOSFET 的開關損耗是指任何開關事件期間電壓時間積分與電流的乘積。

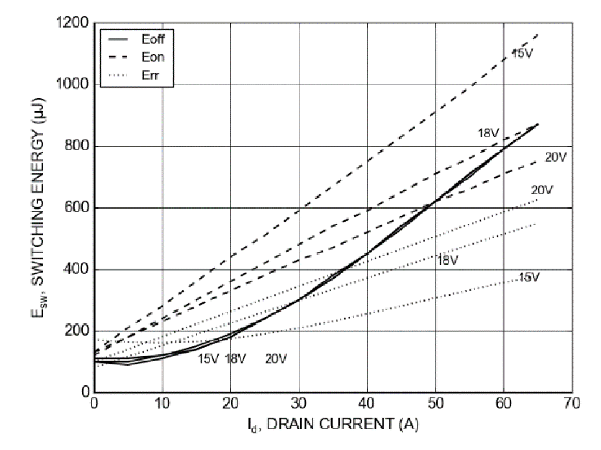

因此,預計損耗會隨著電流的增加而增加。但在將 M 1 1200 V SiC MOSFET 的行為與 IGBT 相比時,存在一些差異。如圖 16 所示,對于半橋配置的 20 mΩ、1200 V SiC 模塊,EON?與 ID?的關系是線性的,這些損耗將取決于換向回路中相應二極管的恢復。體二極管的恢復損耗也表現為線性模式。另一方面,EOFF?損耗從二次增長開始,直到它們也變成線性的某一點。

圖 16:20 mΩ、1200 V SiC MOSFET 模塊中的開關損耗與 ID?特性

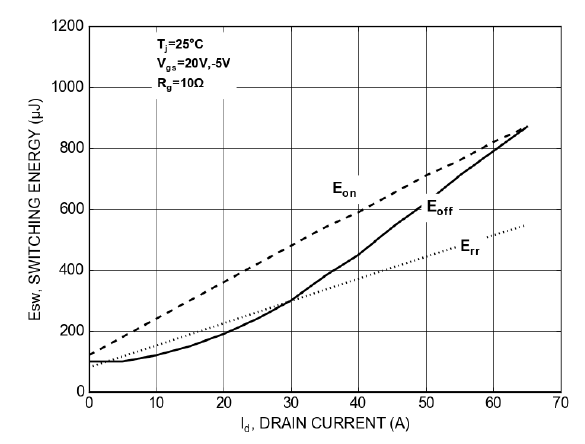

開關損耗與漏源電壓 (V?DS?)

如前一點所述,開關損耗的另一個直接因素是 V?DS?,在這種情況下,如圖 17 所示,E?ON?、EOFF?和 Err?以線性方式表現,但斜率不同。

圖 17:20 mΩ、1200 V SiC MOSFET 模塊中的開關損耗與 VD

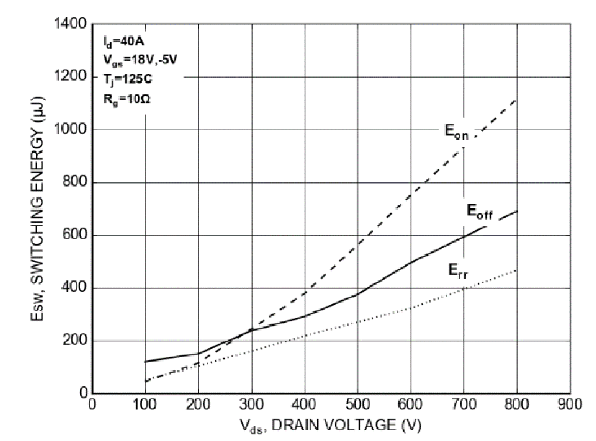

柵極電阻 (R?G?) 對開關性能的影響

開關器件通過外部手段實現的可控性是電路設計中的關鍵因素。在 MOSFET 或 IGBT 的情況下,盡管是電壓控制器件,但影響其開關行為的最常見方式之一是修改外部柵極電阻 R?G?,其中包括調節開關事件中涉及的不同電容的充電或放電速度。因此,會直接影響開關時間以及 di/dt 或 dv/dt。

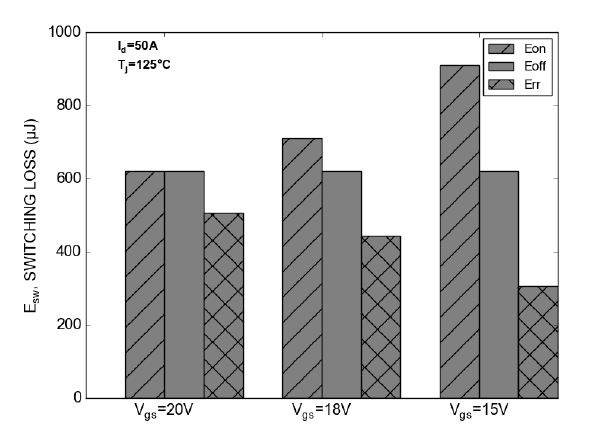

在第一階段,選擇適當的值時,需要考慮 RG?對損耗的影響。RG?較高將使器件速度變慢,從而導致 EON?和 EOFF?損耗增加。圖 18 顯示了 20 mΩ、1200 V SiC MOSFET M 1 模塊中開關損耗與 RG?的關系。RG?較高的積極影響是 Err?損耗減少,這是因為 MOSFET 體二極管在較慢的開關速度下表現更平滑。

但是,這不能補償導通和關斷損耗的增加。

圖 18:20 mΩ、1200 V SiC MOSFET 模塊中的開關損耗與 RG

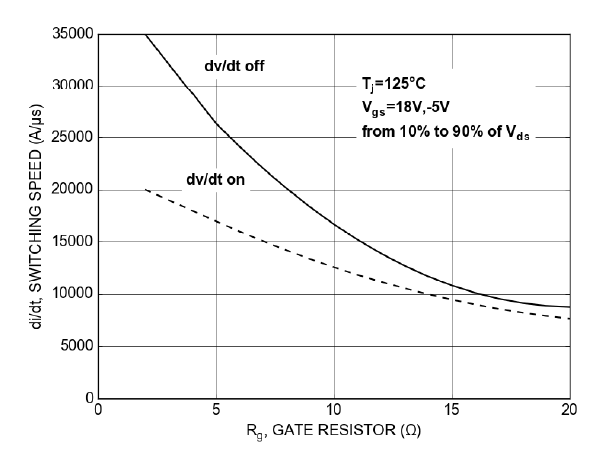

結論顯而易見,應盡可能降低 R?G?。另一方面,任何電路的寄生電感和電容都可能導致臨界電壓過沖或振蕩,如果器件太快打開,會產生潛在的電磁干擾 (EMI),這不僅涉及主電流換向路徑,還涉及柵極電路。此外,在某些應用中,出于安全原因,dV/dt 可能受到限制。因此,器件的速度必須能夠通過 RG?或最終的柵極電容 (C?G?) 輕松調節,但不建議使用后者,因為它可能會在柵極中造成嚴重的振蕩。圖 19 顯示了在使用安森美 M 1 SiC MOSFET 的 1200 V、20 mΩ 半橋模塊中 RG?對 dV/dt 的影響。此圖顯示,RG 的修改使用戶能夠對 dV/dt 產生強大的影響,從而使開關行為適應電路和應用的要求。通過這種方式,每個用戶都能輕松為自己的應用找到開關損耗和開關速度之間的最佳平衡。

圖 19. 20 mΩ、1200 V SiC MOSFET 模塊中 RG?的 dV/dt 可控性

VGS?對開關損耗的影響

在本應用筆記的第一章中,討論了 VGS?對安森美 M 1 1200 V SiC MOSFET 靜態特性的影響。結論是,至少在 + 18 V 的電壓下使用該器件,高達 + 20 V 的電壓更佳。如果現在正在考慮開關性能,則結論將是相同的。圖 20 顯示了開關損耗與 VGS?的相關性。EOFF?與正 VGS?無關:在圖中,三條 EOFF?曲線重疊。另一方面,VGS?將對 EON?和 Err?行為產生重大影響。如果 VGS?增加并且使用相同的 R?G?,則電流給 CGD?和 CGS充電。結果導致器件開關變快,從而減少 EON?損耗,這對 Err?的影響正好相反,因為速度加快將在相反 MOSFET 的體二極管中引起更高的恢復損耗。

圖 20:20 mΩ、1200 V SiC MOSFET 模塊中正 VGS?對開關損耗的影響

如果考慮總損耗,如圖 21 所示,在 VGS?較高時,EON?損耗的減少會過度補償 Err?的增加,能夠更有效地在較高 VGS?下開關器件。當然,還應考慮其他因素,如 EMI 或 dV/dt。

圖 21:20 mΩ、1200 V SiC MOSFET 模塊中不同正 VGS?的總損耗

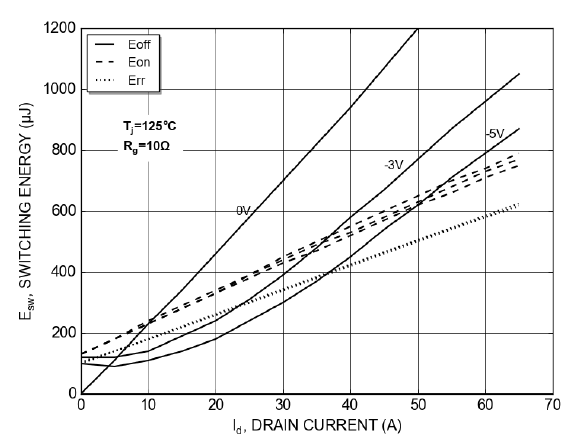

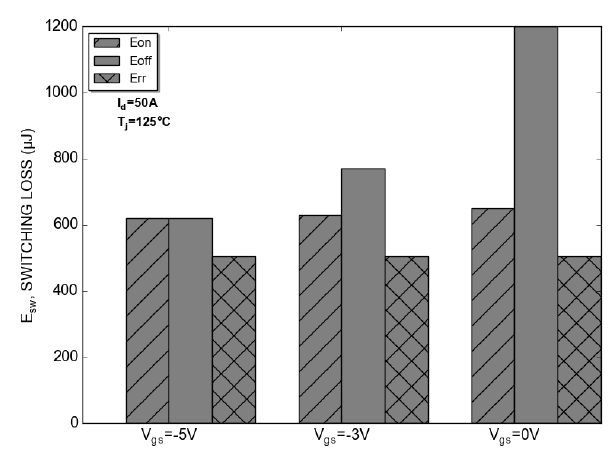

考慮到負柵極偏壓,之前強調了在體二極管應導通期間使用負電壓完全關閉溝道的重要性。這也會對開關損耗產生影響。如圖 22 所示,雖然負柵極電壓對 EON?或 Err?損耗幾乎沒有影響,但 EOFF?損耗可能會受到嚴重影響。盡管 – 5 V 和 ?3 V 之間的差異約為 25%,但如果使用 0 V 負柵極偏壓,則 EOFF?損耗可能會翻倍。

圖 22:20 mΩ、1200 V SiC MOSFET 模塊中負 VGS?對開關損耗的影響

在圖 23 中也可以觀察到這種影響,其中顯示了總損耗。

圖 23:20 mΩ、1200 V SiC MOSFET 模塊中不同 VGS?的總損耗

圖 23:20 mΩ、1200 V SiC MOSFET 模塊中不同 VGS?的總損耗

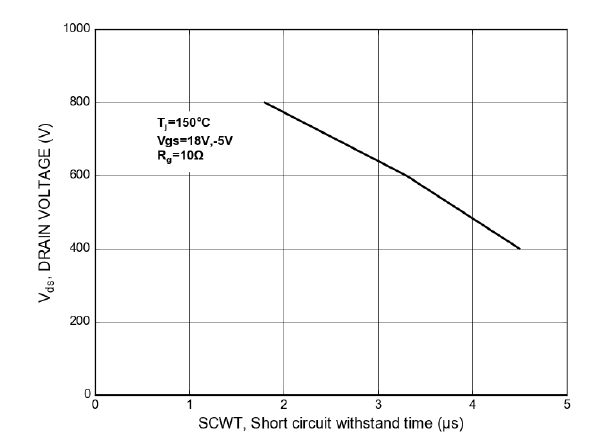

短路耐受時間 (SCWT)

在一些應用中,SCWT 是挑選器件時需要考慮的一個重要要求。不過,此特性也會帶來一些影響。SCWT 較長會對靜態和動態性能產生影響。因此,在許多器件中,為了獲得更好的性能,會忽略此特性。

安森美 1200 V M 1 SiC MOSFET 留有一定的設計裕度,以提供短路耐受能力。器件能夠在短路中存活的時間取決于許多因素,最重要的因素是 VDS 和設備可能遭受短路事件的參考溫度。與本應用筆記中討論的許多其他參數一樣,必須在合適的溫度下看待這些特性,雖然 125℃ 和 150℃ 之間的差異不大,但 SiC MOSFET 的 SCWT 在 25℃ 時可能會明顯更好。為了提供常見工作溫度的相關數據,本文選擇了 150℃ 的起始溫度。圖 24 顯示了不同 VDS?的典型 SCWT。

重要提示:這些是典型的參考值,無法保證一定會實現,請參考數據表中的值或聯系您當地的技術支持人員。

圖 24:20 mΩ、1200 V 半橋 SiC MOSFET 模塊中的短路耐受時間

圖 25 顯示了 20 mΩ、1200 V SiC MOSFET 模塊在 150℃ 時的實際測量短路行為。

圖 25:20 mΩ、1200 V 半橋 SiC MOSFET 模塊中的短路行為

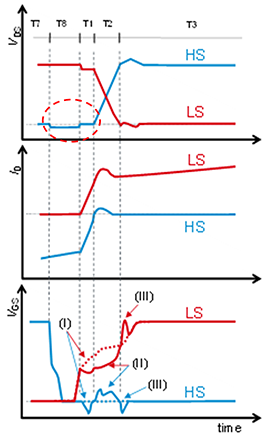

體二極管的動態特性

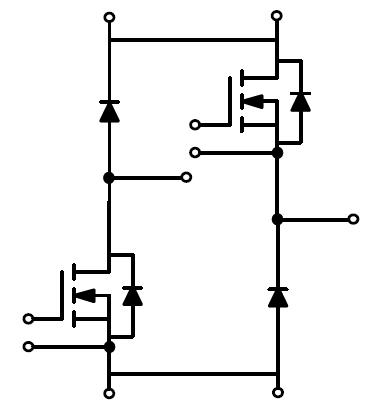

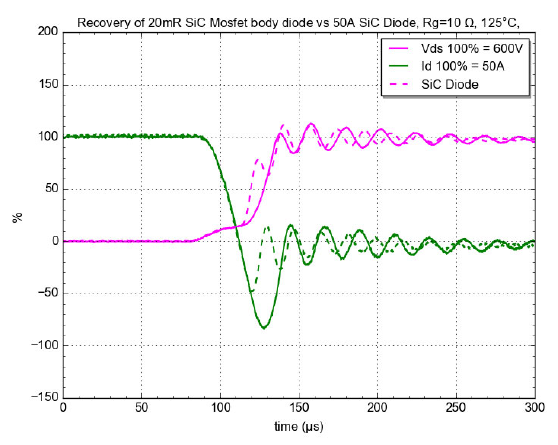

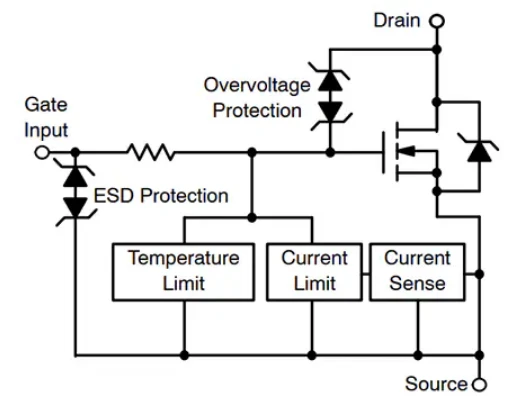

如前幾章所述,即使不建議使用傳導損耗較高的 SiC MOSFET 體二極管,這也不能總是避免。改善總損耗的一種可能性是激活 MOSFET 的溝道以改善靜態行為,但這對動態性能的影響微乎其微。另一種方法是采用與 SiC MOSFET 并聯的外部 SiC 二極管。不過,為了完全禁用體二極管,應將其與半橋的主換向路徑去耦,如圖 26 所示。

圖 26:具有拆分輸出的半橋

這種拆分不僅引入了額外的 SiC 二極管,而且增加了布局的復雜性。比較外部 SiC 二極管與體二極管的動態行為,如圖 27 所示,可以看出外部 SiC 二極管確實改善了反向恢復行為。但這種改善可能微不足道;特別是考慮到部分體二極管損耗無耗散。因此,用戶需要考慮在成本和復雜性都相應增加的情況下添加此附加組件是否值得。

圖 27:外部 SiC 二極管(虛線)與 SiC MOSFET 體二極管(實線)的恢復行為

在電源模塊內添加緩沖電容的影響

任何設計中的雜散電感都將在器件的開關性能中發揮關鍵作用,不僅在效率方面,而且還會導致不必要的行為,例如振鈴或高壓過沖。考慮到 SiC 器件主要用于快速開關應用,雜散電感產生不必要影響的風險變得更高。因此,在任何設計中,都要首先保持寄生電感盡可能低。盡管如此,即使是最有經驗的設計人員也無法避免封裝固有的某些寄生和所需的最少 PCB 布線。

圖 28 顯示了標準半橋配置關鍵開關回路中主要組件的示意圖。為了縮短臨界回路的長度,應盡可能靠近模塊放置低 ESR 電容。但是,這不會阻止回路中包含引腳電感、PCB 跡線和電容引線。

圖 28:具有外部電容的半橋模塊示意圖

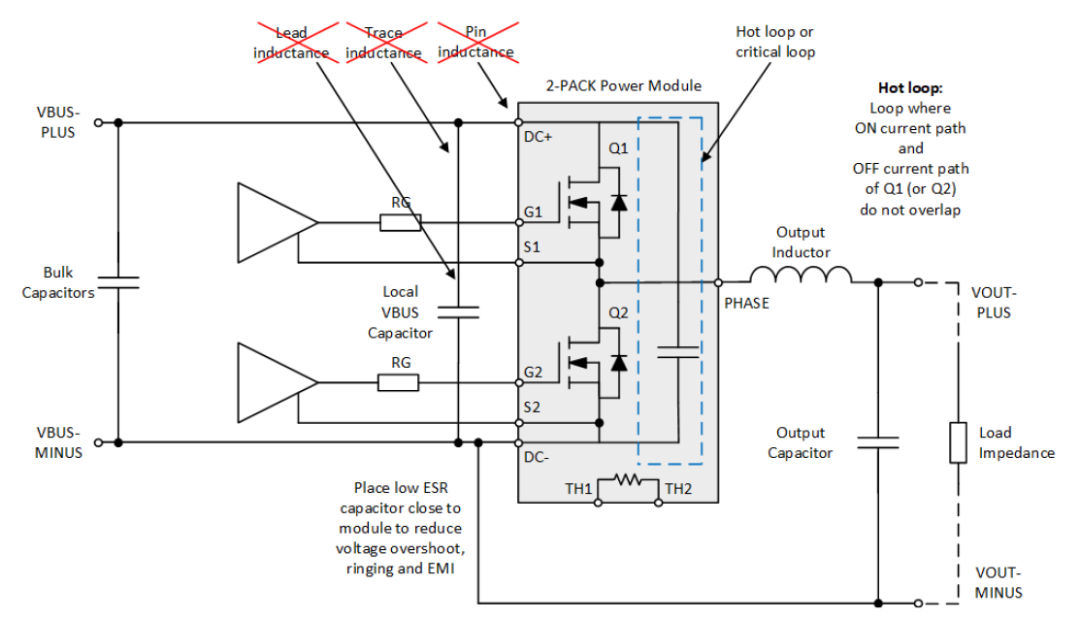

為了進一步縮短臨界回路的長度,可以在模塊內部集成一個額外的電容。如圖 29 所示。這樣,通過在一定程度上消除引腳、跡線和引線電感的影響,我們可以進一步減小寄生電感。集成電容的尺寸受到模塊內部可用空間的限制,例如,本研究使用了 100 nF 電容。

圖 29:具有集成電容的半橋模塊示意圖

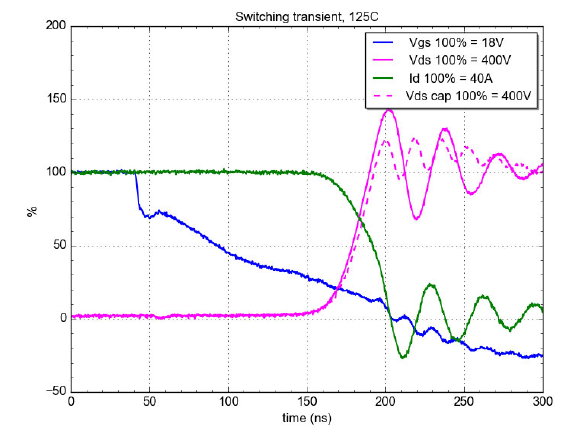

減小臨界回路電感將能改善開關行為。首先,如圖 30 所示,關斷時的電壓過沖可從近 150% 降至 120%。

圖 30:具有集成電容與外部電容的半橋關斷行為

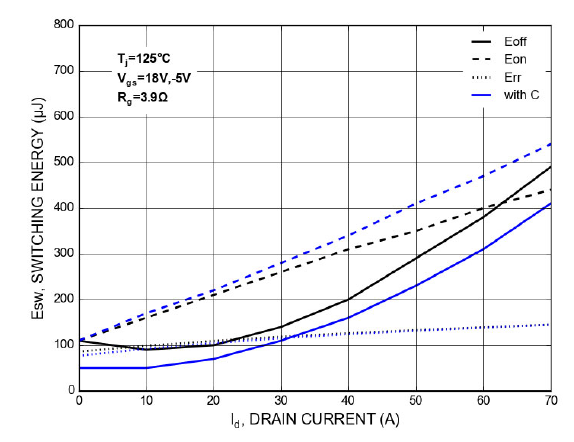

如圖 31 所示,電壓過沖減少的直接后果是 Eoff?損耗減少。另一方面,隨著電流的增加,Eon?損耗可能會增加。在任何情況下,從總損耗來看,器件的公共電流能力都有所提高。

圖 31:具有和沒有集成電容的開關損耗

審核編輯:劉清

電子發燒友App

電子發燒友App

評論