目錄

PN結

MOSFET基礎

TFT器件可靠性

UISL基本制程工藝(65nm)

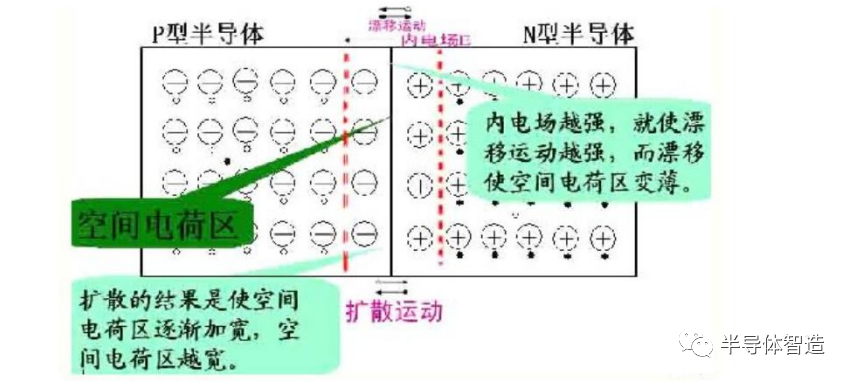

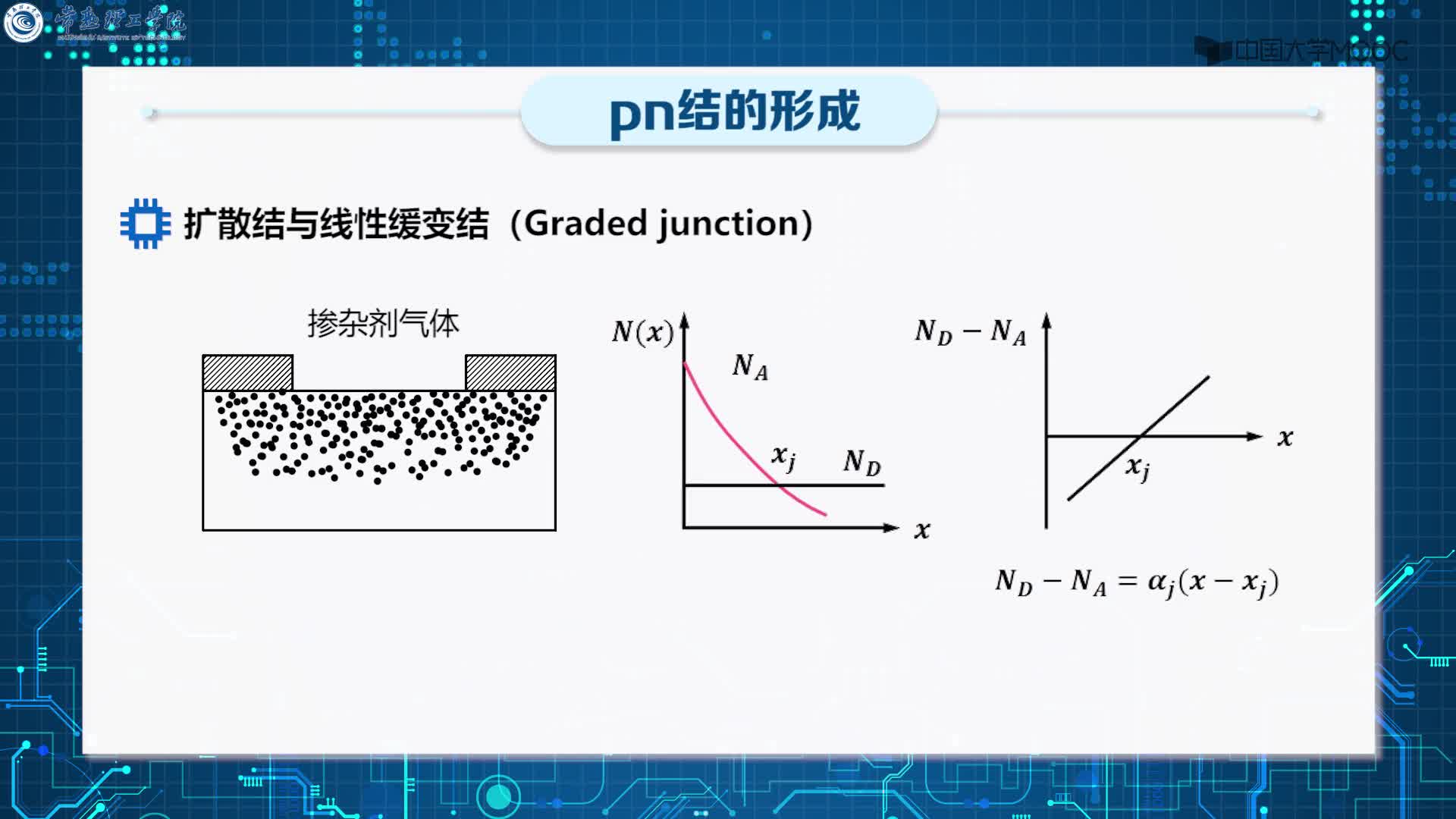

1.PN結如何形成

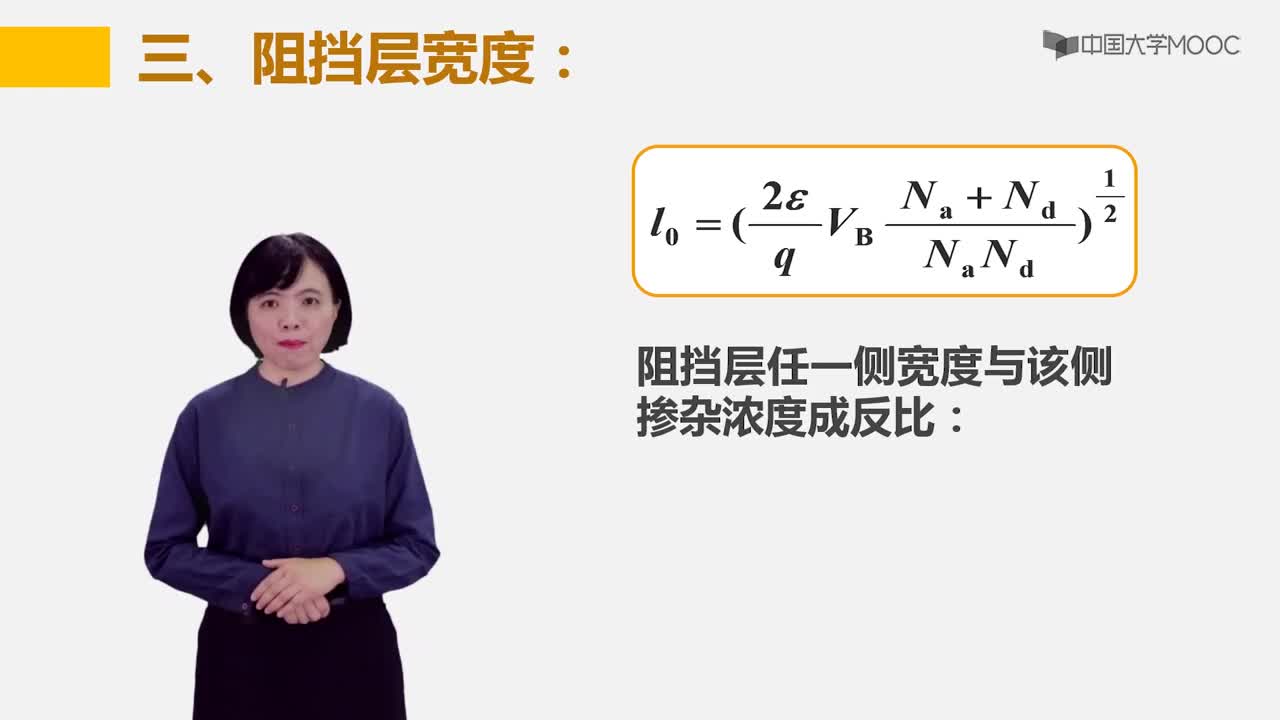

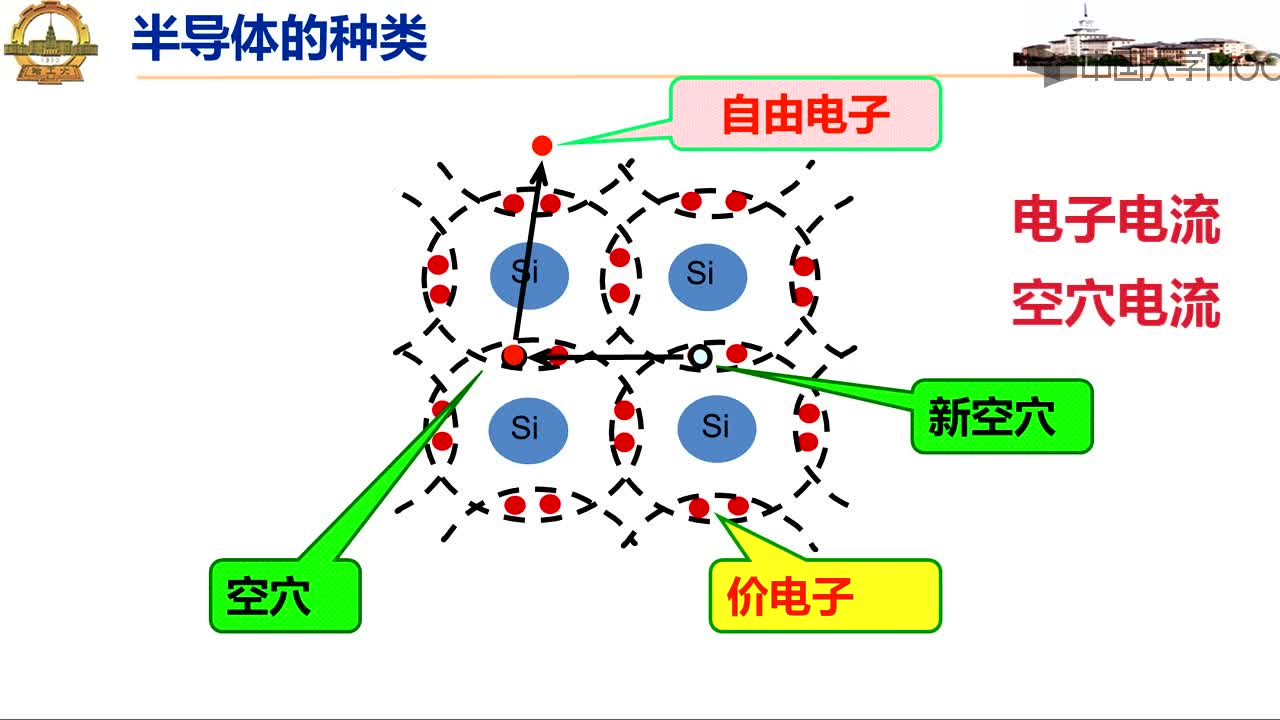

當n型半導體與p型半導體接觸時,電子與空穴都從濃度高處向濃度低處擴散,稱為擴散運動。當電子進入p型區域,空穴進入n型區域后,即與對方多子復合,留下了固定不動的原子核。這些原子核形成了一個內建電場,使電子與空穴向反方向漂移。這兩種運動達到平衡時的結果就是形成一段沒有載流子的區域,稱為空間電荷區,也叫耗盡層。這個空間電荷區叫做PN結。

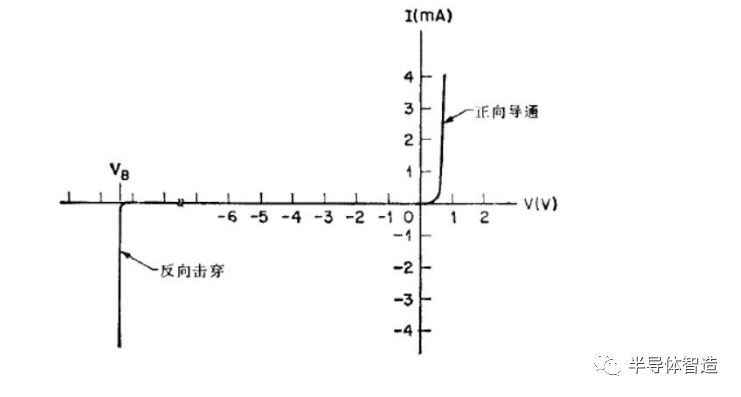

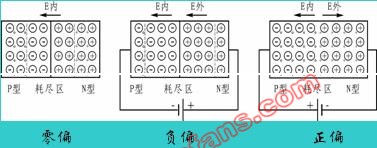

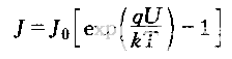

PN結的伏安特性

當PN正向偏置時,電流隨電壓的增大而迅速增大。當反向偏置時,電流很小且隨電壓增大變化不大,但是當電壓達到臨界點時電流突然增大。這兩種現象稱為正向導通與反向導擊穿。

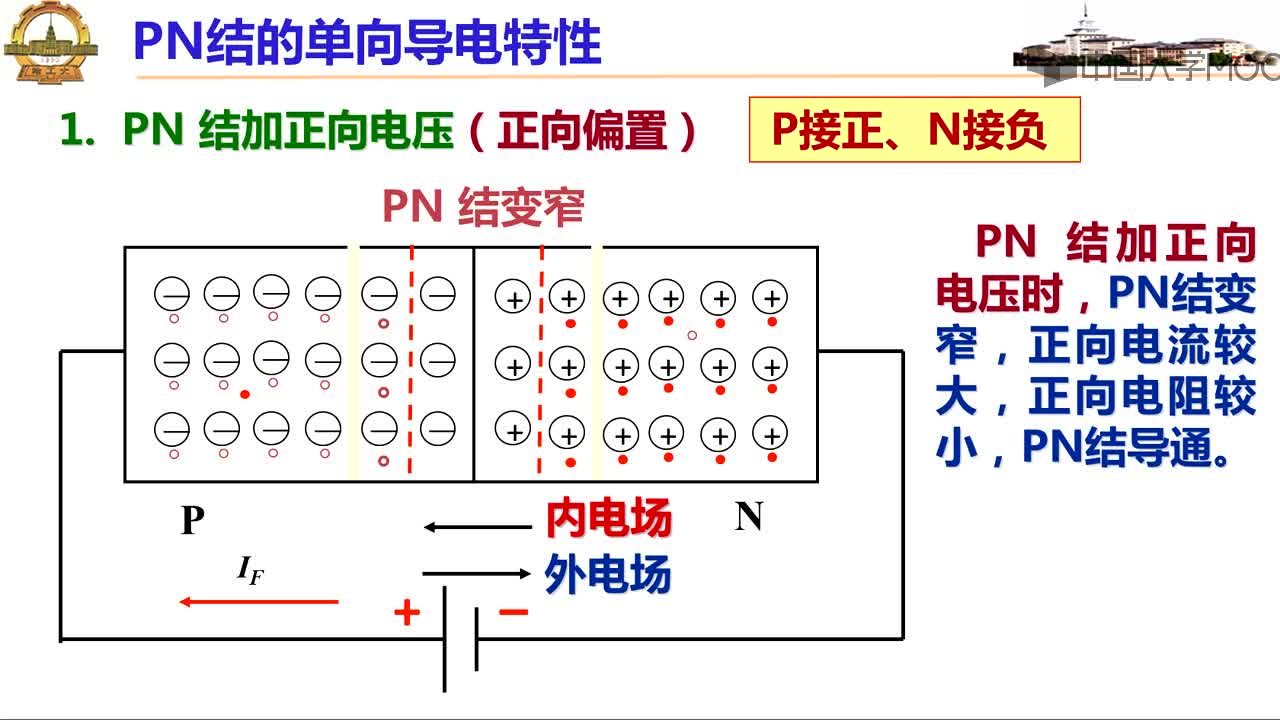

正向與反向偏置的定義:P型半導體電位高于n型半導體電位,稱為正向偏置。反之為反向偏置。

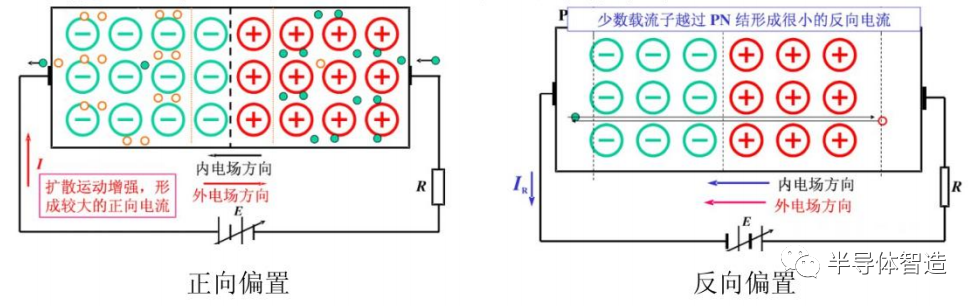

PN結的伏安特性的解釋

當PN結正向偏置時,外部電場從P型指向N型區,使得空穴和電子都向界面處運動。因此耗盡層厚度變窄,電流上升。同理反向偏置時耗盡層變寬,阻礙電流的通過,因此電流隨電壓變化很小。

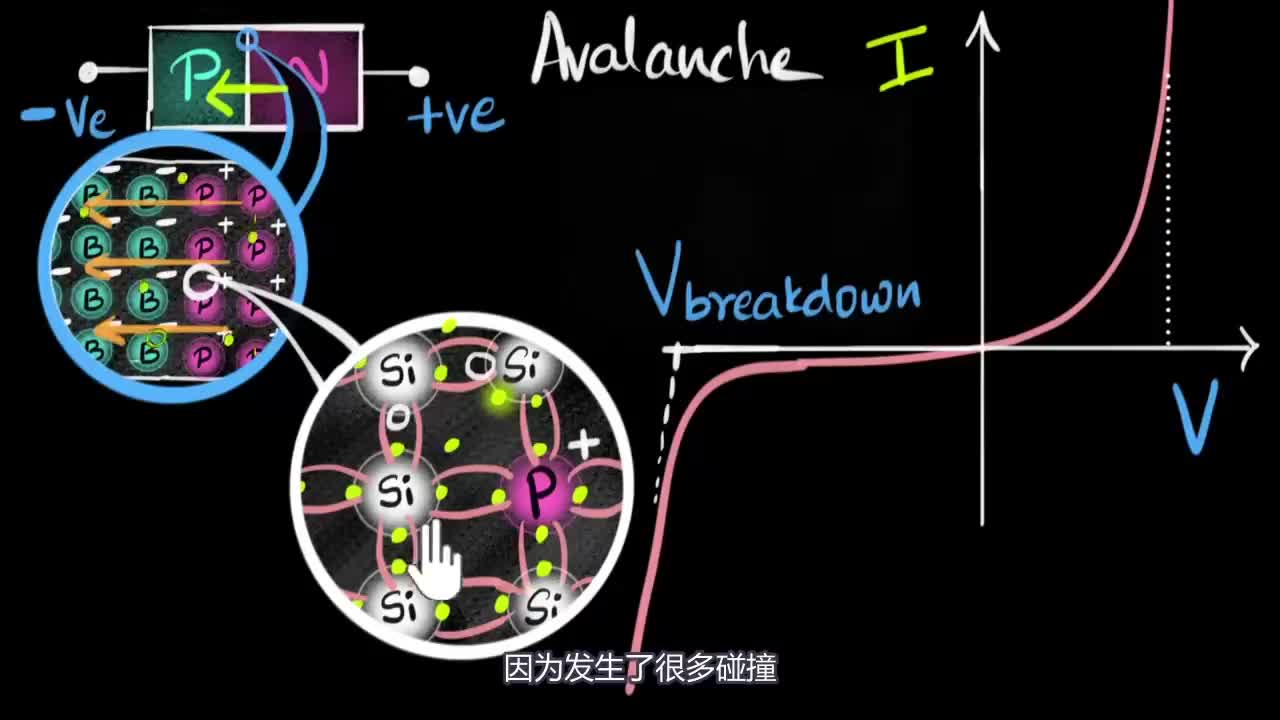

? 當反向電壓達到一定強度時,PN結電流急劇增大,稱為反向擊穿。這時的電壓叫擊穿電壓。反向擊穿的模式有了兩種

齊納擊穿:發生在高濃度摻雜,耗盡層很窄時。此時耗盡層內電場強度高,能夠破壞共價鍵結構形成電子-空穴對。(E>1MV/cm)

雪崩擊穿:發生在中低濃度摻雜,耗盡層較寬時。電子在電場中獲得能量,如果電場強度足夠大,電子與晶格碰撞后就可以破壞共價鍵,產生電子-空穴對。產生的電子和空穴又與晶格碰撞生成新的電子-空穴對。該過程稱為雪崩倍增。(E~0.2-0.6MV/cm)

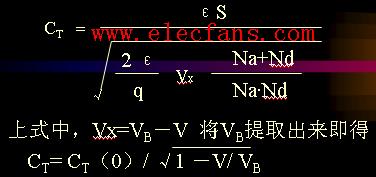

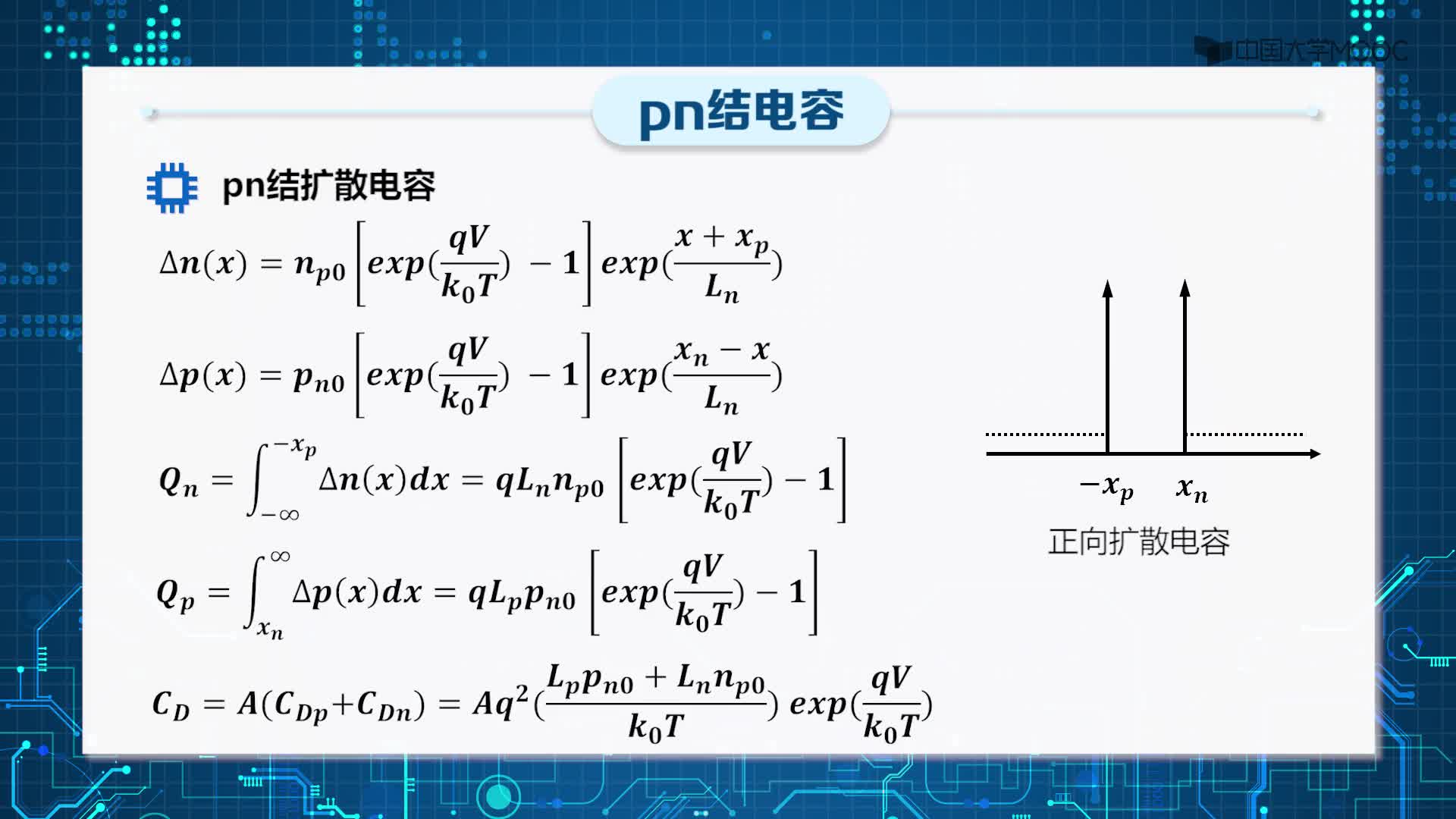

PN結電容

PN結電容分為兩部分:勢壘電容和擴散電容

PN結負偏壓時,耗盡層寬度隨電壓變化,空間電荷區的電荷數量也隨之變化。電壓向負方向變化時耗盡層變寬,空間電荷增加,相當于充電,向正方向變化則耗盡層變窄,電荷數量減少,相當于放電。該電容稱為勢壘電容,它是由多子變化引起的。

PN結正偏時,P區和N區分別向對方注入空穴和電子,這些載流子在對方體內稱為非平和少數載流子。當電壓變化時,在PN結兩側的少子數量發生變化,相當于對電容進行放電。該電容稱為擴散電容,它是由少子變化引起的。負偏壓時由于平衡少子數量少,該電容忽略不計。而且由于少子壽命的限制,高頻下擴散電容不起作用。

由此可見PN結電容并不是一個固定值,它隨外電壓的變化而變化。

2.MOSFET及相關器件

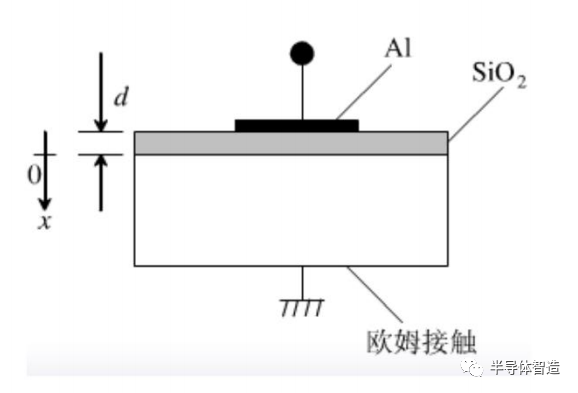

MOS二極管是MOSFET的基礎,在電路中也被用作電容。它是研究半導體表面特性最有用的器件之一。

理想MOS二極管的結構圖如下圖所示。d為氧化層厚度,V為金屬電極上的電壓。定義金屬電極上電位高于體電位時為正偏壓。

MOS二極管特性

當MOS管施加正或負偏壓時,在Si表面有電子或空穴積聚。為討論方便,以下以P型半導體為例進行說明。

當MOS管為負偏壓時,Si表面積聚了比體內更多的空穴,此時為積累狀態。

當偏壓由負轉正時,空穴被排離表面而作為少子的電子則被吸引到表面。電子與空穴復合的結果是表面載流子濃度較少直至消失,硅表面出現耗盡層,此時為耗盡狀態。

正偏壓繼續增大時,表面的電子濃度超過了空穴濃度從而形成一個自由電子層,這個電子薄層稱為反型層。此時為反型狀態。

繼續增大偏壓,反型層厚度隨之增加。

N型半導體依此類推。

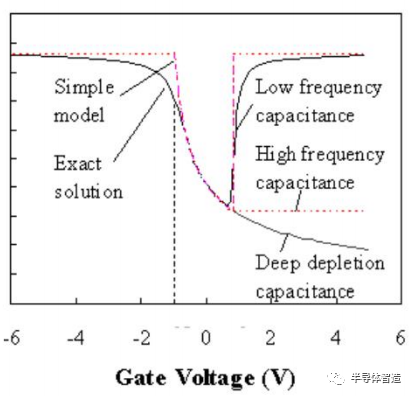

MOS二極管電容

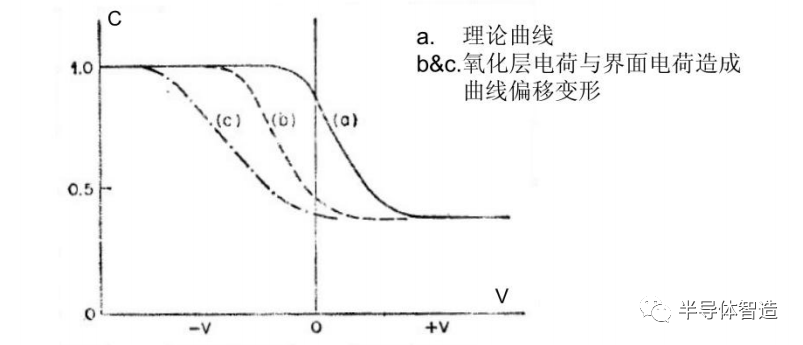

MOS二極管本質上是一個電容器。與理想電容器不同的是,它的下極板是半導體,因此MOS電容并不是一個定值,而是隨柵極偏壓而變化的。下圖是P-Si MOS二極管的C-V曲線

當Vg為負時,硅表面為P型,測得的電容即為柵氧化層的電容。當Vg向正移動時,硅表面的空穴逐漸減少而電子逐漸增多,在表面形成耗盡層且耗盡層不斷變厚。因此電容逐漸下降。當耗盡層達到最寬,即將出現反型時電容達到最小值。反型后由于反型層中電子對電場的屏蔽,耗盡層寬度不再變化,因此電容值不再改變。

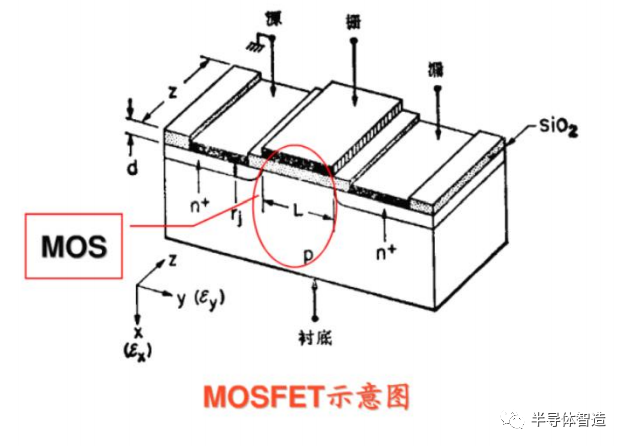

MOSFET基本結構

MOSFET全稱Metal-Oxide-Semiconductor Field Effect Transistor.MOS表示器件的基本結構,FET表示器件的工作原理。

MOSFET伏安特性

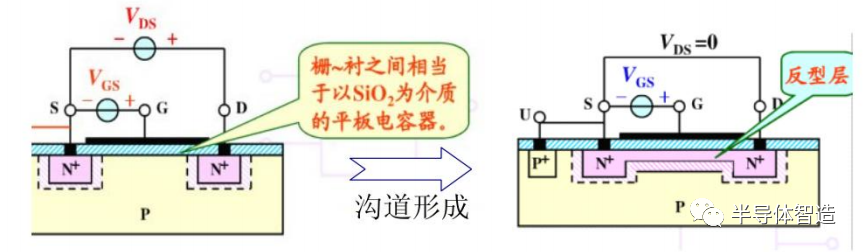

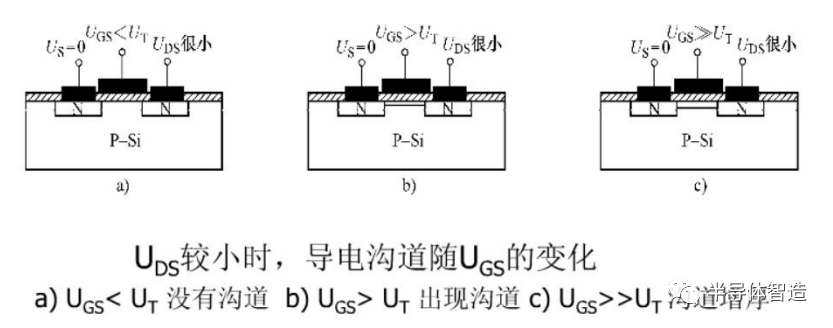

MOSFET是在MOS二極管的基礎上加入了源漏兩端構成的。源漏兩端的摻雜是和溝道區相反的,從而構成了兩個背靠背的PN結。在柵極無偏壓時,從漏到源只有很小的PN結反向漏電流。當柵極上加電壓時,源漏電流會隨之有明顯變化。因此叫場效應管。 MOS管源漏電流主要受柵極電壓和漏極電壓的控制。下面以NMOS為例說明電流和柵極電壓與漏極電壓的關系。

MOSFET轉移特性 ?

隨著柵極正偏電壓逐漸增大,硅表面電子逐漸增多最后形成一個N型的反型層。反型層與同為N型的漏源連通,形成導電溝道。這時如果給漏極加電壓,就會有電流流過。溝道從無到有時所需的柵極電壓VG定義為閾值電壓VT。

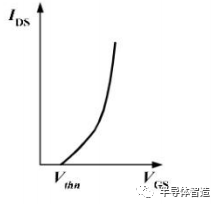

漏源電流Ids隨柵極電壓Vg的變化如下圖

當VG

當VG>VT時, 溝道開啟且溝道厚度隨VG增大而變大。因此lds隨VG增大而迅速增大。

當VG略小于VT時, Ids隨VG呈指數關系變化。這一小段區間稱為亞閥值區域。

VG增大到一定程度時,lds增加幅度變小。

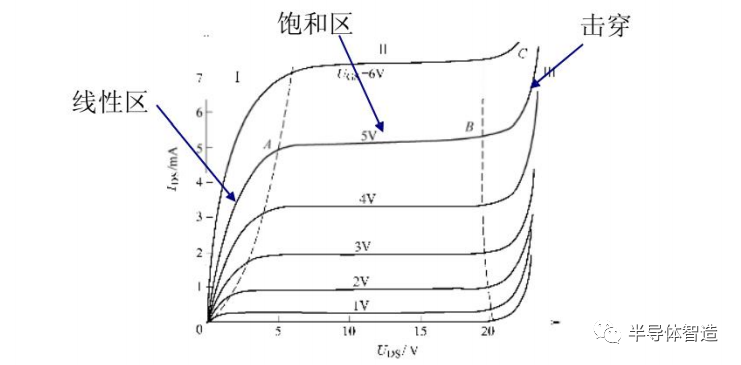

MOSFET輸出特性

當VG

當VG>VT時,溝道形成,有較大的電流通過且電流隨Vd增大而增大。(線性區)

當Vd增大到一定程度時,ld變化趨于飽和。( 飽和區)

Vd繼續增大,電流將急劇上升。(擊穿)

線性區

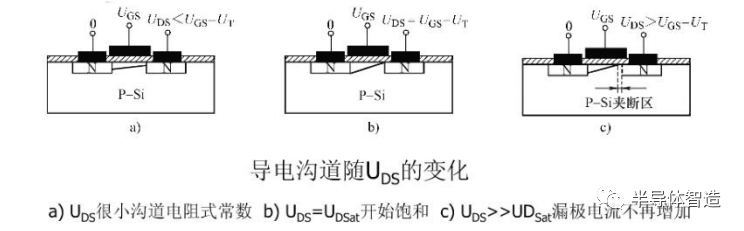

在MOS二級管中,反型層的厚度是均勻的。但是在MOSFET中,當Vds不為零時,在反型層中沿著溝道方向的電位是不均勻的,造成柵氧化層兩端的電壓并不等于Vg。結果是溝道的厚度從漏極到源極是不一致的。

當Vd較小時,溝道厚度的這種不一 致不會帶來大的影響,MOS管呈現電阻特性。反映在Id-Vd曲線上就是線性區。 ? ?

飽和區

溝道在漏極一端的電位近似于Vd,柵極與溝道內的真正電位差為Vg-Vd.而在源極一端。因為多數情況下源極電位為零,電位差即為Vg。所以從源極到漏極溝道厚度逐漸變窄。當Vd逐漸增大,直到Vd=Vg-VT時,溝道消失。這種現象稱為夾斷。

在夾斷發生后繼續增大Vd,夾斷區擴展而有效溝道長度變短。增加的電壓幾乎全部落在夾斷區上,所以Id變化不大。對應的Id-Vd曲線進入飽和區。

夾斷區的導電原理:在夾斷區耗盡層與柵氧化層接觸,載流子數量非常少。但是從源區注入的電子會在強電場的作用下被拉到漏極,這就是夾斷區的導電方式。

MOS管擊穿

當VD繼續增大時,MOS管被擊穿,電流急劇增大。主要有兩種擊穿方式:

雪崩擊穿。實際上就是漏極和襯底的PN結擊穿。

漏源穿通。漏極的耗盡層隨Vo增大而變寬,當漏極耗盡層與源極耗盡層連通時,源極的電子注入并被耗盡層中的電場拉到漏極。產生漏電。

實際的MOSFET電容C-V曲線

與MOS二極管不同,MOSFET的柵氧化層電容在高頻與低頻測試條件下呈現不同的CV曲線。

高頻測試時,其曲線在負偏壓部分和理論值基本相同。在反型層出現后,電容并不像理論上那樣保持在最小值,而是進一步下降。這是因為半導體進入深耗盡狀態,原因是少子的產生需要定時間,如果測試信號的頻率過高,少子產生速度會跟不上振蕩頻率,從而使得感應電荷數量減少,電容值變小。

低頻測試時,負偏壓部分的曲線無變化。當反型層產生后,少子的產生速度可以跟上測試信號變化,因此電容又迅速變大,直至和負偏壓時基本相當。

對于薄膜晶體管這樣的三 端器件,其C-V曲線又有所不同。

為什么需要LDD

熱載流子就是具有較高能量的載流子。

當S/D重摻 雜時,耗盡層寬度窄而其中的電場強度高。部分電子會獲得足夠高的能量然后在與晶格碰撞時產生新的電子空穴對,并形成正反饋產生更多的電子-空穴對。這些新產生的電子空穴對都是載流子,因此造成飽和電流增加(kink effect),和可靠性變差(進入GI或破壞界面處的Si-H鍵)。LDD即在重摻雜漏極與溝道之間插入一個輕摻雜漏極,這樣耗盡層寬度增加,降低熱載流子發生率。

耗盡層寬度增加的另一個好處就是降低漏電流(Ioff)但是相應的代價是開態電流(lon)下降。

NMOS的hot carrier比PMOS嚴重, 這是因為NMOS的載流子是電子,而電子的有效質量約為空穴的一半。

討論:影響器件特性的因素

LTPS制程回顧

影響實際VT的因素有哪些0影響實際lon的因素有哪些

影響loff的因素有哪些

影響μ和SS的因素有哪些

LTPS工藝對器件參數的影響

LTPS制程中制造的MOS管與以上論述的標準MOS管最大的不同在于LTPS的器件是在一層多晶硅薄膜中制造的,因此它是一個三端器件(無襯底引出)。由此造成的結果是體電位受柵極電壓和漏極電壓影響而不固定。盡管如此,很多情況下薄膜晶體管的伏安曲線還是接近標準MOS管的,影響器件特性的工藝也基本相同。但LTPS有個獨有的氫化工藝,其對TFT影響非常大。該工藝的目的是將氫摻入多晶硅中,與多晶硅體內的懸掛鍵形成Si-H鍵來修補晶格缺陷。氫化效果的好壞對所有的晶體管參數都有影響。除此之外,各項參數的主要影響因素如下:

VT: 主要受溝道區摻雜濃度、柵電容、界面態與氧化層電容影響。III/V族元素污染和金屬離子污染也會顯著影響VT。Plasma Induced Damage也會有很大影響。

lon: 主要受溝道區摻雜濃度、柵電容、LDD/SD濃度及Overlay的影響。多晶硅晶粒大小,表面粗糙度及界面態也是主要影響因素。此外還有Gate和polyCD。

loff: 主要受溝道與LDD/SD雜質濃度及分布影響: Gate CD和LDD/SD

Overlay會有較大影響。柵氧化層厚度不均勻或質量差時,柵極漏電也會是一個重要分量。對于沒有LDD的晶體管,GIDL也很重要。

SS:結漏電、柵電容、溝道反型層電容。

U:溝道摻雜濃度、LDD/SD濃度、柵氧化層的界面態、多晶硅晶粒尺寸。

等離子體損傷

等離子體在半導體加工工藝中十分常見,主要用于CVD、Dry Etch、 PR removal等。

在使用等離子體工藝對基板加工時,這些具有一定能量的離子會運動到基板表面,并與基板發生化學反應或者物理轟擊作用,從而對表面造成一定的損傷。這種損傷叫做等離子體損傷(Plasma Damage)。

等離子體損傷最為典型的就是對溝道區的硅晶格損傷導致VT漂移和遷移率下降。實例: ashing引起的Plasma Damage。

等離子體誘導損傷

等離子體工藝使用帶電離子對材料進行加工時,這些離子會將所攜帶的電荷傳遞基板。如果沒有釋放路徑,這些電荷會積累在基板表面,并隨著圖形的不同在各個區域建立不同的電位。

等離子體誘導損傷(Plasma Induced Damage,簡稱PID)特指這些積聚的電荷引起局部電位升高從而對器件造成了損傷。

實例: PV dry etch引起的PID

3.TFT器件可靠性的測量

為了推算TFT器件的壽命,通常在高溫和高電壓下對晶體管進行Stress測試,通過觀察一定時間后的器件特性變化情況來推算其壽命。

通常進行的測試項目有

TDDB (Time Dependent Dielectric Breakdown) 指柵極電壓小于擊穿電壓時,經過長時間的加壓而使柵絕緣層發生擊穿。測試方法為將電壓加至工作電壓的1.1-1.5倍,經過一段時間后測量柵極漏電的變化。

NBTI (Negative Bias Temperature Instability) PMOS在負偏壓情況下空穴與Si表面的Si-H鍵作用生成H原子進而產生H2擴散,而留下的Si懸掛鍵則使得Vth發生偏移。測試方法為加高溫、高柵極電壓后測量Vth的變化。

HCI (Hot carrie Injection) 熱載流子注入至GI膜內引起的Vth偏移。測試方法為加VD=VG=1.1-1.5工作電壓使TFT長時間處于導通狀態下后測量Vth和Ion變化。

Non-conductive HCI 晶體管處于截止狀態時的HCI效應。測試方法為加VD=1.1-1.5工作電壓而VG=0,一段時間后測量Vth和lon變化。

用于OLED驅動的TFT需要在帶負載和不帶負載(負載及發光單元)的情況下分別測量可靠性,并使用模擬實際顯示情況下的脈沖加壓法。

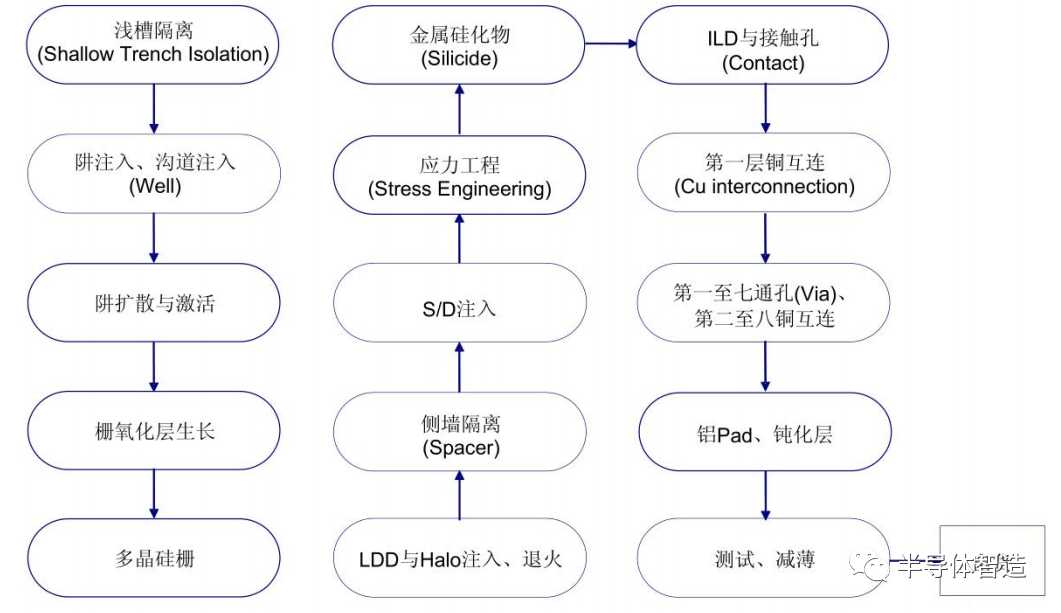

4.半導體邏輯器件工藝流程簡介(65nm)

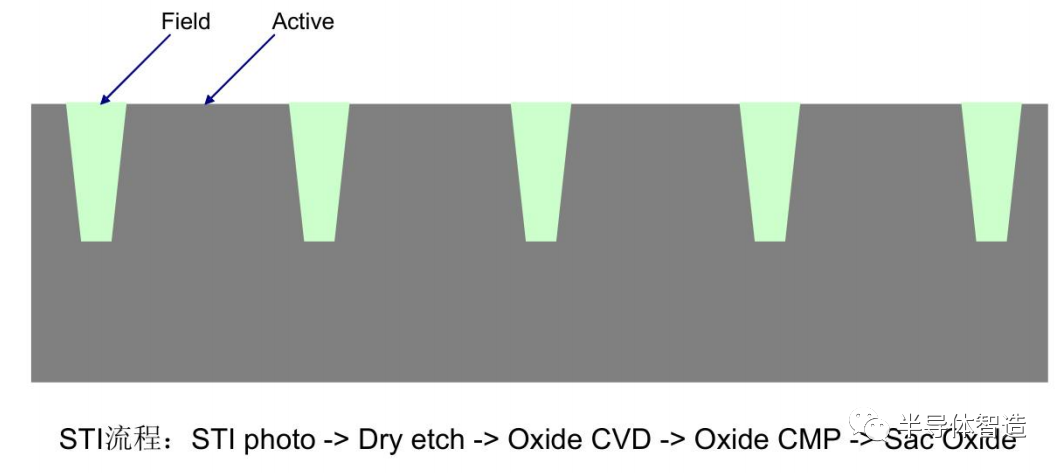

? Shallow?Trench Isolation

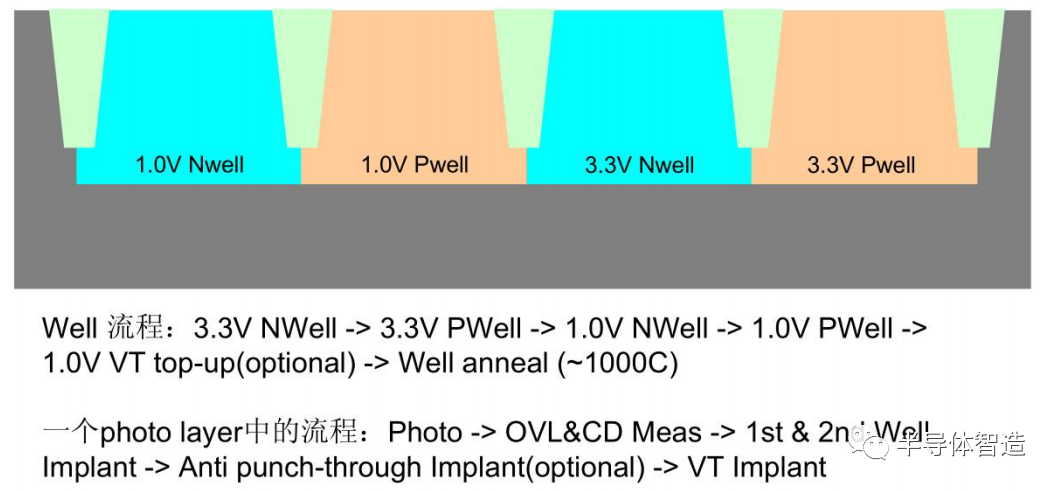

Well Formation

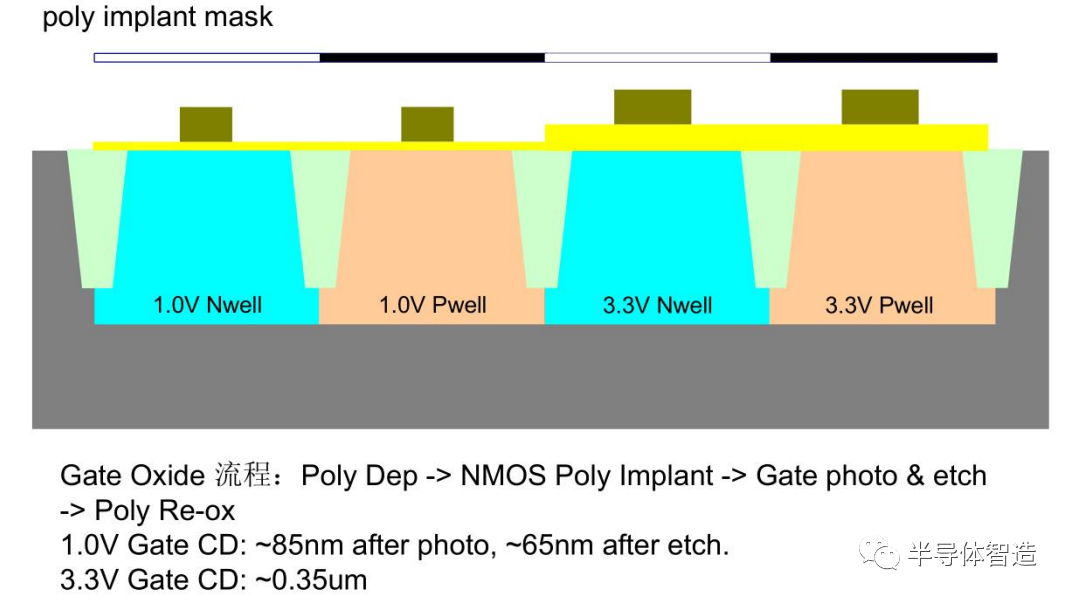

? Gate?Oxide

Poly Gate

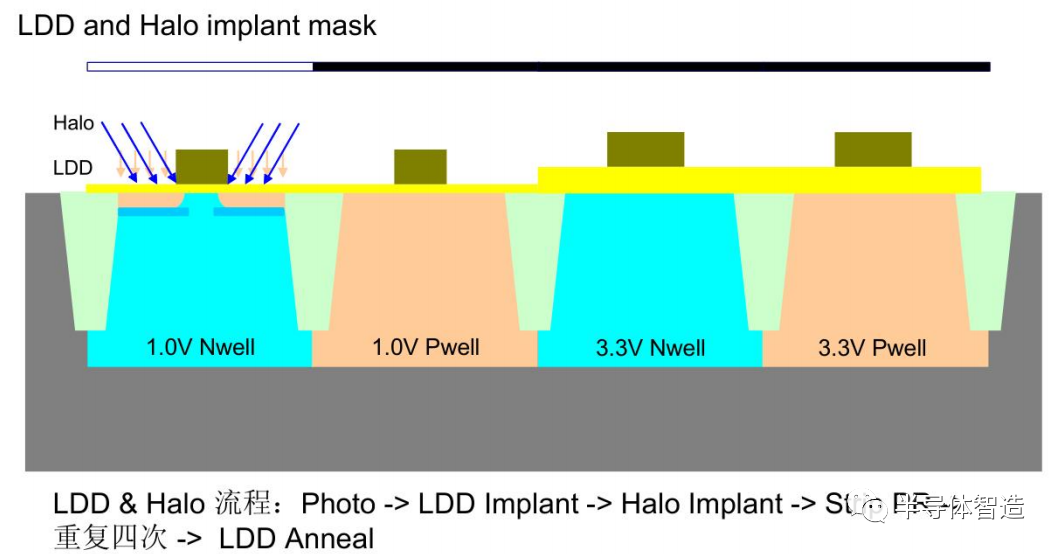

LDD?& Halo Formation

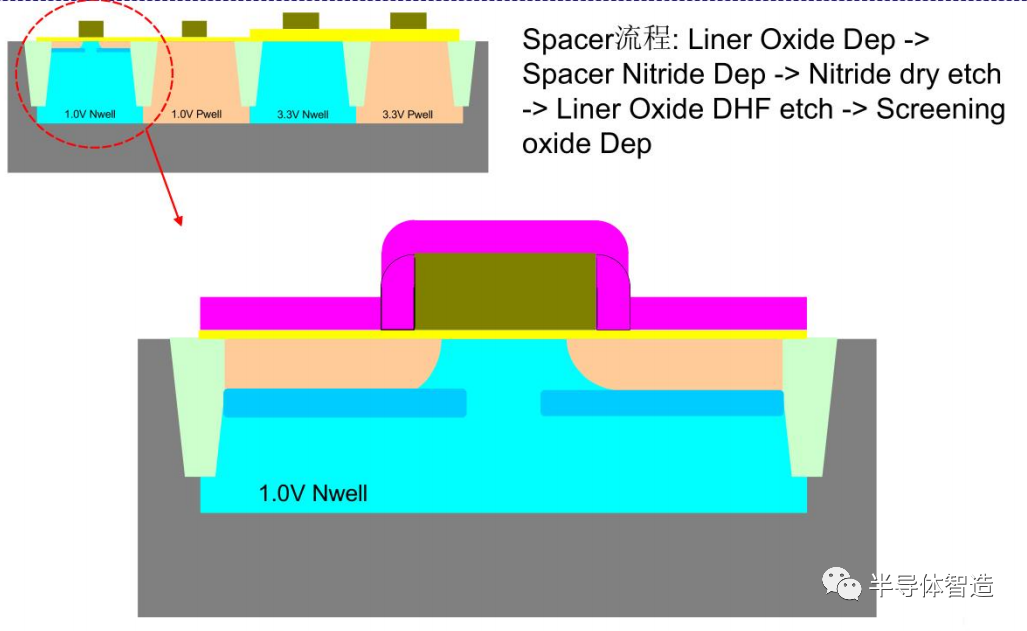

Spacer

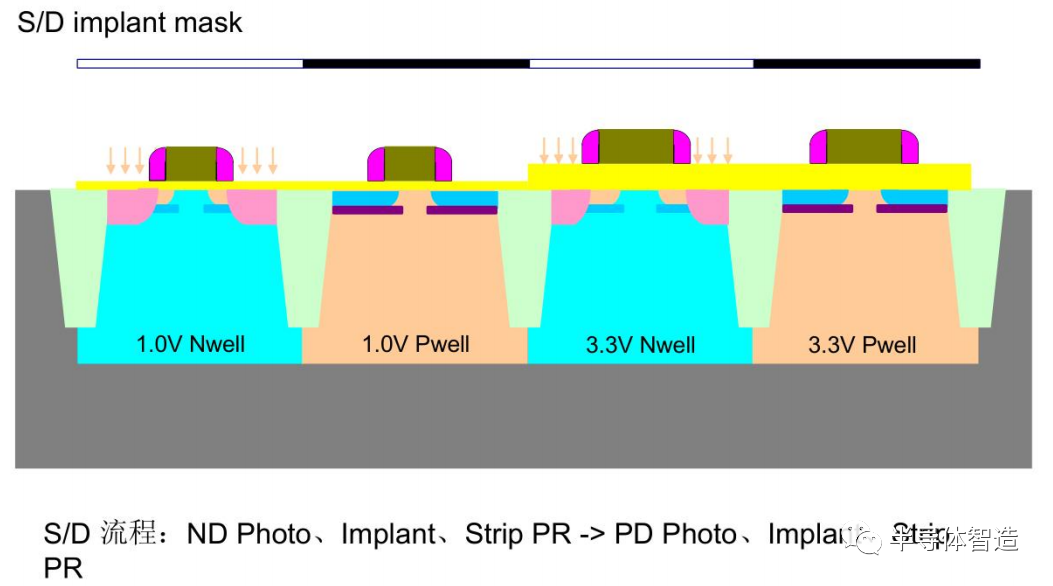

S/D?Formation

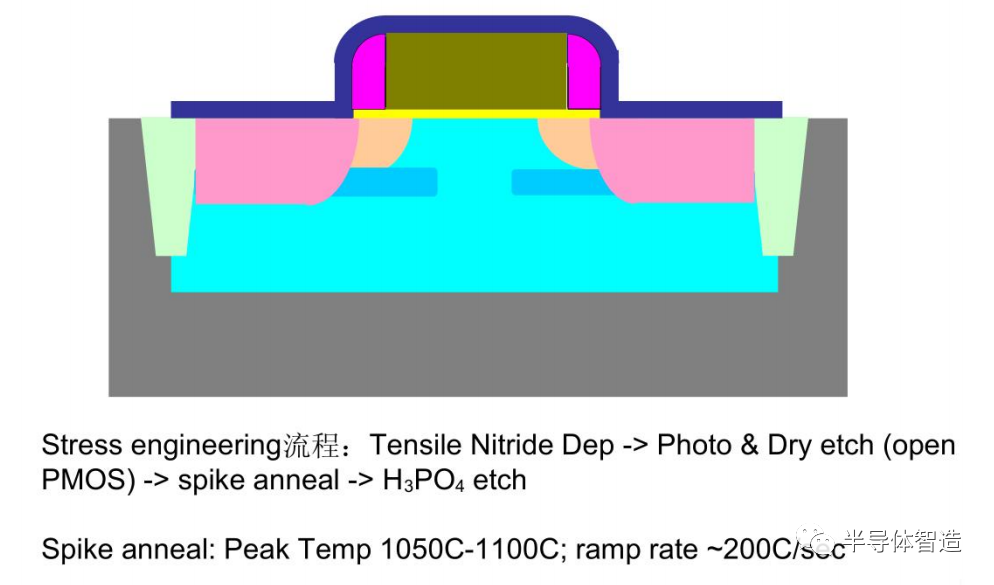

Stress?Engineering

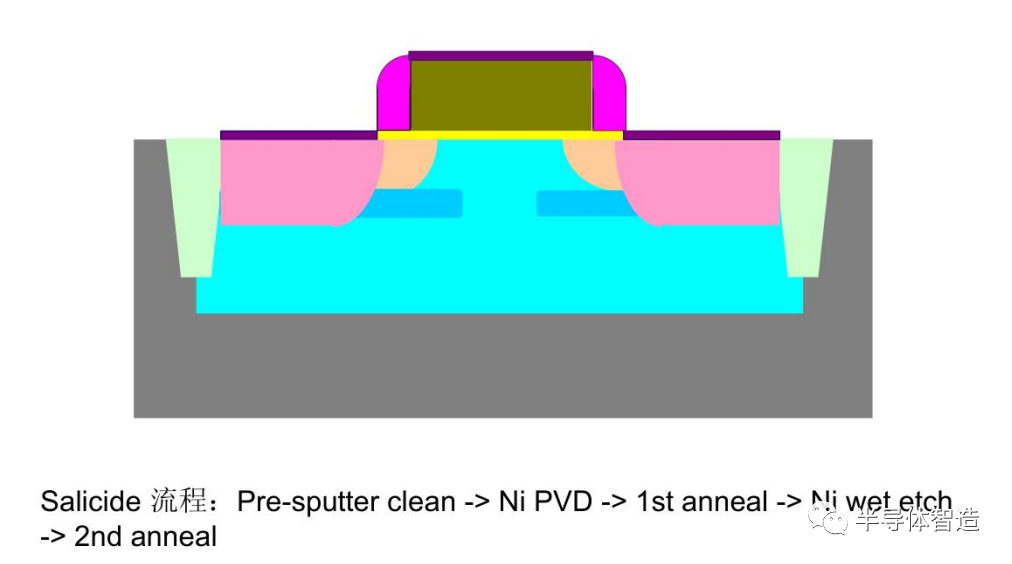

Salicide(Self-aligned?Silicide)

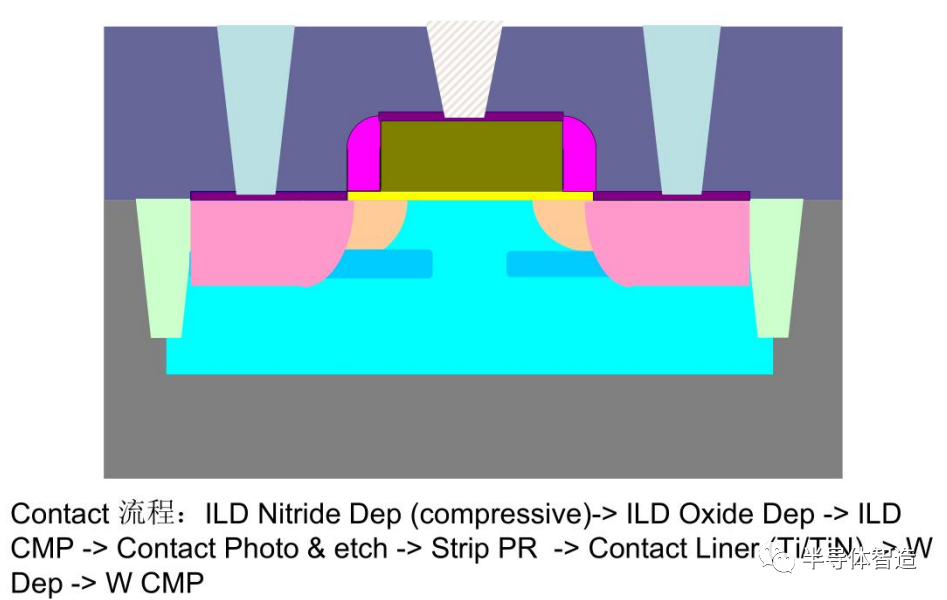

ILD?&?Contact

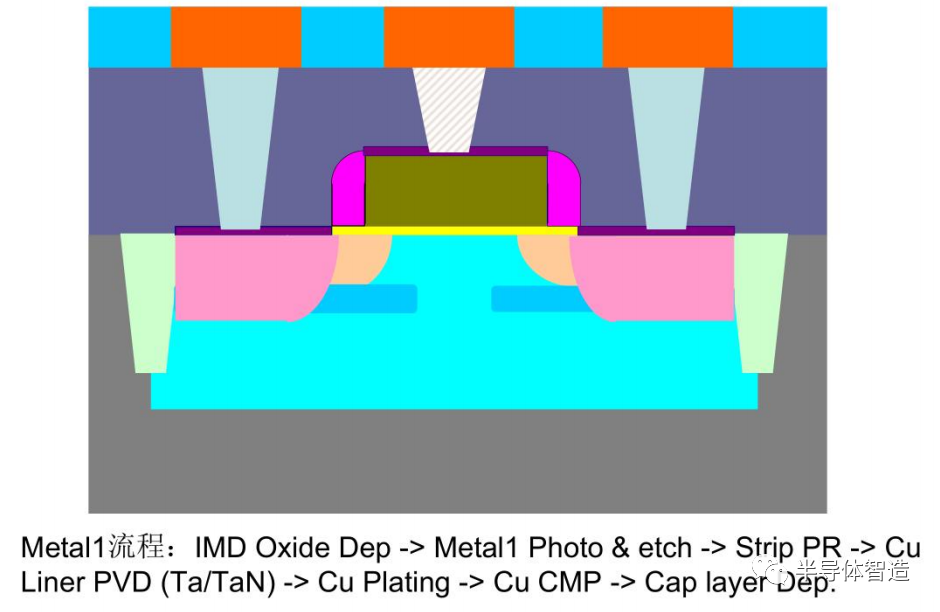

1st Cu Inter-Connection

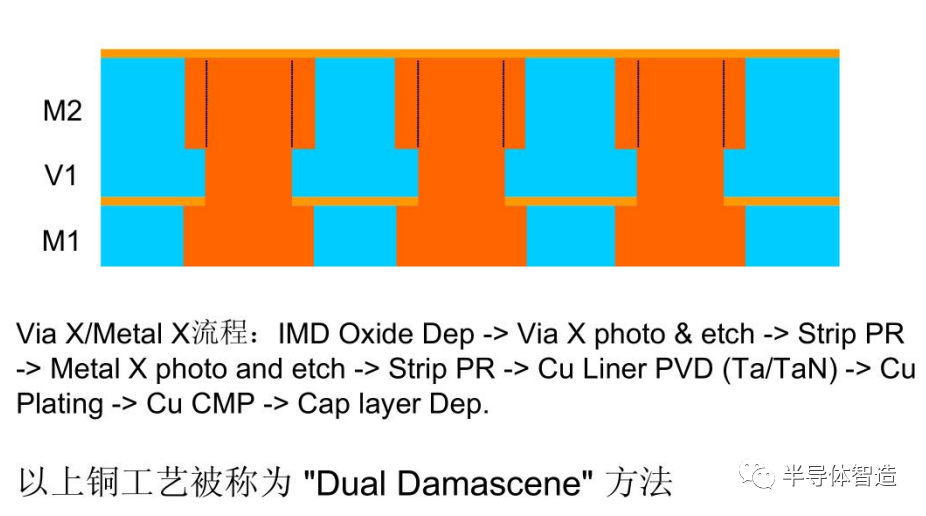

Via1/Metal2 and Above

來源:大話光纖傳感

審核編輯:湯梓紅

漏源電流lds隨漏極電壓Vd的變化如下圖

熱載流子效應(Hot Carrier)

電子發燒友App

電子發燒友App

評論