半導體產業面臨的挑戰日益嚴峻,我們該如何應對?

如果把晶體管比作糧食,我們可以參考解決糧食危機的方法,來說明應對芯片挑戰的三種思路。

第一,最直接的就是繼續提升主要糧食的單位面積產量,這對應于提高芯片中晶體管的密度,這被稱為“延續摩爾”(More Moore)。

第二,是擴展其他糧食種類,提高豐富程度,這意味著除了CPU、內存等數字芯片之外,還要大力拓展模擬、射頻、電源、顯示、柔性芯片等的用途,以及通過3D芯片將各種功能集成在一起,這叫作“擴展摩爾”(More thanMoore)。

第三,也是最長遠的,是開發全新的糧食品種,這對應于探索MOS場效晶體管以外的新型晶體管,例如碳納米管場效晶體管(簡稱CNTFET或CNFET)、阻變式存儲器(簡稱RRAM)、相變隨機存取存儲器(簡稱PCRAM)、隧穿場效晶體管(簡稱TFET)等,這條路徑叫作“超越摩爾”(Beyond Moore)。

01. “延續摩爾”

半導體業界繼續縮小晶體管尺寸,提高芯片里晶體管的密度,是“延續摩爾”路徑的主要目標。

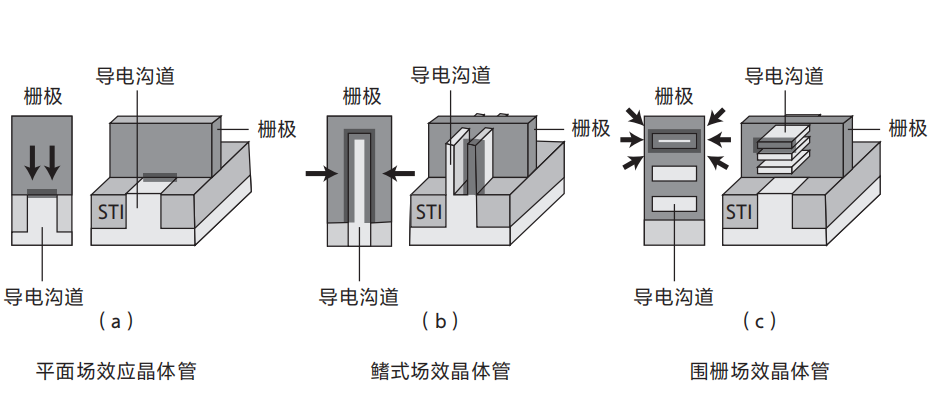

當工藝節點從5納米進到3納米和2納米時,FinFET遇到了一個老問題,晶體管無法有效關斷,漏電流飆升導致發熱嚴重。盡管FinFET已經變成了立體結構,可通過凸起的三個側面去關斷導電溝道,但仍無法完全關斷。

2003年,研究人員提出了更大膽的“納米線”(Nano-wire)結構。在這種結構中,晶體管的導電溝道變成納米粗細的一根“線”,完全被一個環形的“柵”給全方位地環繞,就好像一只“手”握著橡皮水管。在“手”上施加電壓,能更好地關閉晶體管,減小漏電流。

雖然這種結構解決了晶體管關斷的問題,但也對晶體管開啟后通過的電流大小造成了影響:細細的納米線對電流的阻礙作用極大。

為此,2006年法國原子能委員會電子與信息技術實驗室(CEA-Leti)的研究人員提出納米片(Nano-sheet)結構。這類晶體管又叫GAAFET(見圖14-3)。在這種結構中,連接晶體管開關兩側的不再是細細的“線”,而是薄而寬的“片”,這樣全包圍的結構更利于關斷晶體管,而多個薄而寬的片又提升了導電能力。2017年,IBM公司展示了這種堆疊的納米片晶體管。2021年5月,IBM公司采用納米片成功突破2納米技術節點,在一個指甲蓋大小的芯片上集成了500億個晶體管。

圖14-3 晶體管結構的演變

IRDS預測圍柵晶體管將用于3納米、2納米及以下的技術節點。三星公司準備在3納米技術節點時切入圍柵晶體管,而臺積電公司準備在2納米技術節點時遷移過來。

在隨后的1納米和0.7納米技術節點,單個晶體管的尺寸將再一次面對挑戰。IRDS預測那時業界將把水平放置的圍柵晶體管豎立起來,以進一步減小“占地面積”。再進一步,業界還可能將圍柵晶體管堆疊起來,做成3D結構。芯片將通過堆疊的方式繼續向上“生長”,就像一層層的空中花園,以便繼續提高單位面積可以容納的晶體管的數量。

盡管有了好的晶體管結構設計,但能否將其制造出來則又是另外一回事。

制造晶體管的最大瓶頸仍然是***。光源為193納米的浸沒式***可以加工的最小柵間距約為34納米。要知道,193納米的紫外光(經過水折射后變成134納米)本身無法用來加工這么小的尺寸,它需要經過多次曝光,分次加工線條的不同邊緣,才能達到所需的精度。

然而,加工尺寸越小,紫外光進行多重曝光所需的掩膜版數量也就越多,到了7納米技術節點就需要幾十層掩膜版。掩膜版越多,加工步驟越多,所花費的成本和時間也就越多。10納米工藝制造的晶圓比14納米工藝制造的晶圓貴了32%,而在7納米的技術節點又比10納米貴了14%。如果到5納米技術節點時再不采用下一代EUV***,光刻所需的步驟將達到100多步。

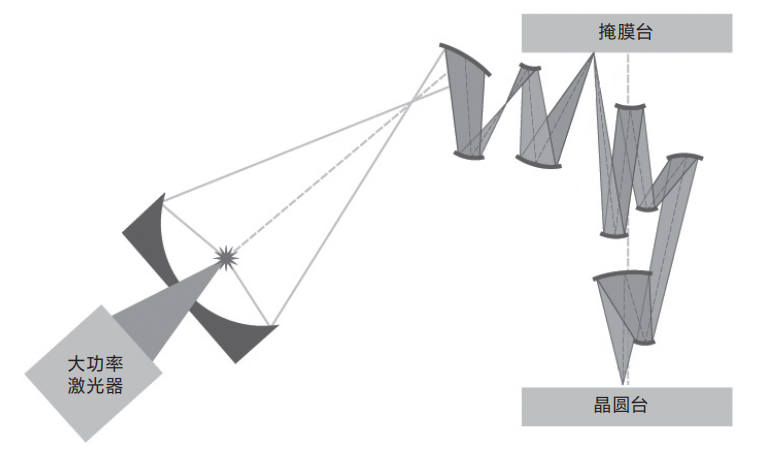

EUV***(見圖14-4)的光源波長是13.5納米,僅為浸沒式***的1/10,是解決這一問題的希望。然而,EUV***的問世時間卻一次次地推遲。早在1994年,半導體業界的幾家公司就聯合起來啟動了EUV***的工業化進程。阿斯麥爾公司于2006年交付了一臺光刻膠的掃描樣機,但之后卻卡在了激光光源這一障礙上,波長13.5納米的EUV光太難產生了。

直到2011年,美國加州的西盟半導體設備公司(Cymer)提出了一種產生極紫外激光的方法。阿斯麥爾公司的一位光刻專家阿爾貝托·皮拉提(Alberto Pirati)評論說:“我第一次聽到這個主意的時候,覺得它很瘋狂。”這個主意是將金屬錫高溫熔化,把極其細微的液滴均勻地噴灑在一個空腔里,然后用大功率二氧化碳激光器發出一束強光,以每秒5萬次的頻閃照射這些液滴,并將其轉變為類似太陽中的等離子體,從而激發出13.5納米的EUV。

圖14-4 EUV***原理示意圖

然而,這種方法的效率卻異常低下,激光器需要20千瓦功率的輸入(可為100臺冰箱供電),卻只能得到11瓦(相當于一盞LED臺燈的功率)輸出,遠小于光刻所需的250瓦,其余99.945%的能量都變成熱量耗散掉了。

不得已,西盟半導體設備公司找到了一個變通方法:用一束低功率的先導激光照射滴液顆粒,將其“壓扁”成薄餅形狀,增大受光面積,接著再用高功率激光照射,以激發出更多的EUV光。2013年,輸出的光源功率提高到了55瓦,2016年達到了200瓦。

2018年終于達到了實際工作所需的250瓦。盡管EUV光源有了,但新的問題又冒了出來。EUV光無法在空氣中傳播,因為這么短波長的光會被空氣吸收掉。為此,機器內部的光傳播路徑和晶圓加工臺所在區域要抽真空。

更麻煩的是,玻璃透鏡也會吸收EUV光,人們不得不放棄使用了幾十年的透鏡,改用反射鏡。然而,普通的反射鏡也會吸收EUV光。為此,阿斯麥爾公司發明了一種特殊的鏡子,表面交替涂有硅和鉬的薄層,每層只有幾納米厚。利用兩種材料不同折射系數的布拉格效應,每個交界面處都可以反射一部分EUV光。

EUV光在到達晶圓臺前要經過12個反射鏡,每次反射損失30%,最后只有約1%的光線能照射到晶圓片上。本來250瓦的光源,照到晶圓上只剩下2瓦。

如此微弱的光線需要光刻膠極其敏感,但高靈敏度的光刻膠又會引起加工精度的波動……技術難題層出不窮,解決完一個,又冒出一個。

經過多次延遲,阿斯麥爾公司最終克服了難以想象的困難,制造出了人類歷史上最精密的***,每臺成本高達2億美元。

2018年,阿斯麥爾公司開始向客戶交付EUV***。每臺機器的部件需要4架波音747飛機運送。運抵晶圓廠后,那里會有準備就緒的上百名工程師,他們負責安裝和調試。***占地約80平方米,其中激光部分占了20平方米。整個機器像一座冰山,因為大量管道和線纜埋在地下10米深處,然后才是露出地面的部分。

2020年,經過17年的研發,EUV***終于開始用于5納米節點的工藝制造。它在未來面臨著新的挑戰。1納米及以下的技術節點需要更高的分辨率。這時,就需要高“數值孔徑”的EUV***,而后者所需的光源功率還要再翻一倍,達到500瓦才行。

然而,EUV***很快也將達到極限。IRDS預計,2028年半節距將達到極限的8納米(此外,盡管X光和電子束的波長比EUV更短,但是由于X光需要占地面積很大且昂貴的同步輻射源,而電子束的串行寫入會導致效率低下,被認為不適合大規模芯片制造)。那將會是“懸崖邊緣”,再往前就是量子力學的不確定性統治的世界了。當光刻精度達到極限后,晶體管尺寸將無法繼續縮減。

唯一有可能繼續增加晶體管密度的方法,就是將多層芯片在垂直方向上堆疊,這就像是將一層平房變成高層樓房,以提高晶體管密度。實際上,在EUV***之前的工藝上,人們制造成本敏感的存儲器時就已經開始使用3D堆疊技術,這樣就無須采用最先進的***,也能很好地控制成本。目前,存儲器已經實現了數百層的堆疊。

除了以上困難,CPU性能提升也變得越來越緩慢。20世紀90年代,CPU性能每年可以提升52%,到了21世紀前十年每年只能提升23%,從2011到2015年,這個數值又下降了近一半,只有12.5%,而在2015年到2018年幾乎停滯,只有3.5%。

而且,CPU和存儲器之間的“內存墻”也越來越難以逾越。馮·諾伊曼計算機要先從內存中調取數據,再送入CPU中計算。但是,CPU處理能力顯著提高后,計算機從內存調取數據的速度并沒有等比例提高,于是CPU和內存之間就形成了通道瓶頸。

CPU很快將“腹”中的數據“消化完畢”,而新的數據卻遲遲不能從內存“喂”過來,CPU不得不處于“饑餓”狀態。據估計,計算機從內存將數據搬運過來的時間比CPU處理時間至少長10倍,CPU只能將寶貴的時間和資源浪費在等待上。

造成CPU和內存之間存在“高墻”的原因有多方面,其中之一是CPU和內存的距離,它們位于不同的芯片,容易造成信號延遲。為了縮短這段距離,人們提出將CPU與內存封裝在同一顆芯片內,分別放置在不同層,然后堆疊成一顆三維芯片,層與層之間通過硅通孔相連,以縮短信號傳輸距離。然而,即使CPU和內存在同一顆芯片內的不同部分,互連線上的時延也越來越嚴重。

徹底解決“內存墻”問題的方法是改變CPU從內存中調取數據的方式,不再以計算單元為中心,而改為以存儲為中心,發展計算、存儲一體的“存內計算”。這種全新的計算機架構有可能改變“80歲高齡”的馮·諾伊曼計算機架構的統治地位。

02. “擴展摩爾”

隨著“延續摩爾”遇到的障礙越來越大,人們開始尋找其他解決路徑。2005年,ITRS提出了“擴展摩爾”的概念。這條路徑追求的不是縮小單個晶體管的尺寸,而是增加系統功能的多樣性,在一個芯片上集成和實現豐富的功能。

這條路徑關注的不是CPU和存儲器這些需要最先進工藝的數字芯片,而是模擬、功率、傳感以及數模混合芯片,它們不需要最小的晶體管,但能實現豐富的應用場景。

“擴展摩爾”根據頂層的應用與需求來拉動技術的發展,其中一個最大的需求就是物聯網。過去幾十年中,個人電腦和手機先后普及,但數量已經趨近飽和,將來的數量至多再提高3倍。而未來的物聯網設備,包括智能家居、健康監測、自動駕駛汽車、環境監測等,還會增加3個數量級,構成一個無處不在的物聯網世界。

例如,自動駕駛汽車里需要激光測距雷達、超聲波傳感器、加速度計等多種傳感器;醫療領域需要可穿戴式的生理信號監測設備,以及為了抑制癲癇發作的植入式傳感器和電流刺激芯片等;環境監測領域需要能探測各種二氧化碳、硫化物等污染物的傳感器芯片。這些傳感器需要跟CPU、存儲器等集成在一起,從而實現豐富的功能。

此外,我們也需要高效的電源,想要實現極低的功耗,滿足便攜或移動設備的要求。我們同樣需要用高信噪比的傳感器和模擬電路來感知或采集微弱的生理信號、危險氣體的濃度等。我們也需要滿足各種頻段的無線射頻電路,實現更多樣的無線連接。

另外一個有“擴展摩爾”需求的是能源領域。與硅相比,氮化鎵和碳化硅等半導體材料的性能更優異,用它們制成的功率器件可以在相同的耐受電壓下提供更高的開關頻率,或者在相同的耐受電壓和開關頻率下有更低的導通和開關損耗。

此外,人們也將對能量收集技術產生極大的需求,因為許多傳感器安置在露天環境中,沒有市電供電,也不方便更換電池。而能量收集的途徑可以是機械振動、冷熱溫差或者無線電波、光線等,這將大大地延長芯片的工作時長。

最后,柔性電子將在基于織物的可穿戴設備、折疊屏幕、薄膜太陽能電池等方面發揮作用。未來相當一部分柔性電子設備將通過打印在柔性基材上的方式制造出來,但這需要業界在有機材料和碳基材料上取得進一步突破。

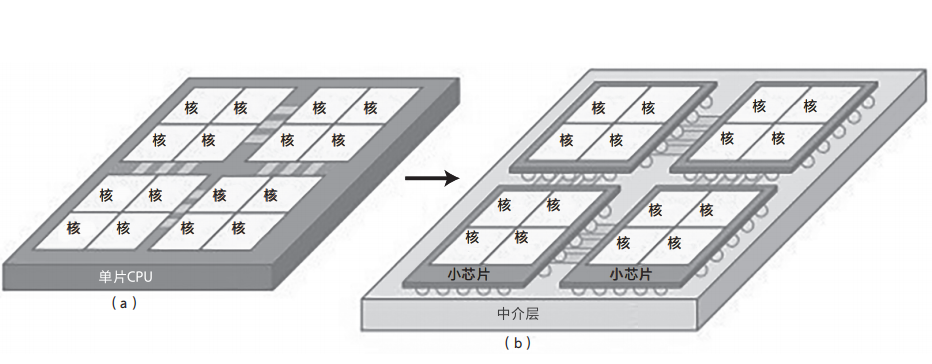

從2017年開始,一種叫作小芯片(Chiplet)的技術引起了業界,尤其是超威半導體公司的興趣。以往,人們盡量將不同的電路模塊集成到一顆芯片上,以降低成本。但是人們發現,加工的芯片面積越大,芯片良率(晶圓片上性能良好的裸芯片的比率)越低,進而推高了成本。反之,將大芯片拆成小芯片則能提高良率,降低成本。

于是,一種相反的趨勢出現了:將大芯片拆解成尺寸較小的單個芯片,分別制造,然后再通過封裝技術合成在一起(見圖14-5)。這有點像先制造小塊的樂高積木,然后將其拼成一個更大的整體。例如,將一顆面積為360平方毫米的芯片拆成4顆小芯片分別制成,它的良率將提高兩倍多。在這一趨勢下,未來CPU中的內核會越來越多。超威半導體公司的一款“霄龍”處理器(簡稱EPYC)中有8個小芯片,每個小芯片中又有8個內核,總共有多達64個內核。

小芯片技術為芯片系統增加了一個自由度,即每個小芯片的制造都可以自由地采用最佳性價比的工藝,CPU和內存采用先進工藝以提高算力,而模擬和射頻等則采用較為低價的成熟工藝,以降低整體成本。

圖14-5 將單一芯片(a)拆分為小芯片(b)分別制成,并通過下方基板互連起來

1958年到1959年基爾比和諾伊斯發明集成電路時,他們分別解決了集成和互連的問題。現在60多年過去了,我們仍然走在追求如何更好地集成和互連的路上。集成的方式從平面走向了三維,從單芯片走向了多芯片,從單一電路互連走向了數字、模擬、射頻、傳感器等多種電路的集成,從硅集成走向了硅、碳、鍺等元素的共同集成,從平面互連走向了立體互連。

03. “超越摩爾”

大數據、物聯網、人工智能和超級計算等新技術的計算需求對芯片性能和能效提出了更高的要求,于是就有了第三條路:“超越摩爾”,又叫“超越CMOS”,即在主流的CMOS技術之外尋找更好的可能。

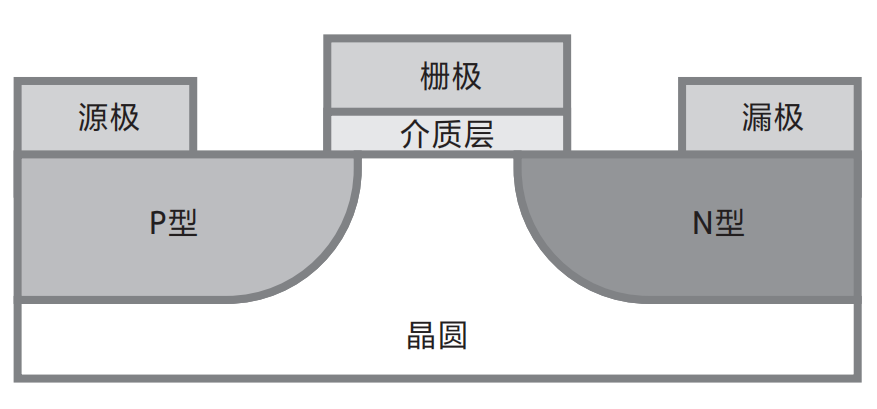

硅晶體管中的漏電流一直是科學家的心頭大患。為此,人們發明了TFET(其結構見圖14-6)。它利用導帶與價帶之間的量子隧穿效應,控制晶體管的開與關,使漏電流更小、導通電流更大,突破了傳統晶體管中的麥克斯韋-玻爾茲曼統計限制,使得亞閾值擺幅低于60 mV/dec的下限。不過,TFET的源極與漏極不再像MOS場效晶體管那樣同為P型半導體或同為N型半導體,而是一邊為P型半導體,另一邊為N型半導體,這對器件制造和應用提出了新的挑戰。

圖14-6 TFET的結構

硅材料雖然適合大規模生產,儲藏豐富,還有一個天然穩定的絕緣氧化層,但它也有難以克服的缺點:電子遷移率低,導致開關速度不高;散熱特性一般,限制了芯片的工作頻率。這些問題都讓“延續摩爾”之路變得困難重重。

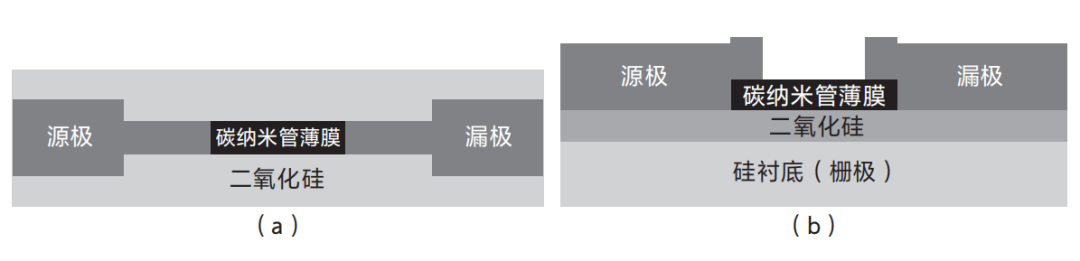

而碳材料則在遷移率、小尺寸和散熱特性方面具有優勢。在實驗室中,研究者已經用碳納米管制成了CNTFET(見圖14-7),結構類似于硅MOS場效晶體管,只是將中間的導電溝道換成遷移率更好、散熱性更好、尺寸更小的碳納米管。目前,人們仍在解決大規模制備方面的挑戰。

圖14-7 CNTFET注:俯視圖(a)和側視圖(b)

無論是BJT,還是MOS場效晶體管等器件,都是用電子作為信息處理的媒介,創新的思路則是采用速度更快的光子。光子沒有散熱問題,不受電子噪聲影響,而且光信號延遲小、通信帶寬遠高于電信號。

此外,用硅材料就能做出各種光處理器件(光波導、光濾波器和光連接器等),它們很容易就能集成到CMOS芯片中,從而大大地降低成本。制造光互連處理器已經開始變得可能。不過,硅光電子仍需要突破一些技術瓶頸才能進入實際應用。

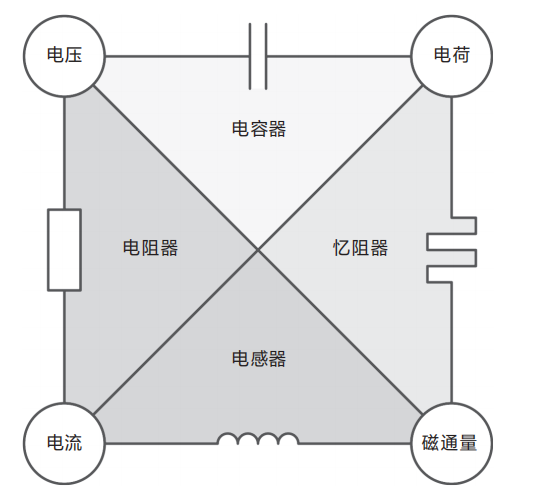

1970年,加州大學伯克利分校的蔡少棠(Leon Chua)教授發現,當時已有三種基本元件:電阻器,負責關聯電壓和電流;電容器,負責關聯電壓和電荷;電感器,負責關聯電流和磁通量。但電荷與磁通量是否可以有直接關聯呢?蔡少棠提出,或許存在第四種基本元件能將電荷和磁通量直接關聯,他將其命名為憶阻器(memristor)(見圖14-8)。2008年,惠普實驗室威廉姆斯領導的團隊做出了單器件結構的憶阻器,僅僅由兩端的金屬和中間的氧化物構成。

憶阻器具有電阻記憶效應,掉電后能維持電阻數值,在脈沖信號的激勵下能改變電阻值,就像大腦的突觸在神經元脈沖的刺激下改變連接強度,能作為人工電子突觸模擬大腦中的化學突觸,實現學習記憶功能。憶阻器的尺寸可以做到納米級,但是在制備良率以及器件一致性方面仍有較大的改進空間。

除此之外,人們在自旋場效晶體管(簡稱Spin-FET)、PCRAM、RRAM、磁阻式隨機存取存儲器(簡稱MRAM)、柔性薄膜晶體管(簡稱FTFT)等方面也展開了研究,但由于傳統器件成本低、產量大,這些新型器件的優勢還無法體現出來,不能在短期內替代現有器件。

圖14-8 四種基本元件之間的關系

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論