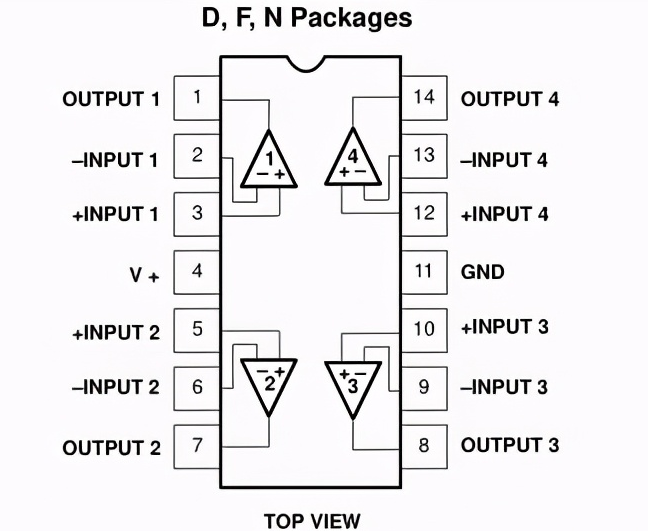

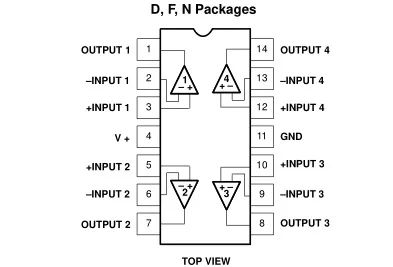

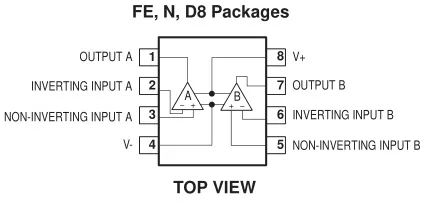

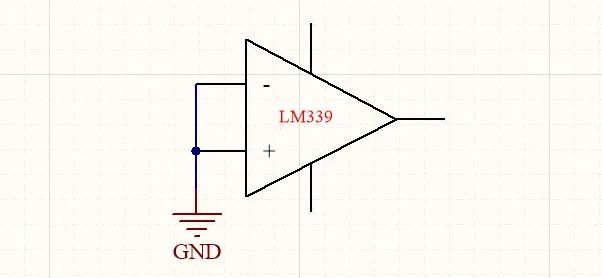

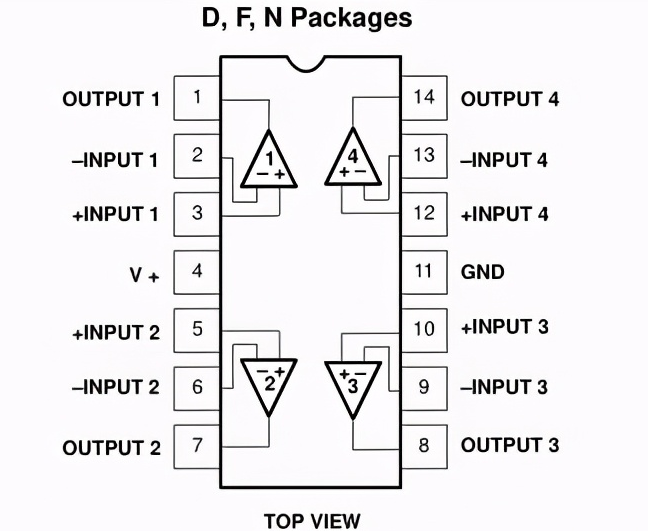

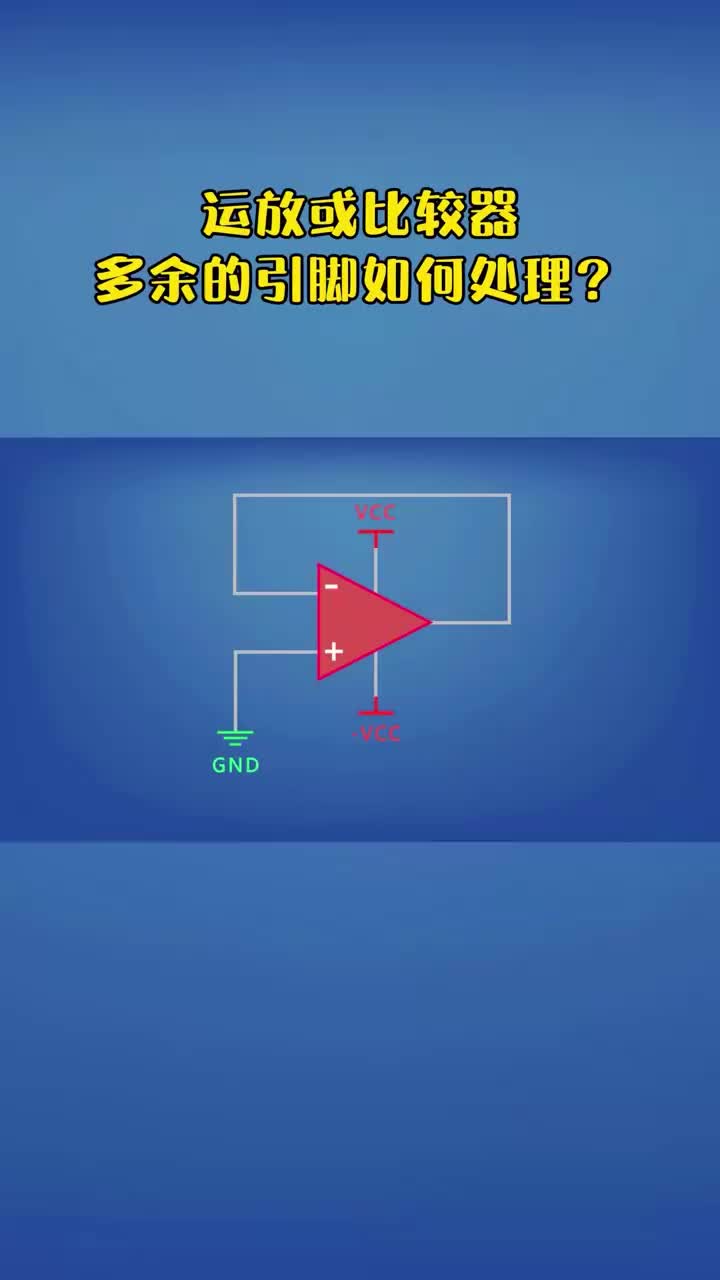

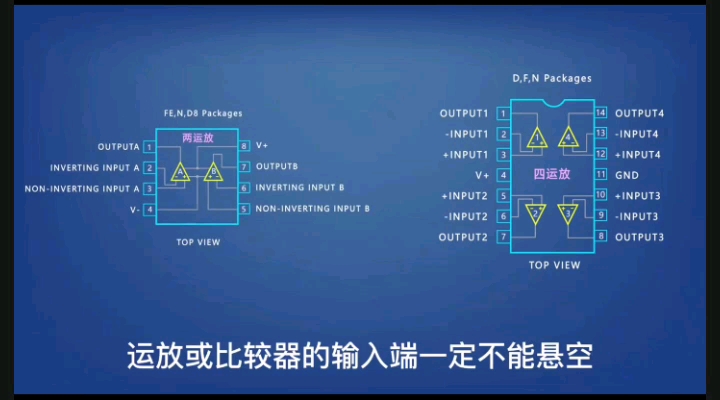

在實際應用中,運放的同一個封裝里面有雙運放或四運放(如下圖),但有時候我們只需使用其中的一部分,多余的引腳怎么處理呢?

2021-03-14 11:30:13 24014

24014

用OPA847做一個簡單的運放,它不但沒有放大,反而還將輸入正弦波衰減了一半,847后面接了一個tl3016比較器,他們之間用一個50歐電阻串聯

2015-08-07 11:21:39

中的,并一直貫穿到課后的課程內容。同時為了更好的記憶和理解電路,還會做一些適當的延伸,雖然課程講運放,但是課程從比較器開始,講濾波器電路,從最簡單的LC開始到RLC,再到以運放實現的濾波電路。講信號

2019-06-29 19:00:37

是一方面,另外運放當比較器時輸出不穩定,不一定能滿足后級邏輯電路的要求。 4、比較器為集電極開路輸出,容易輸出TTL電平,而運放有飽和壓降,使用不便

2021-05-14 06:57:05

如下圖一,運放加MOS管組成的恒流源,調節電阻器R4的阻值,改變運放U1A的3腳的電壓值(不大于2V),運放2腳的電壓值隨之變動,運放的輸出也在變化。問題:運放的正向反向端的電壓相同,這運放的輸出是哪里來的?(當運放U1A的3腳的電壓值大于2V。運放就成了比較器)

2021-06-28 21:41:50

AD825 是一款比較經典的高速運算放大器, 其頻率特性優異, 失調和增益誤差極小, 溫漂極小, 負載適應性強, 具有高輸出驅動能力且價格低廉, 廣泛應用于低失真濾波器、 音頻放大器、 ADC 輸入

2022-09-09 19:20:46

是比較大的,進行電路設計時,不得不考慮的。而對于FET輸入的運放,由于其是電壓控制電流器件,可以說它的柵極電流是很小很小的,一般會在fA級,但不幸的是,它的每個輸入引腳都有一對ESD保護二極管。這兩個

2013-08-11 22:05:01

`請問比較器和運放的區別是不是在于運放是閉環的而比較器是開環的?`

2012-08-23 16:55:34

,對研發也是有幫助的。課程的提到的名詞其實經常都在耳邊掛著,但總是不能深入的了解,但愿這次的學習能有所收獲。在一節課程里既提到了運放,有提到了比較器,顯然兩者有某種關系。通過對這兩種元器件的比較想必會更

2019-06-26 21:55:55

本帖最后由 gk320830 于 2015-3-5 23:27 編輯

運放和比較器的根本區別

2012-08-08 14:37:15

穩定!這時候你就要成本/風險仔細核算一下了.⑵:運算放大器和比較器如出一轍,簡單的講,比較器就是運放的開環應用,但比較器的設計是針對壓門限比較而用的,要求的比較門限精確,比較后的輸出邊沿上升或下降時間要

2015-04-05 12:16:03

!這時候你就要成本/風險仔細核算一下了

二、升或下降時間要短,輸出符合TTL/CMOS 電平/或OC 等,不要求中間環節的準確度,同時驅動能力也不一樣。

一般情況:用運放做比較器,多數達不到滿幅

2023-11-21 07:24:06

對于模擬電路設計來說器件的選型很關鍵,但對于經驗不豐富的工程師來說也是一個很大的難點,我這里有一份運放和比較器的型號對照表,器件的參數也很清楚,知道為什么要選這個器件的理由!

2012-08-31 23:06:18

運放和電壓比較器的本質區別

2021-03-02 07:06:17

1、運放可以當比較器用,比較器不可當運放用

2、運放為推挽輸出,比較器為開集輸出,需接上來電阻

3、運放的電平翻轉速度比比較器要慢

2023-05-23 23:12:42

萬倍或更多,用數值直接表示不方便比較,所以一般采用分貝方式記錄和比較。一般運放的共模抑制比在80~120dB之間。 10、電源電壓抑制比(Supply Voltage Rejection Ratio

2018-09-29 15:26:19

現在有一個運放,在高頻段輸出相對于輸入假設有60度的延遲,這個延遲怎么由反饋網絡做出補償?我想到幾個辦法如下?

1、在反饋網絡作出處理,讓高頻段從反饋網絡輸入到輸出,這樣就避免了在運放內部的容性

2024-01-29 15:57:06

將運放結構改為比較器結構,運放的開環增益和比較器的增益大小是否是一致的。

2021-06-24 06:49:28

電壓的關系根本不是線性倍數關系。求教。另外,一個正常的運放輸出阻抗應該是很小的,但是五管單元輸出阻抗很大。很好奇商用運放輸出阻抗是怎么處理的。

2017-04-23 20:55:05

誰有運放類比較全的資料沒?聯系郵箱***@163.com

2014-07-09 20:11:31

TSH94 ST 高速低耗四運放TSH95 ST 高速低功耗四運放TSM102ST 雙運放-雙比較器和可調電壓基準TSM221ST 滿幅度雙運放和雙比較器UA748 ST 精密單運放UA776 ST 可編程低功耗單運放X9430 Xicor 可編程雙運放`

2012-05-16 13:55:57

請求高手幫忙分析:當單片機GPO輸出的PWM占空比較高的時候,此時LED的電流應該增大,通過運放來做恒流。但是現在就是當占空比高的時候運放不恒流了。而且輸入電流不斷的變大,我懷疑是運放已經自激,影響了整個環路的穩定性。請大伙幫忙分析。。。。謝謝!

2017-06-28 09:38:14

有使用過這顆運放的大神嗎?求助,輸入電壓范圍0-75mV,加120%輸入經運放放大后會超出采樣芯片的峰值電壓(0.6V左右),該如何處理輸出電壓使其滿足范圍

2016-11-30 15:32:03

、USB PD及Type-C快充功能,內置可編程協議I/O控制器,提供了OPA運放、CMP電壓比較器、USART串口、I2C、SPI、定時器、12位ADC、Touchkey等豐富外設資源

2023-09-02 14:45:14

功能,內置可編程協議I/O控制器,提供了OPA運放、CMP電壓比較器、USART串口、I2C、SPI、定時器、12位ADC、Touchkey等豐富外設資源。 CH32X035系列提供最多2個可獨立配置

2023-09-11 16:20:44

。一般實際運用時,引腳不建議懸空,易受干擾。對于TTL或非門接地處理,對于TTL與非門可以懸空或接高電平。至于COMS不能懸空,那是因為COMS的柵極和襯底是被二氧化硅隔開,它比較脆弱,只能承受幾百伏

2018-12-03 10:49:35

實際運用時,引腳不建議懸空,易受干擾。對于TTL或非門接地處理,對于TTL與非門可以懸空或接高電平。至于COMS不能懸空,那是因為COMS的柵極和襯底是被二氧化硅隔開,它比較脆弱,只能承受幾百伏的電壓

2018-08-30 11:18:22

上圖中,是358雙運放的應用電路,想請教一下,1.在進行PCB繪圖過程中,假如輸入端IN離運放較遠,那么圖中左邊方框里的C1、R1是選擇靠近輸入端IN,還是靠近運放級358_1比較好??2.進行

2019-03-20 06:35:57

源電壓;V+ < V- 時 輸出Vout偏向于Vs-負電源電壓。輸出與輸入之間沒有負反饋或使用正反饋時,運放可認為是比較器。接下來學習了經典的窗口比較器功能,三分之二VCC連接到比較器A1同相

2019-06-25 13:56:03

與差模電壓輸入電壓的比值。由于差模開環直流電壓增益很大,大多數運放的差模開環直流電壓增益一般在數萬倍或更多,用數值直接表示不方便比較,所以一般采用分貝方式記錄和比較。一般運放的差模開環直流電壓增益在80

2014-05-26 13:30:40

由于運算放大器(運放)規格不同,工程師們經常需要選擇多個運放以滿足其電路板上每個子系統的需求。這會使從采購到生產的工作更加復雜。但是,可以選擇一個運放來滿足您的系統需求,這將有助于優化定價和降低設計總成本。讓我們來看一看一個單運放如何處理三個常見的功能:電流感測、溫度感測和比較器操作。

2021-01-14 07:26:24

什么叫做“未使用的運放”?是指在芯片儲藏箱或防靜電袋中的運放?

2021-04-06 07:08:28

項目要把一個Vpp為20mV的小信號(頻率2Hz,帶1V的直流偏置)放大到0~4V。 信號比較弱,還要直流成分,請問怎么處理才好? 我準備用一個帶通濾波器濾掉高頻噪聲和直流成分后再放大到0~4V。 請問用RC濾波合適還是用運放搭個有源濾波電路好?

2019-04-03 09:51:59

請教,有時候在一個集成運放芯片里面,存在雙運放,我們在使用一個運放放大之后,還剩下一個沒有用,是否能夠用剩下的來做跟隨器?有效果嗎?如下圖所示

2021-09-02 11:18:48

`如圖所示,誤差放大用的是運放比較器,這個能實現穩壓嗎?這個運放穩壓ic用的是輸入電壓的話,那么運放輸出不就是跳變電壓,要么是0,要么就是12v,不是嗎?而不是根據穩壓輸出的取樣變化,使運放輸出從0到12v之間變化了?這樣就不能隨著輸出變化而實現實時穩壓了。還請各位多多指點`

2018-05-31 01:38:51

抄的別的電路。比較器LM2901。PC13、PC14、PC15、PB9是stm32的管腳。V_TC1、V_TC2、V_TC3、V_TC4是運放的輸出。比較器LM2901的作用的是什么?

2017-08-08 18:14:27

第一講:運放用作比較器的注意事項作用:窗口比較器用作保護電路,如電壓電路溫度等等。太大了不好太小了也不行,必須在合理的范圍之內。1、比較器相與,兩個同時輸入為高電平時,輸出才為高,只要其中一個輸出為

2019-07-03 12:06:51

``華強芯城引進聚洵高性能模擬及混合信號芯片——運放、比較器,自營現貨,下單秒發,歡迎咨詢下單!》》》點擊查看聚洵運放和比較器活動詳情``

2018-09-26 16:14:24

大家好!我有個項目中設計二階巴特沃斯低通濾波器,截止頻率160KHz,需要的增益是0.62,我選了一個增益帶寬積28MHz的運放,運放手冊里寫是一個“單位增益穩定”的運放,我看一些資料中寫濾波器增益

2023-11-23 06:08:34

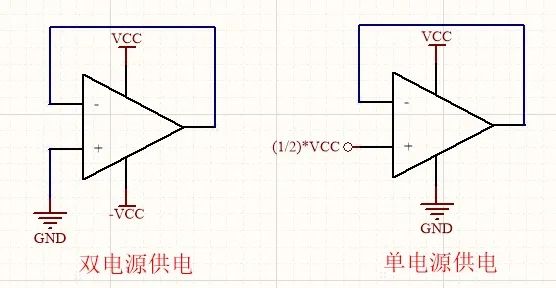

(1)分析分析:單電源運放和單電源運放1.1 電源供電和單電源供電所有的運算放大器都有兩個電源引腳,一般在資料中,它們的標識是VCC+和VCC-,但是有些時候它們的標識是VCC+和GND。這是因為有些數據手冊的作者企圖將這種標識的差異作為單電源運放和雙電源運放的區別。但...

2021-11-11 06:07:27

最近在幫朋友做一個DAC在1794的IV和LPF部分不知道用哪款運放比較好,因為布局的緣故,最好就是雙運放,官方文檔上推薦的5534配合LT1028感覺出來的參數一般般而且還是單運放,不知道有沒有一款可以比它好更多的運放呢,LME4920能作為IV和LPF上的運放不

2019-08-05 10:33:10

在protel 99se里沒有找到比較器,可以用運放代替嗎?請問比較器怎么找

2018-05-02 17:43:21

在數字電路中TTL與非門的多余的輸入端應如何處理?有幾種方法?

2023-04-28 10:49:44

在Virtex-5 FPGA RocketIO GTP收發器用戶指南,UG196 2.1版,第230至236頁中,有關于如何處理未使用或部分使用的磁貼的電源和其他引腳的信息。第231頁的表10-7中

2020-06-04 16:51:11

看到一篇專家文章,拷貝過來分享下,平常在用ADI的運放中也會遇到這些困惑。這里所談論的 “未使用的運放” 不是指在芯片儲藏箱或防靜電袋中的運放;而是指在同一個封裝里面的多個運放中未被使用的部分

2018-09-20 14:59:14

這里所談論的 “未使用的運放” 不是指在芯片儲藏箱或防靜電袋中的運放;而是指在同一個封裝里面的多個運放中未被使用的部分。

最好將未使用的運放連接為一個帶反饋回路的放大電路。顯而易見,單位增益緩沖

2023-11-22 07:45:48

你好,我有兩個關于FX3 GPIOS的問題。在我的設計中,我應該如何處理未使用的GPIO引腳?我應該讓它漂浮嗎?我的第二個問題是關于22OHMS電阻。在數據表中,據說22OHM應該連接到由

2019-10-23 10:45:50

我現在處理一個傳感器,傳感器內部是一個熱電阻,工作溫度80-150°C,阻值240歐。運放需要對傳感器輸出電壓進行放大。

目前我遇到一個很難處理的問題。由于電阻溫度高,具有很大的熱噪聲。而我的采樣

2023-11-24 07:50:05

模電 利用單運放或雙運放設計加減電路 U0=10U1+20U2+15U3-4U4-5U5

2023-03-17 10:05:12

本帖最后由 gk320830 于 2015-3-5 17:19 編輯

如何只顯示運放的引腳序號,不顯示運放引腳的名稱,我是新手,如何分析那運放,見圖片

2014-04-17 21:47:25

運放的基本分析方法:虛斷,虛短。對于不熟悉的運放應用電路,就使用該基本分析方法。運放是用途廣泛的器件,接入適當的反饋網絡,可用作精密的交流和直流放大器、有源濾波器、振蕩器及電壓比較器。 1、運放在

2019-01-07 14:47:46

采集信號放大用的 幾mv 單通道5引腳 高輸入阻抗,CMRR比較大,低噪聲,雙電源運放

2019-05-16 07:55:55

運放虛短有差距,大家怎么處理的?就是在V-=0.167V時,V+在0.172,運放是RAIL TO RAIL的懊惱啊

2019-08-23 04:36:00

/風險仔細核算一下了 二、升或下降時間要短,輸出符合TTL/CMOS 電平/或OC 等,不要求中間環節的準確度,同時驅動能力也不一樣。一般情況:用運放做比較器,多數達不到滿幅輸出,或比較后的邊沿

2018-09-05 11:45:32

在運放的使用過程中,會遇到這樣的情況:例如一個運放芯片集成了兩個獨立的運算放大器,在用作電壓跟隨器的時候,我們只用到了一個運放,另外一個運放可能就不管了。針對未使用的運放,我們應該如何處理才更合適呢

2022-01-25 06:30:00

作者: TI 專家 Bruce Trump翻譯: TI信號鏈工程師 Tom Wang (王中南) 我們在這里所談論的 “未使用的運放” 不是指在芯片儲藏箱或防靜電袋中的運放;而是指在同一個封裝里面

2018-09-21 15:35:31

`* 購買須知:本課程為虛擬內容服務,訂閱后不支持退訂、轉讓,請大家諒解主要包括以下內容:第1部分:初識運放--開環1、同相端、反相端、輸入輸出阻抗、增益2、兩端電壓穩定,輸出即穩定,用作比較器3

2019-07-10 12:24:14

求一適合的電壓比較器或運放,當作品傳統電壓比較器用,LM339試驗過效果不太佳,求高速器件型號。需求如下: 當輸入信號峰值超過3.1V標準電壓后,電壓比較器輸出跳變(低電平到高電平,或高電平到低電平

2019-03-06 00:41:20

。 +輸入引腳的電位 》 -輸入引腳的電位時,輸出高電平; -輸入引腳的電位 》 +輸入引腳的電位時,輸出低電平; 比較器符號 比較器輸入輸出關系圖 2.電壓比較器與運放的差異 電壓比較器

2021-01-20 16:12:37

傳統運放一般都是電壓型運放,但是還有一類運放是電流型運放,電流型輸入運放的輸入側和輸出側均采用了單位增益緩沖器。

1、對于單位增益緩沖器而言,其輸入電阻無窮大輸出電阻比較小,請問單位增益緩沖器

2024-01-18 21:42:34

不止一款芯片出現過該情況,比如8腳的AD8028是雙運放,用其中一個做個簡單的跟隨器,沒有信號給入同向輸入端時,竟也能在同向輸入端檢測到有直流電平近2V存在。后來,嘗試僅給芯片供電,其他引腳不做任何處理和連接,仍有直流電平存在,求解釋!!!

我嘗試其他常用精密運放,比如opa228,也有該情況出現

2023-11-20 08:10:09

需要使用RF開關芯片HMC252A的RF1、RF2、RF3通道。RF4、RF5、RF6通道該如何處理?直接懸空還是接地?

2019-01-21 11:14:15

哪位大俠用過這樣的比較器或者運放的,請告訴小弟型號,感激。Vout是MCU輸出提供的,Out_wave是MCU檢測的

2019-06-26 03:58:17

我現在處理一個傳感器,傳感器內部是一個熱電阻,工作溫度80-150°C,阻值240歐。運放需要對傳感器輸出電壓進行放大。目前我遇到一個很難處理的問題。由于電阻溫度高,具有很大的熱噪聲。而我的采樣需要

2019-03-07 13:13:56

來論壇也有一段時間了,請允許我問一個比較籠統的問題,因為這個問題一直困擾我很久了,請各位見諒 1.如何判斷電流型運放和電壓型運放?它們各有什么特點? 2.在芯片選型的時候,我如何知道我應該去選擇電流型運放比較好還是電壓型運放比較好呢? 3.除了電流型運放和電壓型運放,還有什么其他運放嗎?

2019-09-16 01:38:19

不止一款芯片出現過該情況,比如8腳的AD8028是雙運放,用其中一個做個簡單的跟隨器,沒有信號給入同向輸入端時,竟也能在同向輸入端檢測到有直流電***2V存在。后來,嘗試僅給芯片供電,其他引腳不做

2018-08-20 06:49:00

這個運放是比較器還是放大

2017-11-17 08:59:10

TTL邏輯電路多余的輸入端該如何處理?能否懸空? TTL邏輯電路是一種常用的數字邏輯家族,用于實現各種邏輯功能。在設計TTL邏輯電路時,經常會遇到要處理的多余輸入端的情況。這些多余的輸入

2024-01-16 11:39:35 383

383 ttl門多余的輸入端如何處理 ttl多余的輸入端可以懸空嗎? TTL門是一種常見的數字邏輯門。TTL門通常具有多個輸入端,其中有些輸入端在特定的使用情況下可能是多余的。這些多余的輸入端可以通過

2024-02-18 16:26:24 288

288

電子發燒友App

電子發燒友App

評論