下一代5G網絡的愿景是相比現有的4G網絡,在容量、覆蓋范圍和連接性方面實現數量級提升,同時大大降低運營商和用戶的每bit數據成本。

5G新無線電(NR)標準化第一階段的重點是定義一種無線電接入技術(RAT),利用新的寬帶頻率分配(包括6GHz以下和24GHz以上的頻段),以實現國際移動通信2020年及之后的愿景展望中提出的大峰值吞吐量和低延時。

圖1:5G使用案例

FWA部署

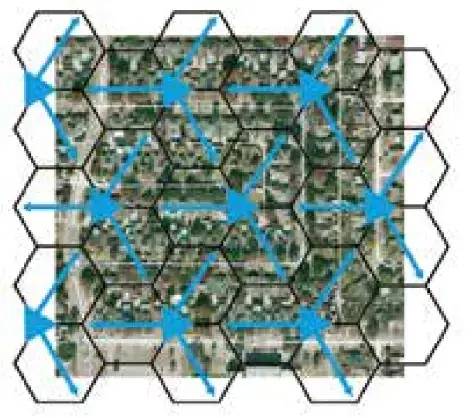

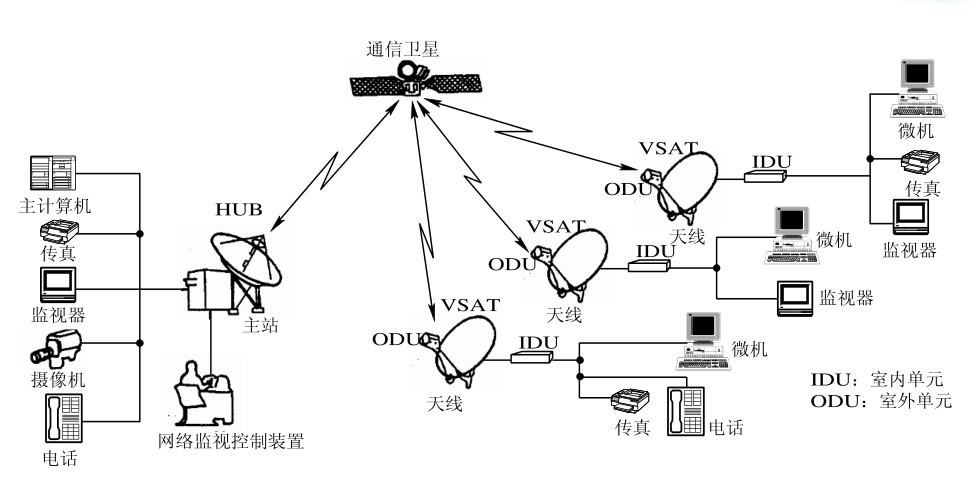

通過利用NR RAT,尤其是在毫米波頻段方面實現的改進,移動網絡運營商只需花費傳統電纜和光纖到戶設施的一小部分時間和成本即可向家庭、公寓和企業提供千兆固定無線接入(FWA)服務。FWA描述了一個集中的分扇區的BTS與多個固定或移動用戶之間的無線連接,如圖2所示。

圖2:城市郊區環境中的FWA

以任意城市郊區為例,假設每平方公里有800個家庭,BTS站點間距離(ISD)為500m,運營商需要設置至少9個蜂窩站點,形成23個扇區。此時,每個扇區覆蓋約35個家庭。如果提供1Gbps服務且網絡超額利用率為目前的5倍,那么每個BTS的容量約為5Gbps,對應每個扇區平均BTS總容量為3Gbps,可以提供400MHz的帶寬。再假設該郊區有35%的用戶簽約使用1Gbps服務,費用為100美元/月,則收入為14000美元/扇區/年,177000美元/平方公里/年。

由此可見,較大的覆蓋范圍對于成功實現FWA商業化至關重要,運營商也會要求設備供應商構建能夠再最高規定限值下運行的BTS和CPE設備,以最大限度地提高覆蓋率和盈利能力。這樣一來,在運營商預期的成本、尺寸、重量和功率預算范圍內構建符合這些目標要求的系統成為一大挑戰。選擇適當的前端架構和RF半導體技術是應對這一挑戰的關鍵。

按列饋電陣列

新興的毫米波有源天線均采用了兩種主要平面架構,即「按列饋電陣列」和「全硅陣列」。

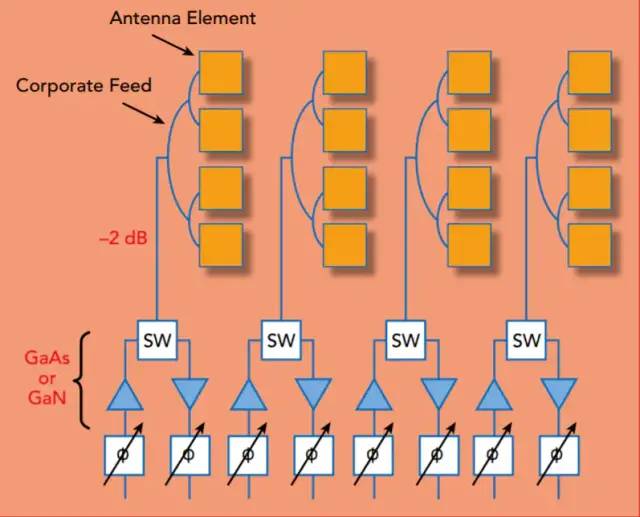

圖3:射頻前端位于陣外的按列饋電陣列

圖3是按列饋電陣列的典型架構,在這種結構中,控制IC位于陣列外部、進行一對一驅動;列中所有單元增益/相位設置統一。控制IC與發射單元之間一般采取并聯饋電結構。為簡單起見,圖3只展示了4*4的情況;實際生產中,行列可選取任意數字。

由于控制IC位于陣列外,因而可以采用高射頻功率的GaAs或GaN來驅動陣列,使得每個單元都具備極高的射頻功率,從而實現小陣列高發射EIRP。還可通過同時驅動天線柱的頂端和底端得到雙極化陣列。

該架構的主要優點有:

每個單元都具備高射頻功率;

每N列只需要N條控制IC射頻電路;

由于IC位于陣列區域之外,不需要受到其尺寸限制。

最后一點對GaAs或GaN工藝來說非常重要,因為這兩種半導體工藝的集成度有限,無法將控制元件整合到毫米波陣列的λ/2范圍中。當然,這一點也隨之為射頻前端組件帶來了插入損耗,因為控制IC需要通過饋線來傳輸發射單元的射頻能量。

雖然發射端的插入損耗可以通過增加少量的有源單元即可彌補,但是接收端卻要增加一倍的數量。造成這種情況的原因有兩點:

接收端G/T值滿足10log(N),其中N為陣列中單元個數,因此前端的損耗需要更多單元才能補償。

根據饋電損耗和接收機噪聲系數值的不同,饋電損耗對G/T的影響可能會超過1dB/dB。這意味著饋電損耗每產生1dB的變化,G/T便會降低1.5到2dB。縱然基于GaAs或GaN的按列饋電平面陣列具有較高的EIRP,但其接收性能很成問題。

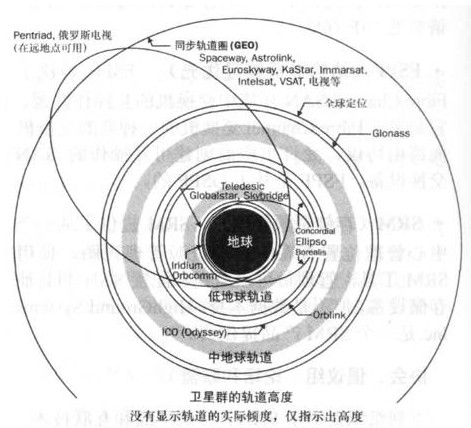

按列饋電架構的另一個缺陷在于它只能支持一維波束導向缺少二維波束導向對于前期的5G固定無線接入應用來說還不算大事;但對中低軌衛星通信系統(LEO/MEO SATCOM)、移動衛星通信系統及城區密集的5G小基站而言,二維掃描能力是必需的,按列饋電架構便不合適了。

采用GaAs和GaN工藝實現控制IC還有一大問題便是無法對電路的振幅和相位變化進行自補償。組件間|S21|和∠S21的變化分別可高達±2dB及±100°,不能自調便意味著要對陣列進行校準,對天線系統而言又是一筆巨大的成本開支。

此外值得注意的一點是,僅有少數全球性供應商能實現6寸GaAs和GaN工藝,在同樣規模的生產力條件下,12寸的Si工藝顯然成本要低很多,更何況6寸GaAs和GaN工藝還不夠成熟。

陣列前端密度

早期的毫米波FWA BTS設計采用單獨的單極化發射和接收天線陣列,隨著相控陣單元之間的格柵間距越來越小,比如39GHz時已縮小到3.75mm。為了最大限度地減少饋電地插入損耗,需要將射頻前端組件置于靠近輻射單元的位置,以便將多種功能整體集成在裸片上或多芯片模塊封裝內。為了實現所有功能的部署,我們要么成倍的提高陣列大小,以容納更多的RFFE組件,要么使用GaN等具有高功率的半導體材料。

此外,在半導體材料的選擇上,還要考慮耐溫性。由于SiGe的可靠性在溫度高于150°C時就會急劇下降,因此我們會選擇額定溫度為225°C的GaN-on-SiC,尤其是針對室外被動冷卻式相控陣。

全硅陣列

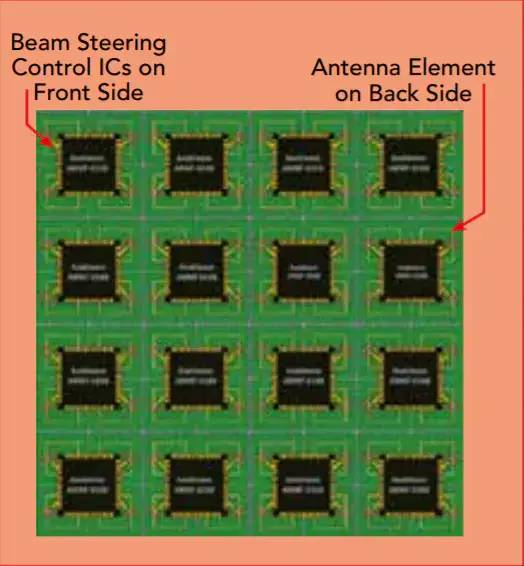

另一種有源天線架構是全硅陣列,其波束控制IC位于內部,如圖4所示。

圖4:全硅架構使得射頻前端能夠嵌入陣列內

波束導向控制IC包含了發射輸出、接收輸入、增益控制以及相位控制器件,全部集成在一塊硅片上。芯片可以是單一發射器、單一接收器或是半雙工發射/接收器。

該架構的優點在于可以將饋電損耗盡可能地降低,從而使發射EIRP和接收G/T的效率達到最大。同時,由于各個發射單元振幅和相位設置均不同,便可以實現LEO/MEO衛星通信、移動衛星通信和高密度城區所需的全幅二維掃描。同時,該架構只采用了硅工藝,產能高、成本最低、供應商充沛,無疑是另一大優勢,而且硅材料集成度高,能夠實現片上系統,因此可以植入一些功能來免去陣列校準的必要。這些對毫米波衛星通信和5G 有源天線等大規模市場而言非常重要,因為它們極需要壓低成本。

波束成型技術

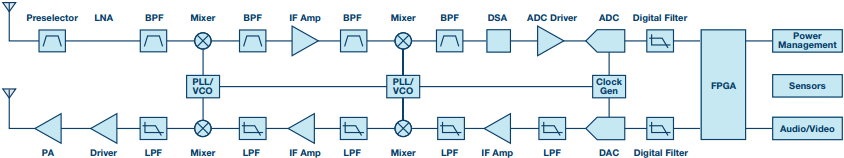

有源天線主要應用了三種通用的波束成型架構:模擬、數字及混合成型。

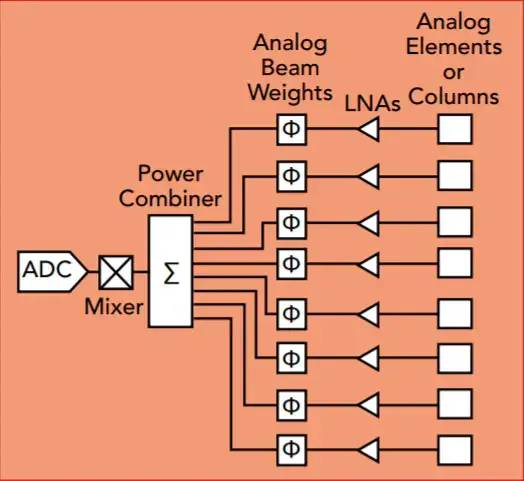

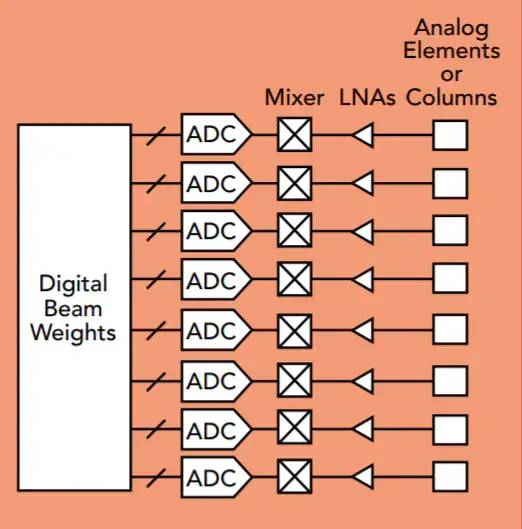

全硅架構下的模擬波束賦形通過對陣列中的每個單元加上模擬波束權重來實現(圖5);按列饋電架構下則對每列加權。進行了模擬波束加權后,相干功率合成波束,后接一個頻率合適的下變頻器及ADC構成接收天線系統。

圖5:模擬波束成型

數字波束成型(圖6)使用復雜的數字權重而非模擬權重,使用該技術在毫米波頻率下的陣列過于密集,二維掃描就不適用了。因為按列饋電架構只能進行一維掃描,電子器件都位于陣列外部,所以可以應用數字波束賦形。同時,因為每個完整的接收器對應一列而非一個單元,所消耗的直流功率顯著降低。

圖6:數字波束成型

數字波束賦形還有幾大難點,包括直流功耗高(尤其是在將大帶寬數字化的情況下);信號通路復雜,其中大量I、Q數據點必須繞過陣列與數字處理器相連;本機振蕩器(LO)信號通道需要控制在陣列內。不過,令人欣慰的是,如果這些困難都能迎刃而解,那這個架構便具有極大的發揮空間,因為無需更改硬件就可以形成多個波束及零點,同時全陣列的增益能影響到每個波束。

數字波束成型的熱管理技術也頗具挑戰,但是即將問世的新型GaN FEM(有限元建模)可幫助解決這個問題,再加上新一代RF采樣DA/AD轉換器實現的功耗節省、毫米波CMOS收發器的改進以及小信號集成度的提高,要不了多久,我們就能目睹更多全數字波束成型解決方案的部署。

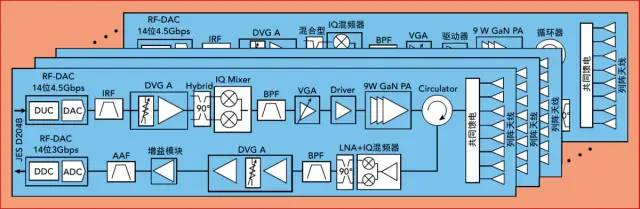

圖7:采用數字波束成型和現成商用組件的陣列設計

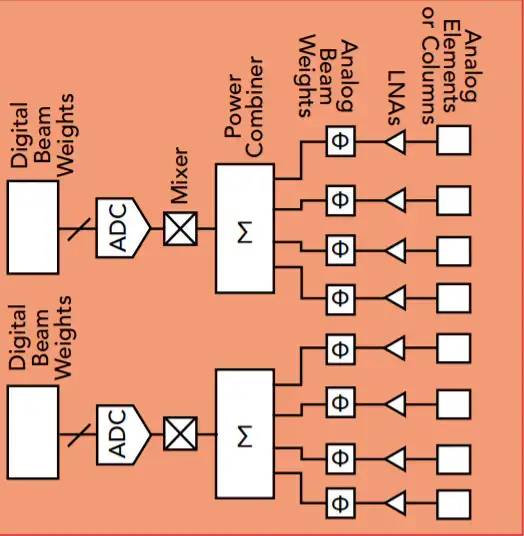

混合波束成型是模擬與數字波束賦形的結合(圖8),其優勢包括:

可以在毫米波頻率下使用;

靈活度高,無需更改硬件即可動態形成許多波束和零點;

單個單元不需要完整的射頻通路,每個子陣僅需一條。

圖8:接收通路的混合波束成型

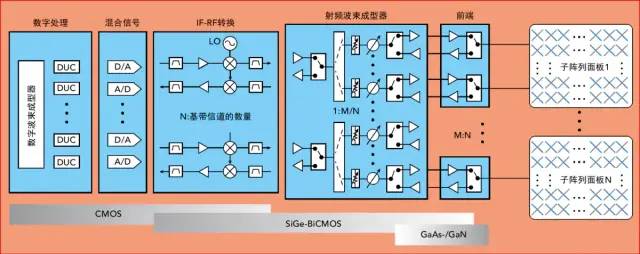

混合波束成型有源陣列的基本框圖如圖9所示。此處,N個基帶信道用于驅動RF模擬波束成型器,進而將信號分為M條路徑,并提供單獨的相位和振幅。流行的設計比率是16或64個有源單元對應一個基帶信道,不過也要視實際部署而定。

圖9:采用混合波束成型的有源陣列

例如,如果采用熱點小基站(或在CPE終端側),那么一個1:16單面板就可以了;而一個宏BTS就需要1:64的面板,如果有24個子陣列,則對應256512個有源單元和4~8個基帶信道。

RFFE半導體的選擇

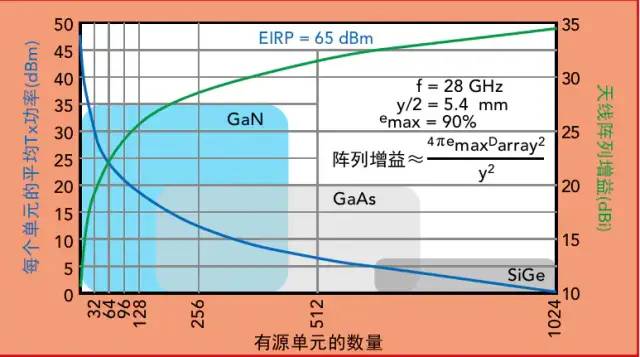

RFFE技術選項取決于系統的全向輻射功率(EIRP)和G/NF要求。這兩者都由波束成型增益決定,而波束成型增益則由陣列大小確定,如圖10所示。

圖10:優化RFFE技術與陣列大小的關系

上圖添加了最適合每種半導體技術的功率范圍指示,功率限值根據每項技術的基準進行設置,從而避免采用會降低組件可靠性或效率的外來功率合成或方法。隨著陣列大小越來越大(超過512個有源單元),每個單元的功率變得足夠小,以便使用SiGe;相反,如果采用GaN技術,則實現相同的EIRP所需的信道數減少為1/8或1/16。

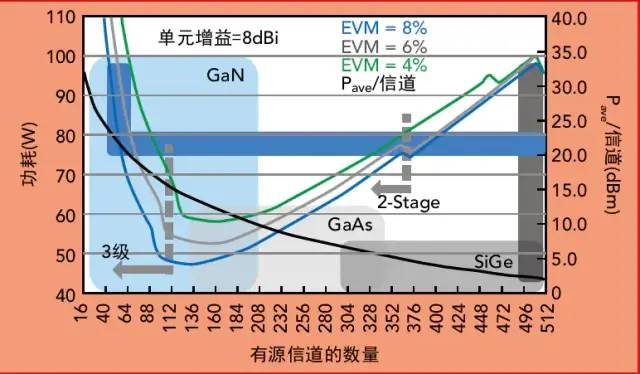

對于可實現64dBm EIRP的陣列,圖11分析了波束成型器加前端的總PDISS與每個子陣列有源單元數量之間的關系。

圖11:64dBm EIRP的系統功耗與陣列大小以及EVM的關系

從圖中,我們可以看出,PA效率越低,隨之波束成型器的效率則也越低。換句話說,選擇將陣列大小增加8倍以實現完全采用SiGe的解決方案要付出一定的代價,因為輸入信號被分為更多條路徑,且需要使用線性偏置型耗電器件將信號放大。

相控陣的成本包括RF組件、印刷電路板材料和天線成本。采用化合物半導體前端可將陣列大小立即減少到1/8,同時PDISS不會增加。即使采用較低成本的印刷天線技術,也可以大大節省昂貴的天線基板材料成本。考慮到組件成本,目前采用4英寸晶圓制成的150nm GaN-on-SiC,每平方毫米成本僅為8英寸130nm SiGe的4.5倍。隨著6英寸GaN生產線開始實現大批量生產,GaN的成本會降至SiGe的3倍。采用高功率密度型化合物半導體(如采用6英寸晶圓制成的GaN)時,可將完全采用SiGe的架構原始裸片成本降低35%。雖然每個組件的硅技術成本較低,但整個系統的成本明顯更高。

基于Qorvo自行研發的FEM工具,在輸出功率相當的情況下,GaN PA的裸片尺寸只有GaAs PA的1/4,同時不會降低增益,且效率稍有提高。考慮到采用LNA ,我們選擇了90nm GaAsPHEMT工藝,因為它的NF略占優勢。然而,在考慮使用額外的焊線和50Ω匹配網絡后,其凈改進只是幾個十分之一dB。經過權衡分析我們得出,最好繼續采用允許PA、LNA和T/R開關進行相互匹配的單片GaN設計。這樣的設計風險更低,更易于裝配和測試,且可采用盡可能緊湊的MMIC。系統熱分析表明,GaN-on-SiC提供的更高結溫對于被動冷卻式陣列至關重要。

總結

FWA商業化很快就會實現,原因在于低成本頻譜資源豐富、早期監管和標準制定工作得當,并且運營商有機會快速開拓一個新市場。剩下的挑戰是要有可用的設備能夠以合理成本閉合鏈路。

用于5G和衛星通信的有源毫米波天線在未來幾年將實現空前的量產,兩種主要的平面結構已經問世。一種基于GaAs或GaN工藝,IC位于陣列外;另一種基于硅工藝,IC位于陣內。

作者:Hubery_Lee

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論