FPGA 原型設計人員艱苦努力所得的明顯回報就是 ASIC 設計可以及時而毫無問題地完成產品定案(tape-out)。不過,原型設計還有一點日益重要的優勢,即 ASIC 或 SoC 中嵌入的軟件在項目開發的早期階段便可與實際速度硬件進行完美集成。

為什么軟件團隊要關注 FPGA 原型設計問題

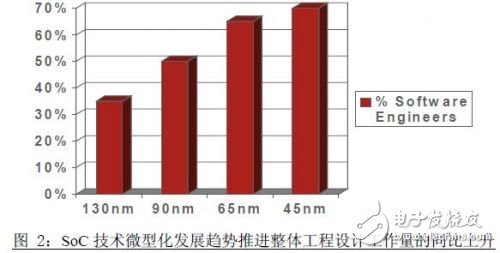

獨立的 EDA 分析師 Gary Smith 指出(見圖 1),SoC 采用的CMOS工藝節點日益小型化,而且技術越來越復雜,因此軟件組成部分已成為產品特色和開發焦點所在。進入市場的最新消費類器件多采用復雜的 SoC,其中包括眾多嵌入式處理器和幾十萬甚至數百萬行代碼。Apple iPhone 就是一個很好的例子,它至少包含 3 個 ARM 處理器。加速產品上市進程對產品推出至關重要,在此情況下,怎么才能在 SoC 環境中進行軟件驗證呢?

SoC 開發團隊越來越多地開始采用 FPGA 原型設計作為解決方案來進行驗證并及時推出各種類型的產品。

為什么選擇原型設計技術?

集成操作系統、應用和硬件非常復雜,會出現許多不可預見的軟件問題。實際速度運行的 FPGA 原型設計能提供一個獨特的環境,在關鍵的集成階段節約數月之久的高強度軟件測試工作。如果這款原型設計還要采用其它軟件,要進行其它實驗室測試,那么原型設計的優勢會進一步體現出來,即便對客戶接受度測試來說都是有益的。Synplicity 推出的 HAPS (高速 ASIC 原型設計系統)等現成的高質量 FPGA原型驗證板基本解決了投放產品的時間問題,剩下的就是要考慮成本問題:

增加板的用量將找出更多錯誤

軟件的潛在用戶數量巨大,他們會隨心所欲使用軟件,難免不造成操作系統鎖死,應用崩潰,或者做些軟件工程師根本想象不到的事情。

何時進行原型設計

在 SoC 設計完成之前就進行調試顯然是非常有利的。圖 1 顯示了大型 ASIC 項目各階段中通常要特別注意的模擬、仿真和原型設計問題。我們可以看到,FPGA 原型設計最常用,因為項目在集成階段需要確保高速和高容量。

我們不妨設想這樣一種情況,軟件集成問題的最佳解決方案需要修改硬件。舉例來說,需要將占用大量周期的DSP算法提取出來,并用協處理器或定制的器件邏輯來代替。如果 SoC 已基本完成了產品定案,甚至已完成設計推出了樣片才發現這一問題,那么不管修改錯誤對最終產品有什么好處,我們也不太可能考慮對器件進行必要的調整了。事實上,早期進行 FPGA 原型設計有助于及時進行設計調整。FPGA 原型設計技術使用越來越多,其原因之一就是在項目早期階段可判斷軟/硬件的問題并權衡利弊(也請參見圖 1)。

原型設計面臨的挑戰

實施 ASIC 的 FPGA 原型需要解決多種開發難題。令人驚訝的是,設計硬件本身并不是最具挑戰性的問題。事實上,許多廠商都提供為滿足特定目的而設計的 ASIC 原型板(如HAPS)。真正的挑戰則在于如何實施 FPGA 設計方案。

分區和 I/O 處理

盡管目前最大的 FPGA 每個都能處理 200 多萬個 ASIC 門,但眾多 ASIC 設計的要求要大得多。這就要求對 SoC 的關鍵部分進行原型設計,或者設計方案必須在多個 FPGA上進行分區。但這會造成一些有趣的障礙,因為我們的整體目標是進行驗證,因此分區時必須盡可能減少對 ASIC RTL 的變動。設計方案分區會造成人為的分界線,如果設計方案的內部總線或數據路徑較寬,則會造成所需 I/O 引腳的數量爆炸性增長,進而引起 FPGA 引腳不足。即便采用最新型的 FPGA,每個 FPGA支持 1000個以上的I/O 引腳,也有不夠用的時候。

我們可在同一 FPGA 引腳上先對多個信號進行多路復用,然后再在目標 FPGA 上進行多路分解工作,從而生成更多 I/O 資源。即便如此,我們還是不希望變動 ASIC RTL,因此要進行自動引腳多路復用。這肯定會產品性能造成一定的影響;但 FPGA 的I/O足夠快,即便采用多路復用技術,仍能提供足夠高的性能,確保復雜的嵌入式軟件驗證工作能夠以實際速度進行。

不改變 RTL 就修改拓撲結構

憑借設計人員的智慧,通過一定的手動干預,我們可在一個以上的 FPGA 中復制子模塊,從而減少 I/O 限制,降低互連需求。通過對 RTL 做進一步的專門化操作,如對低級門進行位切片(bit-slicing)或壓縮(zipper)更多復雜模塊(這些都不需要變動 RTL),可進一步降低 FPGA I/O 需求。

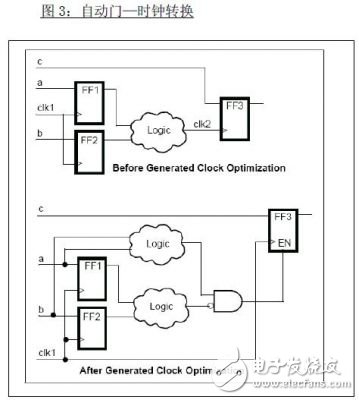

ASIC 時鐘和 FPGA 時鐘不一樣將 SoC 設計移植到 FPGA 上時,設計團隊還會面臨更多問題,因為原始 RTL 的作者根本不可能考慮到 FPGA 問題。RTL 中不利于 FPGA 的因素包括 ASIC 元件例化和 RAM BIST 等,不過最重要的問題在于 IP 和時鐘復雜性。為降低功耗,FPGA 會盡量支持ASIC 常用的門控時鐘(gated-clock)設計風格。時鐘門信號必須轉化為 FPGA 硬件中的時鐘啟用(clock enables)信號。手動進行這種轉換工作量太大并帶來新的問題。一些合成工具可以自動進行門—時鐘轉換,甚至能支持復雜的時鐘生成電路。圖 3 顯示了 Synplicity 的 Synplify Premier 中自動化時鐘轉化的實例。

處理IP

ARM 處理器等大型 IP 塊可作為完整的芯片購買,直接接口于其它原型設計硬件。唯一要求就是硬件必須足夠靈活,以滿足ARM Coretile 等多種支持 IP 功能的子卡需要。但是,存儲器、FIFO、乘法器和加法器等小型常見功能太多了,難以通過這種方式一一滿足。適當的 EDA 軟件能自動將這些功能轉化為 FPGA 內部兼容型實施方案,或者通過簡單的方式將其隔離到FPGA外部實現。

采用FPGA板后的工作

設計移植到 FPGA上并以實際速度運行后,又會出現另一個問題,即如何高效完成調試工作。嵌入式或外置的邏輯分析器可解決此問題,但這些工具通常工作于門級層面。因此,跟蹤返回至 RTL級(即最初進行設計的層面)的信號會花費大量時間,畢竟這需要在合成步驟中逆向工作。最好用能無縫保持門級和 RTL 級層面之間軟鏈接(symbolic link)的工具進行調試。

Synplicity 開發了稱作 TotalRecall Full Visibility Technology 的新技術,能自動從原型設計中提取完整的測試實例,其中包括導致故障或斷言失敗的所有情況,可以了解軟件調試觸發器的外部輸入問題等。捕獲到的測試實例可隨時在正常 RTL 模擬器中重放并分析。該功能使 FPGA 原型設計能擴展到更廣泛的驗證環境中,現在已經在Synplicity 的 Identify Pro 產品中實現。

FPGA 原型設計技術的發展趨勢

以實際速度運行的 FPGA 原型為復雜的嵌入式系統和 SoC 的驗證工作提供了強有效的解決方案。如前所述,目前,我們可以獲得解決本領域中一直面臨的各種挑戰的 EDA 工具和現成的原型板。即便如此,還有待全面集成原型設計硬件和工具組件。這樣我們就能縮短原型設計和重復修改的時間。隨著功能的不斷發展,Synplicity 的 Confirma平臺等以實際速度運行的驗證系統將取代其它傳統驗證方法,成為所有 SoC 開發工作中不可或缺的一部分。

電子發燒友App

電子發燒友App

評論