如今,涉及模擬和數模混合電路的SoC設計日益增多。由于電路規模增大和復雜度提高,傳統的SPICE仿真器已不能滿足設計需求。而采用電路分割、多速率仿真、改進的器件模型等技術的Fast SPICE仿真器突破了傳統SPICE工具的容量和速度限制。此文主要討論目前復雜模擬和數模混合電路仿真面臨的主要挑戰,以及如何用新一代Fast SPICE仿真器加以解決。

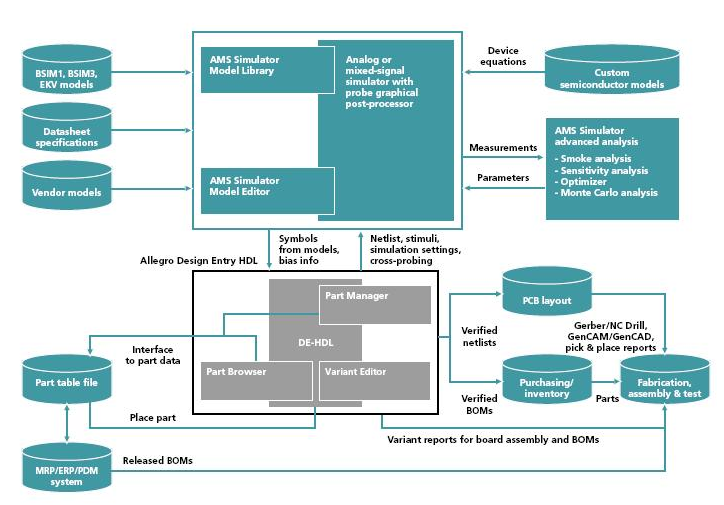

對今天的混合信號SoC設計,往往包括模擬、射頻、數字、定制數字和來自不同IP提供商的IP。為實現完整意義上的芯片級驗證,需要采用SPICE、射頻仿真器、混合信號仿真器和Fast SPICE等多重仿真器的組合。設計者在不同設計階段往往需要采用來自不同公司的仿真器,而這些仿真器由于不同的環境支持和不同的語法格式存在兼容性問題,往往導致誤差和不穩定性,并增加額外工作量和設計風險。

圖1:Multi-Mode仿真(MMSIM)解決方案。

為降低用戶在設計工具方面的使用難度和工具轉換風險,Cadence推出Multi-Mode仿真(MMSIM)解決方案,通過使用統一的用戶接口、器件模型、語法格式、內部方程式,極大地提高了數據兼容性和仿真結果可信度。Multi-Mode技術使設計者可在統一的設計環境中,在模擬、射頻、混合信號、芯片級電路驗證的不同設計階段,自由切換Spectre、SpectreRF、AMS Designer和Ultrasim等仿真器,如圖1所示。

本文將著重討論如何應用分層的全芯片晶體管級驗證工具—UltraSim,解決目前模擬/混合信號電路設計中面臨的挑戰。

模擬/混合信號電路仿真面臨的挑戰

隨著工藝技術的發展和競爭的壓力,主流芯片已經從10年前的0.5微米發展到今天的0.13微米乃至90納米。先進的工藝可以讓設計者把更多、更復雜的電路模塊集成在同一硅片上,但同時也對電路仿真提出了新的挑戰。目前模擬/混合信號電路仿真面臨的挑戰主要有以下幾個方面。

1. 急劇增長的設計復雜度,對仿真器的容量和速度提出更高的要求;

2. 激烈的市場競爭和不斷爬升的流片費用,使如何縮短設計周期、提高流片成功率成為芯片設計中的主要問題之一;

3. 深亞微米小尺寸效應的影響變得更為顯著,如短/窄溝效應對閾值電壓影響、亞閾值電流、體效應導致的襯底電流等;

4. 低信號擺幅設計中電路噪聲和交叉耦合效應、低電源電壓下信號線和電源網格的電壓降和電遷移問題等;

5.

圖2:MMSIM中的共享組件。

SoC芯片中電源調節器導致電路各模塊間電源耦合增強。混合信號仿真由于數字模塊和模擬模塊分開仿真,不能反映此類問題;

6. 對互連線延遲、信號串擾、襯底效應、接地噪音(Ground bounce)等物理效應的考慮,依賴于精確的后仿真結果。

上述問題的解決越來越依賴于全芯片晶體管級電路仿真及后仿真,而傳統晶體管級SPICE仿真器由于容量和速度的限制,通常只適用于模塊級電路設計,因此Fast SPICE技術的引入不可避免。

Fast SPICE技術介紹

為了克服第一代SPICE仿真工具(如Spectre、PSPICE)在仿真容量(約50K)和速度上的缺陷,第二代SPICE技術即Fast SPICE仿真器采用電路分塊、多速率、簡化模型等加速仿真技術。

傳統SPICE仿真器將電路作為一個矩陣,隨著電路規模的增加,矩陣的求解速度顯著下降。Fast SPICE把相關的電路模塊放在一起,將大矩陣分成許多小矩陣,減小計算量。此外,事件驅動技術可忽略不活動的電路,進一步降低運算量。

電路分塊的另一個優點是可采用多速率仿真。各個電路模塊往往存在不同的工作頻率,因此仿真中不同的電路塊可以采用不同的仿真步長。這樣,既可以保證高頻率的電路得到精確結果,又讓低頻率的模塊避免重復計算,降低CPU負荷。

簡化模型技術是Fast SPICE加速的另一項重要技術。在傳統電路仿真中,MOSFET或BJT需要一組復雜的公式進行計算,常常耗費大量的CPU時間。而Fast SPICE在仿真開始時先產生模型表格,然后進行查表,從而節省大量的時間。Fast SPICE通過多層次簡化的模型,可以滿足不同的精度和速度要求。

使用UltraSim進行模擬/數模混合電路仿真

圖3:布局后仿真流程和RC縫合技術。

Virtuoso UltraSim Simulator作為新一代Fast SPICE仿真器,引入了分層化同型仿真、動態電路分割等技術,對電路中的相同子模塊只需計算其中一個,避免重復計算,從而進一步提升仿真容量和速度;提供與傳統SPICE的完全兼容以及和SPICE類似的仿真精度;簡潔的選項使設計者可以方便地定制電路仿真;改進的RC減小技術使之可以進行精確、快速的后仿真。此外,UltraSim已完全集成于Cadence標準模擬設計流程之中。這些優點使UltraSim成為目前業內應用最廣泛的Fast SPICE工具之一。

1. 精確模型支持

硅精確的器件模型從來都是得到準確的電路仿真和物理效應分析的關鍵。通過與業內公認的先進器件模型提取工具BSIMPro+共享所有的模型和公式,UltraSim不僅擁有強大的器件模型支持能力,而且還可確保獲得硅精確的仿真結果。

2. 本征兼容性

Cadence MMSIM中的各種仿真器(包含Spectre、SpectreRF、AMS Designer和UltraSim)都通過CMI讀入器件模型,并使用相同的VerilogA引擎,消除了因為仿真器不兼容帶來的不準確性和不穩定性(如圖2所示)。此外,作為混合信號仿真器,UltraSim支持Spectre、結構化Verilog和多種SPICE網表;支持所有標準模型和描述特定電路的模型單元(如閃存宏模型)、行為描述語言VerilogA和SpectreHDL;支持VCD/EVCD/VEC;支持傳統SPICE的后處理方式(如.measure,多種波形文件格式等)。

3. 強大的后仿真能力

因為引入大量寄生電阻電容(RC),后仿真更富有挑戰性。UltraSim采用專用的RC減小技術可有效減小RC數目(可達90%),且將精度損失控制在1%~3%以內。與傳統的RC減少技術相比,UltraSim專利算法在保證精度的同時能更顯著地減小仿真時間和內存消耗。UltraSim采用的RC減小技術并不是簡單過濾小電容或小電阻,而是用簡化的等效RC網絡代替原來復雜的RC網絡,并可根據信號頻率自動調整RC的簡化程度。

表1:Spectre和UltraSim的∑-Δ ADC仿真結果對比。

UltraSim支持所有標準的后版圖網表格式,如SPICE網表、Extracted View、扁平或分層化的DSPF或SPEF網表、DPF以及節點電容網表等;并支持目前業內多種后仿真流程。此外,UltraSim的RC縫合技術可以選擇性地把寄生RC加到指定的電路模塊上(如圖3),使設計者可以靈活地定制其電路仿真流程,例如對某些數字模塊采用行為級模型,某些重要的模擬模塊采用帶寄生參數的網表。UltraSim提供postl選項設置RC減小的簡化程度,它可以自動調整所有相關RC壓縮參數。有經驗的設計者也可以根據需要自由調整各個參數。

4. 仿真易用性

模擬/數模混合電路的仿真精度取決于模型精度和仿真器容差。設計者在使用UltraSim時,一般只需設置仿真模式和速度來優化仿真,到達良好的精度和速度匹配。當然,有經驗的設計者可以依據對其設計本身和Fast SPICE技術的了解來調整各個選項,進一步提高仿真性能。

UltraSim已完全集成于Cadence標準的全定制設計流程中。用戶可以在ADE中方便地切換Spectre、UltraSim和AMS Designer等不同的仿真器,完成從模塊級電路到全芯片的仿真與調試。在ADE界面下,設計者可以根據需要產生Spectre或標準SPICE網表,并以圖形化方式快速設置仿真模式和速度等選項,獲得良好的精度和速度匹配。此外,ADE也為UltraSim的時序、功耗、可靠性分析提供友好界面。

5. 電源網絡分析、設計檢查及其它

對于包含電源網絡的電路,電阻網絡的存在會降低仿真速度。為此,UltraSim推出了UPS方案,通過把電源電阻網絡和其它電路分離,由UPS和UltraSim協同仿真。因此,在得到3-5倍加速仿真的同時,仍能得到精確的IR壓降分析報告。

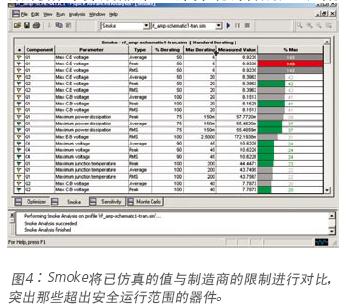

為了發現和修改設計中的錯誤,UltraSim提供多種設計檢查功能,包括過載電流檢查、電壓越界檢查、高阻結點檢查、DC漏電流路徑檢查等。Ultrasim的時序分析工具可以幫助設計者來檢測轉換時間、建立時間、保持時間或者脈沖寬度上的錯誤,而功耗分析工具可以報告指定時間、指定子電路端口上的電流和功耗。

對于高頻電路,Ultrasim提供了Fast Envelope仿真等。

仿真實例

下面部分通過兩個典型實例說明如何用UltraSim仿真模擬/數模混合電路。

1. ∑-Δ ADC

相對于Nyquist采樣ADC,過采樣ADC包含的模擬器件數目較少,但由于過采樣率很高,往往需要較長的瞬態仿真時間。本實例為某∑-ΔADC的后仿真。該電路內部最高時鐘頻率為450MHz,包含1個VerilogA模塊、瞬態分析時間為20us,FFT分析采樣點4,751。表1為Spectre和UltraSim的仿真結果對比。

表2 :RC減小前后器件統計。

這里仿真選項設為sim_mode=MS(模擬/數模混合電路的全局模式一般采用默認的MS模式)、speed=1(定義仿真器的容差,相當于Spectre的Moderate模式)。

為保證仿真精度,后仿真使用了默認值(postl=1),即較保守的RC減小技術。從表2中可以看到,RC減小后,電容的數量從60.7K減小到1.3K,其中耦合電容數僅為529。由于采用層次化和同構技術,juncap的數量從27K減小到2.11K。最終,UltraSim獲得11倍的速度提高。

2. RF PLL

本實例為一用于無線通訊的PLL,其前仿真網表包含31K MOSFET、600BJT、75K二極管和大約1.5K R/C。參考時鐘頻率為33MHz,LC型VCO頻率為3.9GHz。UltraSim參考設置為:

.usim_opt sim_mode=ms speed=5 analog=3

.usim_opt speed=4 method=gear2 IPLL.VCO

.usim_opt sim_mode=df IPLL.LOGIC

這里,我們采用了MS仿真模式,其中analog=3使UltraSim在電路劃分時考慮更大的反饋回路以保證精度;speed=4, method=gear2局部地加于VCO模塊(通常RF VCO需要使用gear或trap收斂算法以及更小的容差)。數字模塊采用了df模式,即用簡化的數字表格模型來進一步提高速度。UltraSim僅用了19小時就完成25us瞬態仿真,甚至超過設計者的期望值。

- 仿真技術(25215)

- 組圖模擬(6582)

相關推薦

如何通過仿真有效提高數模混合設計性

1359

1359

0RCAD電路混合電路仿真教程

48V數模混合類主板PCB設計

數模混合電路中,數字地和模擬地怎樣能比較有效地隔離?

數模混合電路的PCB設計

數模混合電路設計的難點

數模混合PCB設計的基本概念和電路種類區分

數模混合PCB設計詳解

Altium Designer的混合電路信號仿真工具介紹

CAE有限元仿真技術面臨的挑戰有哪些

Cadence PSpice仿真技術的優勢有哪些

Protel 99 SE電路設計與仿真技術 (電子書)

cadence pcb仿真使用說明

《模擬集成電路設計與仿真》何樂年pdf

【資料分享】硬件工程師必讀攻略:如何通過仿真有效提高數模混合設計性

【轉】數模混合PCB布局規則

以DAC為例,介紹AMS-Design數模混合電路仿真的方法是什么?

做數模混合設計遇到的幾個問題求解

分享:設計仿真技術Cadence PCB介紹

基于MATLAB/Simulink的系統仿真技術與應用

基于設計數據共享的板級熱仿真技術研究(一)

如何對包含數模混合的PCB設計進行合理的控制

恒茂創遠虛擬現實仿真技術的發展及應用特點

我的數模混合設計難點經驗

招兼職candence仿真技術相關專業講師

招兼職candence仿真技術相關專業講師

新的模擬混合信號仿真技術驗證

電子電路計算機仿真技術教材-周常森 pdf下載

通過仿真有效提高數模混合設計性

高速電路--數模混合電路最新PCB創新技術

系統仿真技術與應用

37

37電子電路計算機仿真技術教程

0

0計算機仿真技術及其應用教學大綱

34

34基于DES理論的數模混合電路可測試性研究

28

28如何通過仿真有效提高數模混合設計性

12

12如何通過仿真有效提高數模混合設計性

21

21國內外電網數字仿真技術

31

31基于FPGA的加速原型再現仿真技術

17

17數模混合仿真在以太網芯片設計中的應用

10

10HSDPA仿真技術淺析

449

449Cadence PCB設計仿真技術

4341

4341

混合電路加速仿真

722

722模擬/混合信號仿真器

73

73用于射頻、模擬和混合信號電路設計的新一代仿

28

28混合信號仿真技術綜述

45

45基于仿真技術的LED路燈熱設計

54

54如何通過仿真有效提高數模混合設計性(上)_硬件工程師必讀攻略

0

0仿真技術在模擬電路實驗教學中的應用研究資料免費下載

1

1集成電路 | 電站虛擬仿真技術在高職實踐性教學中的應用

3641

3641高速電路--數模混合電路最新PCB創新技術

966

966模擬仿真技術是什么

15174

15174數模混合電路設計中的難點

3423

3423

VR虛擬仿真技術在各大領域的應用

5211

5211智能制造下仿真技術的作用

3571

3571仿真技術是什么,它的用途有哪些

6772

6772仿真技術如何仿得更真?仿得更快?仿得更全?仿得更易?

2026

2026模擬電路仿真說明

12

12模擬電路仿真導論

12

12模擬集成電路設計與仿真電子版下載

0

0模擬集成電路的基礎知識及仿真技術

26

26仿真技術與數字孿生的關系及未來

1040

10403d虛擬仿真技術在制造業中能夠帶來哪些優勢?

925

925

通過仿真有效提高數模混合設計性能——硬件工程師必讀攻略

1133

1133在飛機設計中的仿真技術

381

381 電子發燒友App

電子發燒友App

評論